Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

21 - 40 / 259

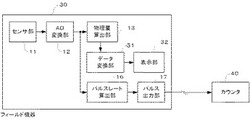

パルス出力型フィールド機器およびそのチェック方法

【課題】パルス信号を出力するフィールド機器のパルス信号が正確に出力されているかをチェックするためには、内部積算値とパルス信号が入力されるカウンタを同期して動作させなければならないので、操作が複雑であり、かつリアルタイムでチェックできなかった。本発明はこのような課題を解決することを目的とする。

【解決手段】物理量に対応する値を基準時間における値に変換し、パルス信号をこの基準時間の間カウントする操作を繰り返して、このカウント値と前記基準時間における値を比較するようにする。簡単な操作でリアルタイムにパルス信号をチェックできる。

(もっと読む)

クロック逓倍回路及び半導体装置

【課題】逓倍されたクロック信号のパルス数が逓倍数の値からずれる状態を原理的に阻止することができるクロック逓倍技術を提供する。

【解決手段】第2クロック信号(CLK2)のサイクル単位で、第1クロック信号(CLK1)の計数値を逓倍数で除した商の値に対応するサンプリングクロックサイクル数を単位として第3クロック信号(CLK3)を順次生成すると共に、生成された一つの逓倍クロックサイクルにおいて前記商の余りに対応する当該サンプリングクロックのサイクル期間に対応して逓倍クロック信号の変化を抑止する制御(106)を行う。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

周波数判定回路および半導体装置

【課題】長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供する。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

動作クロック生成装置、動作回路、及び、画像形成装置

【課題】少なくとも動作クロックの立ち上がりまたは立ち下がりのタイミングが所望のスペクトラム拡散クロックの周波数である動作クロックを生成する動作クロック生成装置、並びに、その動作クロック生成装置を用いた動作回路及び画像形成装置の提供。

【解決手段】基準クロックを計数したカウンタ値の増加に応じて、その基準クロックの立ち上がりタイミングを(A)に示す遅延量tr0〜tr23で遅延補正し、立ち下がりタイミングを(B)に示す遅延量tf0〜tf23で遅延補正した動作クロックを出力する。カウンタ値が1つ増加する間の遅延量trの各増減幅が、EMIを十分に抑制可能な所望の第1スペクトラム拡散クロックにおいて各クロックの立ち上がりタイミングが取る各周波数にそれぞれ相当する値となるように、遅延量tr0〜tr23を設定している。遅延量tf0〜tf23も、所望の第2スペクトラム拡散クロックに応じて設定している。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

デジタル信号処理装置

【課題】フレーム同期式のDSPにおいて、動作クロックの異なる信号処理回路間のデータの受け渡しを簡便に実現する。

【解決手段】各々の動作クロックの異なる複数の信号処理回路のうちから送信側回路と受信側回路を定め、各信号処理回路の動作クロックの全ての立ち上がりエッジが揃うタイミングをデータ受け渡しタイミングとする。送信側回路には、当該送信側回路に与えられるタイミング信号がアクティブレベルであることを条件にデータを出力させる一方、受信側回路には、各動作クロックの周波数の約数を周波数とし、かつデータ受け渡しタイミングを跨ぐ所定期間に亘ってアクティブレベルとなるフレーム同期信号がアクティブレベルであることを条件に、送信側回路から出力されるデータを取り込む処理を実行させる。

(もっと読む)

バイポーラ信号の周波数測定方法および装置

【課題】正パルスおよび負パルス間の位相偏差に影響されることなくバイポーラ信号の周波数を正確に測定する。

【解決手段】バイポーラ信号をB/U変換110した被測定クロックのパルス列の立ち上がりを第1カウンタ120でカウントし、当該カウント値を基に測定期間を設定する。このとき、測定期間の開始および終了のタイミングを決める各パルスの極性が一致するようにしておく。そして、基準クロックに従いカウント動作する第2カウンタ130を上記測定期間で有効にし、該第2カウンタのカウント値を用いて被測定クロックの周波数を算出する。

(もっと読む)

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】回路規模の増大を抑制しつつEMIノイズの低減を図ることができる送信装置を提供する。

【解決手段】送信装置10Aは、送信データ生成部11および出力バッファ部12Aを備える。送信データ生成部11は、受信装置へ送出すべきデータdata1およびクロックclock1を生成し、これらを出力バッファ部12Aへ出力する。出力バッファ部12Aは、データ送信部13およびクロック送信部14Aを含む。クロック送信部14Aは、間欠的に位相シフトを与えられたクロックを生成して送出する。データ送信部13は、クロック送信部14Aにより送出されるクロックに同期してデータを送出する。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

PLL回路、PLL回路の動作方法およびシステム

【課題】 回路規模を増加することなく、PLL回路の精度を向上する。

【解決手段】 時間計測回路は、基準クロックの遷移エッジが現れてから、出力クロックの遷移エッジが2回現れるまでの時間間隔をカウント値として計測する。位相差正規化回路は、計測された時間間隔を出力クロックのクロック数で表される微少位相差に正規化する。また、位相差正規化回路は、PLL回路のロック後に、”1”または”2”を示す微少位相差が連続して現れるときに、”1”と”2”がランダムに現れるまで正規化係数を徐々にずらす。演算回路は、出力クロックの積算値から微少位相差の値を引いた値を、周波数制御語の積算値から差し引いて、基準クロックと出力クロックの位相差を示す位相差信号を生成する。発振回路は、基準クロックと出力クロックの位相を合わせるために、位相差信号に基づいて出力クロック信号の周波数を変更する。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

(もっと読む)

21 - 40 / 259

[ Back to top ]