Fターム[5J039KK25]の内容

Fターム[5J039KK25]に分類される特許

1 - 20 / 37

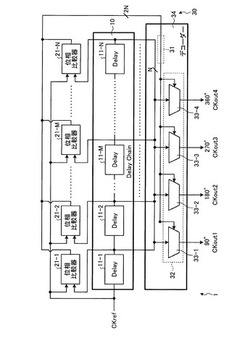

DLL回路、逓倍回路、及び半導体記憶装置

【課題】例えば、遅延クロックの位相と基準クロックの位相とを同期させるためのロック時間を低減する。

【解決手段】1つの実施形態によれば、ディレイチェーン、複数の位相比較器、制御部を有するDLL回路が提供される。ディレイチェーンでは、複数段の遅延素子が直列に接続されている。複数段の遅延素子は、基準クロックに対して互いに異なる遅延量のクロックを発生させる。複数の位相比較器は、基準クロックをそれぞれ受けるとともに、複数段の遅延素子における互いに異なる段の遅延素子からクロックを受ける。制御部は、複数の位相比較器による比較結果に基づいて、複数段の遅延素子のうち基準クロックに対して位相が同期するクロックを発生させる段数を決定する。制御部は、遅延クロックを出力するように、その決定された段数に基づいて複数段の遅延素子における出力段数を選択する。遅延クロックは、基準クロックが要求に応じた遅延量で遅延されたクロックである。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

車載機器用二値信号処理装置

【課題】車両側から車載機器に入力される二値信号の高レベル/低レベルの電位が未知の場合であっても、前記二値信号の2つの状態を正しく弁別し、高レベル及び低レベルの状態に応じてパルス状に変化する出力側二値信号を生成する。

【解決手段】入力側二値信号SG1の波形のアナログレベルをデジタル情報に変換して入力し、このデジタル情報から第1のレベル(高レベル)と第2のレベル(低レベル)とを検出し、前記第1のレベル及び第2のレベルに基づいて少なくとも1つの閾値を決定し、前記閾値に応じて基準レベル生成部の状態を自動的に調整するマイクロコンピュータ11と、前記基準レベル生成部に配置され前記マイクロコンピュータ11からのデジタル制御入力に従って抵抗値が決定される少なくとも1つのデジタルポテンショメータ16、17とを備える。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

PLL回路および電圧制御発振器

【課題】PLL回路のデッドロック状態になることを防止する

【解決手段】閾値判定部13aは、制御電圧の高低を示す制御信号を生成する。制御部13bは、制御信号に応じた制御値を出力し、制御値が発振周波数の上限および下限について最も高い対応関係を示す場合において制御信号が高を示すとき、および制御値が発振周波数の上限および下限について最も低い対応関係を示す場合において制御信号が低を示すときのいずれか一方を満たす際、所定の制御値を出力する。発振器13cは、制御電圧と発振周波数との対応関係が発振周波数の上限および下限が異なるように複数定められていると共に対応関係が複数の制御値と対応付けられており、制御値が示す対応関係における制御電圧に応じた発振周波数を有する出力信号を出力する。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

位相比較装置

【課題】高速動作するBang-Bang型位相比較回路の出力パルスに歪や欠損がある場合であっても、チャージポンプやA/D変換器を用いることなく、進相、遅相のいずれであるかを正確に表すデジタル信号を得る。

【解決手段】Bang-Bang型の位相比較回路10と、該位相比較回路の進相出力パルスおよび遅相出力パルスを入力して遅相/進相の識別を行う位相比較結果識別回路20とを備える。位相比較結果識別回路20は、位相比較回路10の進相出力パルスによってリセットされた後にクロック信号のカウントを行い所定のカウント値に達すると遅相を示す信号を出力する第1カウンタ回路21と、位相比較回路10の遅相出力パルスによってリセットされた後に前記クロック信号のカウントを行い所定のカウント値に達すると進相を示す信号を出力する第2カウンタ回路22と、前記遅相を示す信号と前記進相を示す信号を入力して進相/遅相の識別信号を出力する識別回路23とを具備する。

(もっと読む)

半導体装置

【課題】従来のデューティ検出回路では、キャパシタに対するプリチャージ後の充放電動作が、通常のデューティ検出動作中の充放電動作とは異なるものとなり、正確なデューティ検出ができなかった。

【解決手段】内部クロック信号CLKがハイレベルを取る期間とロウレベルを取る期間との比(デューティ比)を積算し、電気的に記憶する記憶部(キャパシタC1,C2)と、記憶部(キャパシタC1,C2)における積算動作(デューティ検出動作)を制御する積算動作制御回路42と、一端が積算動作制御回路42と接続され、他端が電源線(VDD,GND)に接続された定電流回路(バイアストランジスタBTr1,BTr2)と、積算結果を初期化するプリチャージ回路43とを備え、プリチャージ回路43による初期化の実施中に電流回路(バイアストランジスタBTr1,BTr2)に電流を流すようにする。

(もっと読む)

デューティ補正回路、及びデューティ補正方法

【課題】本発明は、入力信号のデューティ比や周波数、温度、電源電圧、プロセスによらず、出力信号のデューティ比を補正することが出来るデューティ補正回路、及びデューティ補正方法を提供することを課題とする。

【解決手段】コモンモード比較回路13からのフィードバック信号により、レベルシフト回路11はレベルを補正する。またコモンモード比較回路15からのフィードバック信号により、TrTf制御回路12は、信号のエッジの角度を補正する。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

ジッタ測定回路

【課題】周期信号の周期を測定することなくジッタ量をディジタル出力すること。

【解決手段】本発明に係るジッタ測定回路10は、入力される被測定信号5を当該被測定信号のエッジから所定の時間単位である第1の時間で遅延させることによりエッジ間パルス信号6を生成するエッジ間パルス生成部1と、エッジ間パルス信号6を、所定の時間単位である第2の時間を整数倍した値により除算し、該除算演算による剰余結果を剰余結果信号Mとして出力するパルス幅剰余分割部2と、剰余結果信号Mの値が最小となる場合の整数の値を、エッジ間パルス信号6のサイクルジッタ値信号Dとして出力するワンホットステート部4と、を有する。

(もっと読む)

PLL位相合わせ回路

【課題】PLL回路のリファレンスクロックが停止された後に再開された場合、再開後のリファレンスクロックとフィードバッククロックとの位相合わせを短時間で行い、再ロックさせることができるPLL位相合わせ回路を提供する。

【解決手段】PLL位相合わせ回路は、PLL回路と、フィードバッククロックを分周する第1の分周回路と、PLL回路の出力クロックを分周する第2の分周回路と、リファレンスクロックの動作状態を監視するクロックモニタ回路とを備える。第1の分周回路の分周数は、第2の分周回路の分周数と等しく、クロックモニタ回路が、リファレンスクロックが停止されたことを検出すると、第1の分周回路がリセットされてフィードバッククロックが停止され、リファレンスクロックが再開されたことを検出すると、第1の分周回路のリセットが解除されてフィードバッククロックが再開される。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

位相検出回路及びデータ処理装置

【課題】回路構成が簡素化され、低消費電力化され集積回路化する上で有利な構成の回路を得る。

【解決手段】第1クロックが各クロック入力端に与えられる複数段のフリップフロップ回路(Q1−Q7)と、第2クロックが入力される直列接続された複数段の遅延素子(D1−D6)と、前記複数段の遅延素子の出力をそれぞれ、前記複数段のフリップフロップ回路の各データ入力端に与える接続部(L1−L7)と、前記複数段のフリップフロップ回路の出力データが入力され、この出力データ内容に応じて変化する制御信号を得る信号生成回路(163)と、前記信号生成回路からの制御信号に応じて、前記第1若しくは第2クロックを相調整する位相調整信号を出力する位相調整信号出力部(164)を有する。

(もっと読む)

1 - 20 / 37

[ Back to top ]