Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

141 - 160 / 259

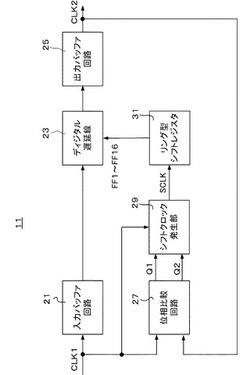

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路においては、品種展開を行う際に追加のフォトマスクが必要となったり、品種の切り替え制御用として専用のボンディングパッドが必要となったりするという課題があった。

【解決手段】クロック入力とデータ入出力とを兼用する少なくとも2個の兼用ボンディングパッド11,12,13と、これらの兼用ボンディングパッドからの入力がクロック信号であるか否かを判定するクロック判定回路14と、このクロック判定回路からの出力に応じて動作する品種を決定する品種選択回路15とを備える。これにより、チップサイズを増加させることなく、また追加のフォトマスクを必要としない半導体製品の品種展開を実現する。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】クロックのデューティ検出において、半導体メモリ装置内のプロセス、電圧レベル、及び温度などによる環境変数の変化によって発生するオフセットを除去するための初期測定動作を行うことができる回路を提供すること。

【解決手段】本発明に係る半導体メモリ装置は、初期測定動作時、共通クロックの遷移時点に対応する2つの検出パルスを生成するクロックエッジ検出部100Bと、前記2つの検出パルスを比較し、その結果を出力するデューティ検出部200Bと、前記初期測定動作時、デューティ検出部200Bから出力された比較結果に基づいて、デューティ検出部200Bを制御するコードカウンタ300とを備える。

(もっと読む)

ノイズ除去回路

【課題】入力信号の“H”,“L”のレベルに拘らず重畳されるパルス性ノイズを除去可能なノイズ除去回路を提供する。

【解決手段】入力信号INが“H”のときに、クロック信号CLKに同期してカウント値CNTをカウントアップさせ、そのカウント値CNTが閾値HTになったときにカウント値CNTを最大値MAXに設定するハイレベル判定部10と、入力信号INが“L”のときに、クロック信号CLKに同期してカウント値CNTをカウントダウンさせ、そのカウント値CNTが閾値LTになったときにカウント値CNTを0に設定するロウレベル判定部20を設ける。更に、カウント値CNTを閾値THと比較し、その比較結果に応じて出力信号OUTを出力する比較器40を設ける。これにより、継続時間が所定のクロック数に満たない入力パルスは除去され、出力信号OUTとして出力されない。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

周波数認識回路及び画像形成装置

【課題】1種類のクロック信号を用いて測定対象となる信号の周波数を認識する。

【解決手段】クロック信号CLKの例えば立ち上がりに同期して、0又は1の信号を交互に出力する。遅延回路320は、100MHzの半周期よりも長く、かつ50MHzの半周期よりも短い予め定められた遅延時間分、カウンタ310から出力される信号S1を遅延させる。EX−OR回路330は、信号S1と信号S2との排他的論理和をとり、信号S3としてラッチ回路340に出力する。ラッチ回路340は、信号S3をラッチして信号S4を出力する。判定部350は、信号S4が1のとき、クロック信号CLKの周波数が100MHzであると判定し、信号S4が0のときクロック信号CLKの周波数が50MHzであると判定する。

(もっと読む)

位相シフト方法および回路

【課題】遅延セルの直列接続段数を大幅に削減すること。

【解決手段】入力信号の立上りのエッジ信号を複数段直列接続の遅延セル16Aの初段に入力し、4段目の遅延セル16Aが反応した後に終段と初段の遅延セル16Aを接続しループ接続し、立上りエッジをカウンタ18Aで所定回数カウントしたときカウンタ18Aからパルスを出力させ、パルスを複数段直列接続の遅延セル19Aの所望段数を経由させてフリップフロップ14のクロックに入力させる。また、入力信号の立下りのエッジ信号を複数段直列接続の遅延セル16Bの初段に入力し、4段目の遅延セル16Bが反応した後に終段と初段の遅延セル16Bを接続しループ接続し、立上りエッジをカウンタ18Bで所定回数カウントしたときカウンタ18Bからパルスを出力させ、パルスを複数段直列接続の遅延セル19Bの所望段数を経由させてフリップフロップ14のリセットに入力させ、信号を出力する。

(もっと読む)

多重系構成における異常発振検出回路

【課題】鉄道保安装置の安全側制御を行うために多重系構成であることを利用し、クロック発振器の高精度な異常発振検出、及び系間相互の状態監視を可能とした回路を提供する。

【解決手段】CPUボードの多重系構成における異常発振検出回路において、自系のカウンタを他系のクロックで動作させ、同様に他系のカウンタを自系のクロックで動作させることにより、相互のクロックの異常発振検出を可能にすることを特徴とする。

(もっと読む)

パルス入力装置

【課題】入力信号の周波数に応じて最適な精度と応答時間を得ることができるパルス入力装置を実現する。

【解決手段】入力信号をパルス信号として検出し、パルス信号の周波数を上位システムへ通知するパルス入力装置に関する。パルス信号の立ち上がりエッジ又は立ち下がりエッジのエッジタイミングでパルス信号のパルス数を所定時間の間カウントし、エッジカウント値として保持するエッジカウント手段と、エッジタイミングで、前回のエッジタイミングとの間隔時間を測定するとともに、所定時間の間の間隔時間を積算し、エッジ間隔値として保持するエッジ間隔測定手段と、エッジカウント値をエッジ間隔値で除してパルス信号の周波数を算出する周波数算出手段とを設けた。

(もっと読む)

信号分析装置

【課題】同一到来時刻間隔の周期信号系列が複数存在しても系列数を正しく推定する信号分析装置を提供する。

【解決手段】複数の放射信号の受信タイミングを示す放射信号の所定タイミング時刻を含む観測データに基づき放射信号の周期信号の系列数と到来時刻間隔を推定するために、放射信号到来時刻間隔の分析範囲、これを複数の評価値細分区間とカウント値細分区間に分割したそれぞれの幅や個数を設定(6)、前記所定タイミング時刻から放射信号の到来時刻差分を計算(1)、到来時刻差分から対応する評価値細分区間とカウント値細分区間を選出(2)、到来時刻差分と前記所定タイミング時刻から評価値を算出しまた評価値細分区間毎に累積して累積評価値を算出(3)、選出細分区間で選出された到来時刻差分数をカウント値細分区間毎に数えカウント値を算出(4)、累積評価値とカウント値から周期的な放射信号の系列数と到来時刻間隔を推定(5)する。

(もっと読む)

タイミング発生回路

【課題】

周期が一定であるかまたは変化し、一周期の間に少なくとも2つのレベルで遷移する処理対象信号の当該レベル遷移のタイミングを細かく設定できる回路技術を提供する。

【解決手段】

(A)第1周期信号、第2周期信号、・・・、第M周期信号をそれぞれ出力する周期信号発生回路11と、(B)第1〜第M周期信号を計数する第1〜第M計数回路からなる計数回路群12と、(C)前記所定タイミングの値を時間軸で配分して、前記所定タイミングの時間軸で配分した値を、第1周期信号の周期個数N1、第2周期信号の周期個数N2、・・・、第M周期信号の周期個数NMで表し、第1周期信号の周期個数N1を前記第1計数回路に、

第2周期信号の周期個数N2を前記第2計数回路に、

・・・

第M周期信号の周期個数NMを前記第M計数回路に、

セットする設定装置13とを備える。

(もっと読む)

複数の発振回路を備える電子回路

【課題】メイン回路とサブ回路に独立して別々にクロック発振回路を設ける回路構成としながら、サブ回路に設けているサブクロック発振回路の周波数のずれを極めて簡単な回路構成で検出する。

【解決手段】複数の発振回路を備える電子回路は、主クロック発振回路10を備えるメイン回路1と、このメイン回路1に信号伝送回路3を介して接続してなるサブクロック発振回路20を備えるサブ回路2とを備える。メイン回路1は、サブクロック発振回路20の発振周波数のずれを検出する周波数検出回路11を備える。サブ回路2は、サブクロック発振回路20の出力パルスをカウントするカウンター24を備える。メイン回路1の周波数検出回路11は、サブ回路2のカウンター24のカウント値を検出してサブクロック発振回路20の周波数のずれを検出する。

(もっと読む)

アナログ信号比較器

【課題】

アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】

第1のパルス信号を生成する発振器21Aと、アナログ信号を入力し当該アナログ入力信号を第2のパルス信号に変換して出力するVCO22と、発振器21からの第1のパルス信号を入力する第1のシフトレジスタ241と、VCO22からの第2のパルス信号を入力する第2のシフトレジスタ242と、第1および第2のシフトレジスタ241,242の全ビットまたは一部ビットの値を検出し、これらの検出値に基づき、発振器21Aが生成する第1のパルス信号の個数と、VCO22が生成する第2のパルス信号の個数とを比較するパルス個数比較回路とを備えたことを特徴とするアナログ信号比較器。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

半導体集積回路装置及びデューティ制御方法

【課題】動作速度を向上出来る半導体集積回路装置及びデューティ制御方法を提供すること。

【解決手段】第1クロックCLK1に同期して動作し、該第1クロックCLK1が“H”レベルでアクティブとなる第1クリティカルパス12と、“L”レベルでアクティブとなる第2クリティカルパス13とを含むプロセッサコア2と、第2クロックCLK2のデューティを制御して前記第1クロックCLK1を生成する第1クロック生成部3と、前記第1クロックCLK1と、前記第1クリティカルパス12で生じる遅延時間Δtd1だけ遅れた第3クロックCLK3との第1位相差UPと、前記第1クロックCLK1と、前記第2クリティカルパス13で生じる遅延時間Δtd2だけ遅れた第4クロックCLK4との第2位相差DNとが最小となるように前記デューティを制御するよう、前記第1クロック生成部3に命令する制御部4とを具備する。

(もっと読む)

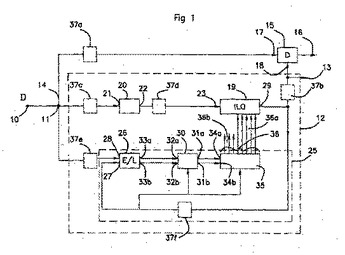

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

測定量を測定するためのホイール電子回路およびタイヤ監視システム

【課題】本発明は、タイヤ監視システムにおいて、測定すべき測定量の測定に及ぼされる妨害パルスおよび/または信号ノッチの影響を少なくとも低減するという課題を基礎とする。

【解決手段】車両のタイヤ監視システム内または車両のタイヤ監視システム用に設けられ、変調された搬送波信号から包絡線を検出することによって、搬送波周波数を有する受信された振幅変調問い合わせ信号を復号化するための評価装置と、該問い合わせ信号を入力結合するためのカウンタ入力側を有するデジタルカウンタと、入力側で該デジタルカウンタのカウンタ出力側に接続されているシフトレジスタと、該シフトレジスタの出力側に接続された論理回路とを有する、ホイール電子回路。

(もっと読む)

位相差計測回路

【課題】2つの信号の進み遅れに関係なく、遷移タイミングの差を測定することができる位相差計測回路を提供する。

【解決手段】EXOR11により、デジタル信号S1,S2の位相差に対応したパルス幅の信号S3が出力される。信号S3は、インバータ12で反転された信号S4と共にセレクタ13に与えられ、選択信号SELに従っていずれか一方が選択され、ゲート制御用の信号S5としてADN14に与えられる。AND14には連続したクロック信号CLKが与えられており、信号S5でゲート制御されたクロック信号CLKが、信号S6としてカウンタ15に与えられる。カウンタ15は、信号S6のパルス数をカウントし、カウント値CNTを出力する。選択信号で信号S3,S4を選択することにより、デジタル信号S1,S2の進み遅れに関係なく、遷移タイミングの差を測定できる。

(もっと読む)

クロック監視回路及びルビジウム原子発振器

【課題】互いに相手のクロックを監視することができるようにして、簡単な回路構成で確

実にクロック停止を監視することができるクロック監視回路を提供する。

【解決手段】このクロック監視回路60は、異なる発振源から発振された2つのクロック

CLK−A、CLK−Bの何れか1つのクロックが停止したことを検出するクロック監視

回路であって、各発振源から発振された夫々のクロックCLK−A、CLK−Bを計数す

るカウンタA、カウンタBと、各カウンタA、Bが所定の計数値を計数したことを検出す

る検出回路A、検出回路Bと、を備え、夫々のカウンタA、Bをリセットするリセット端

子Rには、当該カウンタを歩進させるクロック以外のクロックを接続するものである。例

えば、カウンタAのリセット端子Rには、CLK−Bを接続し、カウンタBのリセット端

子Rには、CLK−Aを接続する。

(もっと読む)

141 - 160 / 259

[ Back to top ]