Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

61 - 80 / 259

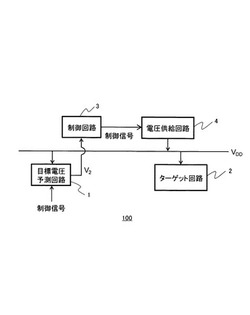

半導体集積回路装置、及び電源電圧制御方法

【課題】短時間に電源電圧を最適値に制御することが可能な半導体集積回路装置を提供することである。

【解決手段】本発明にかかる半導体集積回路装置100は、ターゲット回路2と、ターゲット回路2に電源電圧を供給する電圧供給回路4と、電圧供給回路4の出力電圧を制御する制御回路3と、ターゲット回路2に供給される電源電圧の電圧値を予測する目標電圧予測回路1とを備える。制御回路は、ターゲット回路2の要求動作周波数が第1の動作周波数から第2の動作周波数に変化した際に、電圧供給回路4の出力電圧を所定の電圧値だけ変化させる。目標電圧予測回路1は、所定の電圧値の変化にともなうターゲット回路2の動作周波数の変化量を検出すると共に、動作周波数の変化量と所定の電圧値との関係に基づいて目標電圧値を算出する。電圧供給回路4は、ターゲット回路2に目標電圧値の電源電圧を供給する。

(もっと読む)

パラレル−シリアル変換器及びパラレルデータ出力器

【課題】パラレル−シリアル変換器において、データ信号をラッチするフリップフリップ(FF)に供給されるクロック信号の位相ずれを調整する。

【解決手段】FF1−1〜1−5によるデータ信号D0,D1を選択回路2で選択出力したデータ信号D[0+1]をFF4によりラッチ出力するパラレル−シリアル変換器において、レプリカのデータ信号repIN0,repIN1を選択回路10で選択出力したデータ信号repDをラッチしたFF11によるデータ信号repOUTに基づき位相ずれ検出回路12,13が生成する位相調整指示値信号に従い、分周回路3による分周クロック信号の位相を調整してクロック信号divCLKを発生する任意位相生成回路15を備えると共に、クロック信号ffCLKとrepCLKとを位相比較し、クロック信号repCLKを移相させる位相設定回路16,17を備える。

(もっと読む)

スペクトラム拡散クロックの周波数レベル検出方法及びスペクトラム拡散クロックの周波数レベル検出装置

【課題】一定の変調周期で周波数が複数の周波数レベルに亘って変調されたスペクトラム拡散クロックに対して、そのスペクトラム拡散クロックの上記周波数レベルを検出することのできるスペクトラム拡散クロックの周波数レベル検出方法及びスペクトラム拡散クロックの周波数レベル検出装置の提供。

【解決手段】パルス発生回路48は、基準クロックの計数値と設定レジスタ46に記憶された値とを比較することで一定期間毎にパルスを発生する。その一定期間にスペクトラム拡散クロックSSC_CLKを計数して得られたSSCカウント値をカウンタバッファ51に保持して、設定レジスタ53に記憶された各種閾値と比較回路55を介して比較することにより、その時点におけるスペクトラム拡散クロックSSC_CLKの周波数レベルを検知することができる。

(もっと読む)

精密三角波形生成器

【課題】三角波形の品質をさらに正確に制御するためのシステムおよび方法を提供すること。

【解決手段】三角波形生成器は、容量素子、調整器、および制御回路を含むものとして規定される。調整器は、第1の制御信号に応答して容量素子を充電し、第2の制御信号に応答して容量素子を放電するように構成される。制御回路は、基準波形に応答し、第1および第2の制御信号を生成する。一例において、制御回路は、基準波形の振幅、周波数、位相、および対称性に応答して、第1および第2の制御信号を生成する。

(もっと読む)

半導体集積回路及び半導体集積回路の発振異常検出方法

【課題】オシレータ出力、又はPLL出力、又はリングオシレータ出力のいずれかに発振異常が発生しているか否かを判定できる半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路1は、第1の発振器(オシレータ2)と、第2の発振器(PLL3)と、第3の発振器(リングオシレータ4)と、第1の発振器2のクロック、第2の発振器3のクロックを第3の発振器4のクロックに基づいて順に切り替えて出力するセレクタ6と、セレクタ6から出力されたクロックを、第3の発振器4のクロックに基づいてアップカウント又はダウンカウントし、アップカウント又はダウンカウントの結果に基づいて、セレクタ6から出力されたクロックと、第3の発振器4のクロックとの整合性を判定し、いずれかのクロックに発振異常が発生しているか否かを判定する判定回路7と、を備える。

(もっと読む)

スペクトラム拡散クロック生成装置

【課題】生成されたスペクトラム拡散クロックを、各種タイミングを制御するカウンタのクロックとしても用いることのできるスペクトラム拡散クロック生成装置の提供。

【解決手段】SSC源クロック発生回路3,基準クロック発生回路5が発生するSSC源クロック,基準クロックは、16bitカウンタ7,9に入力されて、そのクロック数がカウンタ値cnt1,cnt2として計数される。カウンタ値cnt1,cnt2は、比較回路10に入力され、カウンタ値cnt1がカウンタ値cnt2よりも1以上大きくなると、比較回路10は比較結果cmpとしてLレベルの信号を出力する。すると、パルス生成回路21がLレベルの矩形パルス(間引き要求pls_cg)を出力し、AND回路31によりその間引き要求pls_cgとSSC源クロックとの論理積が計算されることによって、SSC源クロックが1クロック分間引かれる。

(もっと読む)

スイッチングドライバ回路

【課題】ディスクリート部品を用いることなく、パルス時間が長く、しかも、電圧変動が大きいノイズを確実に除去可能とする。

【解決手段】

入力信号の立ち上がり、立ち下がりを検出し、エッジ検出信号を出力するエッジ検出回路101と、入力信号を所定シフト時間t1シフトして出力するシフトレジスタ回路106と、エッジ検出回路101のエッジ検出信号の入力時点から所定入力時間t2経過後にカウントアップ信号を出力するカウンタ回路102と、シフトレジスタ回路106の出力信号を、カウンタ回路102のカウントアップ信号に同期して出力するDFF回路103と、DFF回路103の出力信号を外部へ出力する出力回路104と、シフトレジスタ回路106とカウンタ回路101のクロック信号を生成、出力する発振回路105とを具備してなり、所定入力時間t2に満たない入力信号が出力されないようになっている。

(もっと読む)

ノイズキャンセラおよび画像形成装置

【課題】 異なる時間レンジにおける信号レベルおよび信号レベルの変化を同時に出力し、ノイズ周波数が状況に応じて変わる場合にも、ノイズキャンセルを効果的に行うことができるようにする。

【解決手段】 N進カウンタ群1は、N進カウンタ1−1〜1−Mを有し、各N進カウンタ1−iは、クロック信号を印加され、そのクロック信号の周期を増加させて出力する。また、レベル変化検知器群3は、レベル変化検知器3−1〜3−Mを有し、各レベル変化検知器3−iは、N進カウンタ1−iから出力される第1クロック信号Giの1周期ごとに入力信号Lei−1のレベルをサンプリングしサンプリング信号Leiを出力するとともに、第1クロック信号より周期の短い第2クロック信号Gi−1の1周期ごとに入力信号Lei−1のレベルを検出してレベル変化の有無を示すレベル変化状態信号Chiを出力する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

ディジタル・ノイズフィルタと方法

【課題】さまざまな信号のノイズ状態に対応可能とし、回路規模の縮小を実現するディジタル・ノイズフィルタの提供。

【解決手段】前状態取込み間隔設定値で時間間隔を調整でき、該時間間隔でタイミングを出力するタイミング生成回路6と、タイミング生成回路6からタイミング信号が出力される毎に、外部入力信号を取り込む前状態保持FF1と、前状態保持FF1が保持している状態と現在の外部入力信号状態の一致比較を行う状態比較器2と、タイミング生成回路6が出力するタイミング毎に状態比較器2で一致した回数をカウントする一致数カウンタ3と、カウンタ・リミット設定値と一致数カウンタ3のカウンタ値が一致またはそれ以上の場合に一致信号を出力する一致数比較器4と、一致数比較器4の出力によって前状態保持FF1の出力を取り込む読み出し用FF5を備える。

(もっと読む)

周波数の即時調整が可能な節電型トリガー制御装置、および、その方法

【課題】周波数の即時調整が可能な節電型トリガー制御装置及びその方法を提供する。

【解決手段】本発明に係る装置は、少なくとも2つの信号入力端を有する信号制御ユニットと、計数制御ユニットと、クロック生成器と、からなる。2つの信号入力端はそれぞれ、トリガー回数を受信し、その後対応する回数の周波数逓増トリガー信号又は周波数逓減トリガー信号を生成する。計数制御ユニットにより受信した周波数逓増トリガー信号及び周波数逓減トリガー信号を計数する。クロック生成器により計数した周波数逓増トリガー信号又は周波数逓減トリガー信号の回数に基づき、出力周波数を線形逓増又は逓減する。本発明の装置は更に、電源コントローラーを有し、出力電圧を調整する。本発明は、システムのいかなる状態下でも、外部の制御により即時にシステムの周波数/電圧を線形調整でき、節電目的が達成される。

(もっと読む)

遅延比較回路、遅延比較方法、遅延回路および半導体集積回路

【課題】複数の遅延回路における遅延差(位相差)を高精度で比較することができる遅延比較回路の提供を図る。

【解決手段】複数のディレイライン1,2と、該各ディレイラインをそれぞれオシレータ化する複数のオシレータ補助回路6,8;7,9と、オシレータ化された前記各ディレイラインの発振出力をカウントしてそれぞれカウント値を求める複数のカウンタ3,4と、前記各カウント値を基準カウント値と比較する比較部5と、を有するように構成する。

(もっと読む)

クロック検出方法及びその装置

【課題】既存のクロック検出方法のリソース占用率が高い問題を解決できるクロック検出方法及びその装置を提供する。

【解決手段】該方法は、プログラマブル部品が、ローカルタイムソースにより生成されたソースクロック信号に周波数分割を行って参照クロック信号を取得し(S101)、プログラマブル部品が、ソースクロック信号をカウント動作クロックとし、検出対象クロック信号の、参照クロック信号の連続するN(Nは正整数である)個のハイ電圧レベルの各ハイ電圧レベル期間における立ち上がりエッジカウント値とハイ電圧レベルカウント値を確定し(S102)、プログラマブル部品が、検出対象クロック信号の、各ハイ電圧レベル期間におけるハイ電圧レベルカウント値と第1の所定値との大きさ関係、及び立ち上がりエッジカウント値と第2の所定値との大きさ関係に基づいて、検出対象クロック信号が有効であるかを確定する(S103)。本発明によると、少ないリソースを占め、クロック検出の信頼性が向上でき、また、検出対象クロック信号の周波数範囲が広くなり、検出対象クロック信号の高周波数グリッチによる影響を避けることができる。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路において、電源電圧が変動した場合のオフセットを抑制する。

【解決手段】レベルシフト回路1は、差動増幅回路10、電流発生回路11、コンデンサ12、保持回路13を備える。差動増幅回路10の非反転入力端子(+)に光ピックアップ2からの入力信号Vinが印加される。先ず、第1のスイッチ14aをオンすることにより、差動増幅回路10、電流発生回路11、コンデンサ12によりフィードバックループを形成してレベルシフトを行い、コンデンサ12に充電された電圧を保持回路13で保持する。その後、第1のスイッチ14aをオフし、第1のスイッチ14bをオンすることにより、保持回路13によって保持された電圧を差動増幅回路10の非反転入力端子(+)に印加してレベルシフトを行う。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

マイクロコンピュータ

【課題】外部発振機能で発生したクロックの発振周波数の異常を確認することができるマイクロコンピュータを提供すること。

【解決手段】本発明の一態様に係るマイクロコンピュータは、発振回路101、サンプリング回路103、サンプリングクロック回路106、異常確認回路107を備える。発振回路101は、CPUのクロック周波数の第1クロックを固定振動子により発生させる。サンプリングクロック回路106は、第1クロックより低い周波数の第2クロックを出力する。サンプリング回路103は、第2クロックを用いて第1クロックの周期をカウントし、第1クロックの発振が安定したか否かを判定し、CPUクロック供給許可信号を出力する。異常確認回路107は、第2クロックの周期をカウントすることにより決定される所定の期間内において、第1クロックの発振異常が発生したか否かを判定する。

(もっと読む)

火災感知器および火災報知設備

【課題】クロックパルス周波数の誤差が±200%になっても、正確な時間で火災検出等の動作を行えることができる火災報知設備を提供することを目的とするものである。

【解決手段】火災報知設備の火災感知器において、中継器または火災受信機との間で伝送を行う際に、上記中継器または上記火災受信機が、時間間隔の基準となるパルスを定期的に上記火災感知器に伝送する火災感知器であって、上記基準となるパルスを、上記火災感知器が受信し、この受信したパルスの長さを、上記火災感知器が自ら発生するクロックパルスの長さと比較することによって、上記クロックパルスの周波数の誤差範囲を修正する火災感知器である。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

61 - 80 / 259

[ Back to top ]