Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

81 - 100 / 259

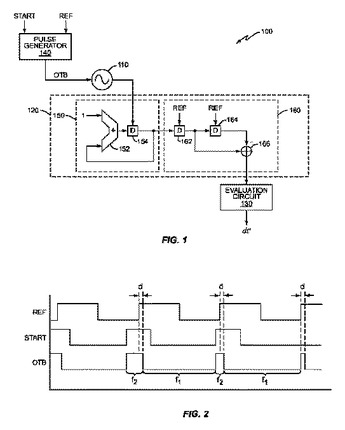

改善された分解能を有する時間デジタル変換器(TDC:TIME−TO−DIGITALCONVERTER)

【解決手段】一つのインバータ遅延より小さいインバータ遅延の高分解能を含む時間デジタル変換器(TDC)が記載されている。デザイン例において、TDCは、第1及び第2の遅延パス、遅延ユニット、及び位相演算ユニットを含んでいる。第1の遅延パスは、第1の入力信号及び第1の参照信号を受信し、第1の出力を供給する。第2の遅延パスは、第2の入力信号及び第2の参照信号を受信し、第2の出力を供給する。遅延ユニットは、例えば半分のインバータ遅延によって、第1の入力信号に対して第2の入力信号を遅延する、または第1の参照信号に対して第2の参照信号を遅延する。位相演算ユニットは、第1及び第2の出力を受信し、入力信号及び参照信号間の位相差を供給する。構成は、前記第1及び第2の遅延パスについての正確なタイミングを得るために実行され得る。 (もっと読む)

クロックスキュー自動調整回路及びその調整方法

【課題】従来のクロックスキュー調整回路では、精度の高いクロックスキュー調整を行うことができないという問題があった。

【解決手段】本発明にかかるクロックスキュー自動調整回路は、クロックのドライブ能力を調整するクロックドライバ101と、クロックの信号変化開始から信号変化終了までに要する時間を計測する計測回路102と、前記計測時間と予め設定された基準時間とに基づいて制御信号を生成し、前記クロックドライバに対して出力する制御回路103と、を備える。このような回路構成により、精度の高いクロックスキュー調整を行うことができる。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

信号レベル変換回路および位相同期回路

【課題】信号レベル変換回路の上限動作周波数を向上させる。

【解決手段】クロック信号をゲート(G)電極に受ける第1MOSトランジスタ(MOS−Tr)と,ドレイン(D)電極を第1MOS−TrのD電極に接続される第2MOS−Trと,逆相のクロック信号をG電極に受ける第3MOS−Trと,G電極およびD電極を第2MOS−TrのG電極と第3MOS−TrのD電極に接続された第4MOS−Trと,第1および第2MOS−TrのD電極から取り出した信号を受けるインバータ回路により構成されたレベル変換回路において,第2MOS−Trのソース電極と電源の間,または,第4MOS−Trのソース電極と電源の間の少なくとも一方に,並列に接続した複数の第5MOS−Trを設け,インバータ回路の出力の平均電圧が低電位側の電源と高電位側の電源の中間の電圧になるように第5MOS−Trの導通及び遮断を制御する制御回路を設ける。

(もっと読む)

ジッタ低減回路および半導体集積回路

【課題】クロック信号に乗るジッタを低減することが可能なジッタ低減回路および半導体集積回路の提供を図る。

【解決手段】第1クロック信号CLK1の第1周波数を測定する第1周波数測定回路11と、第2クロック信号CLK2の第2周波数を測定する第2周波数測定回路12と、測定された前記第1および第2周波数を比較し、該第1および第2周波数が所定の関係に有るかどうかを判定する周波数比較判定回路20と、前記周波数比較判定回路からの第1制御信号CNT1を受け取り、前記第1クロック信号の遅延を制御して前記第2クロック信号によるジッタを低減する第1遅延制御回路41と、を有するように構成する。

(もっと読む)

データ送受信方法

【課題】同期式連続データ伝送の信頼性を確保すると共に容易に設計することができるデータ送受信方法を提供する。

【解決手段】データ送信装置11は、通信開始時にテストデータをデータ受信装置12に送信する。データ受信装置12は、システムクロックを数倍に逓倍した内部クロックによりテストデータをサンプリングしてキャプチャ回路23に取り込み、データ取り込みタイミング制御部24において上記取り込みデータから最適のデータ取り込みタイミングを選択して設定する。データ受信装置12は、通常のデータを取り込む際は、データ取り込みタイミング制御部24において設定された最適のデータ取り込みタイミングにて受信データの取り込みを行う。

(もっと読む)

信号発生装置

【課題】

積分回路や発振回路に、時間差なく各信号が入力され、さらには、積分回路や発振回路の補正や校正の自由度を高くする。

【解決手段】

複数のアナログ信号を入力し当該アナログ信号をそれぞれ積分した積分信号をそれぞれ出力する積分回路111,112と、各積分信号をそれぞれ入力し、積分信号の大きさを所定のしきい値と比較して比較信号をそれぞれ出力する比較回路121,122と、積分回路のうち少なくとも2つの積分回路の制御端子に接続され、それぞれセットされた時間だけ、他の少なくとも1つの積分回路の積分動作の開始タイミングと異なるタイミングで積分動作を開始させる遅延回路131,132と、比較信号を入力し、これらの入力信号の入力タイミングを比較し、これらの入力タイミングに応じた比較結果信号を出力する信号処理回路14とを備える。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

演算回路

【課題】 低消費電力化が図られた演算回路を提供することを目的とする。

【解決手段】 第2の電源分離領域12に対応して設けられた第2の電力制御回路22が、第2の電源分離領域12よりも一段だけ前段の第1の電源分離領域11での情報パケットAの処理の開始時点で、第2の電源分離領域12への電力供給を開始するとともに、第2の電源分離領域12での情報パケットBの処理の終了時点で第2の電源分離領域12への供給電力を遮断する。

(もっと読む)

クロック分周回路、及びクロック分周方法

【課題】動作回路の通信タイミングを考慮すると共に、分周時に出力クロック信号の位相調整が可能なクロック分周回路、及びクロック分周方法を提供することである。

【解決手段】本発明にかかるクロック分周回路100は、入力クロック信号(クロックS)のクロックパルスと、通信タイミング信号26と、位相調整信号60に応じて生成されたリセット値81と、に基づき、入力クロック信号に対する通信タイミングの相対的な位相を示すカウント値55を生成し、カウント値55に基づき入力クロック信号のM個のクロックパルスのうち通信タイミング以外のクロックパルスに対してクロックパルスをマスクするマスク信号25を生成するマスク制御回路20を有する。更に、マスク信号25に応じて入力クロック信号のクロックパルスをマスクするマスク回路10を有する。

(もっと読む)

受信回路

【課題】消費電力を低減し誤動作の少ない受信回路を提供する。

【解決手段】プリアンブルを含む変調されたディジタル信号を受信する受信装置210と、検波回路220によるベースバンド信号S1と基準信号Vrefを比較するコンパレータ250と、ベースバンド信号S1の積分回路240と、積分回路240からの平均値信号S2に基づく信号S3を生成する下側ヒステリシス電圧生成回路260と、平均値信号S2に基づく信号S4/S5を生成する上側ヒステリシス電圧生成回路270と、コンパレータ250からのディジタル信号Doutに基づき、信号S3または信号S4/S5を選択しこれを基準信号Vrefとする選択回路280と、コンパレータ250からのディジタル信号のパルス数を計数し信号Qを出力するパルス検出カウンタ290と、信号Qに基づく信号S4/S5の電圧レベルを可変する電圧と、信号を処理するディジタル回路とを有する。

(もっと読む)

自走発振器のロックを検出するシステム及び方法

【課題】 自走発振器のロックを検出するシステム及び方法を提供することである。

【解決手段】 FROサンプラー110の出力がサンプルストレージメディア120の入力にカップリングされ、パターン検出ロジックが、サンプルストレージメディアを1つ以上のパターン検出器130に作動上カップリングしてサンプルにアクセスし又はサンプルを入手する。パターン検出器が、保存サンプル1〜Nを、保存サンプル(N+1)〜2Nと比較してその等値性を調べ、サンプル1と4が同値を含み、サンプル2と5が同値を含み、サンプル3と6が同値を含むことを発見すると、サンプル1、2、3がサンプル4、5、6と同じパターンの反復であると見なされる。

(もっと読む)

チャタリング除去装置

【課題】 簡単な構成で製造コストを抑制することができるチャタリング除去装置を提供する。

【解決手段】 テンポラリレジスタR2に記憶している前回のシフトレジスタ値のMSBが1であるか否かを判定する。前回のシフトレジスタ値のMSBが1の場合は(S13;Yes)、カウンタC1を1だけインクリメントする(S14)。カウンタC2を1だけインクリメントし(S16)、テンポラリレジスタR2のシフトレジスタ値を1ビット左シフトする(S17)。カウンタC1のカウント値がチャタリング除去閾値N(例えば4)、つまり、最新のシフトレジスタ値における「1」の連続数が4であるか否かを判定する。カウンタC1のカウント値が4である場合は(S18;Yes)、タッチセンサ75がONしたと判定する。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

2相カウンタおよびカウンタシステム

【課題】カウント動作を高速でも容易に行えるようにすること。

【解決手段】A相パルスの前パルスエッジとB相パルスの前パルスエッジとのエッジ位相差と、A相パルスの後パルスエッジとB相パルスの前パルスエッジとのエッジ位相差とを検出し、上記両エッジ位相差の比率を演算し、上記エッジ位相差比率に対応して割り当てられたカウント値を演算する2相カウンタ。

(もっと読む)

プログラマブルデュアルエッジトリガードカウンター

【課題】出力クロック信号のジッターを低減し、デューティサイクル分解能を改善するための回路の提供。

【解決手段】最小のジッターを備えたクロック信号を合成するためのカウンターは、出力クロックの立ち上がりエッジを入力クロック信号の立ち上がりエッジまたは立ち下がりエッジによりトリガーしなければならないかどうかを決定するために、さらに、出力クロックの立ち下りは、入力クロック信号の立ち下りの立ち上がりエッジまたは立ち下りによりトリガーしなければならないかどうかを決定するために進行中のカウントを分析する。カウンターはM/N:Dカウンターとして実施してもよい。このカウンターにおいて、位相アキュムレーターは所定の値と比較され、出力クロック信号の立ち上がりエッジおよび立ち下りを選択する。

(もっと読む)

ノイズシェーピング時間測定回路

時間測定回路のある実施形態では、リファレンス信号期間の第1の部分においてデジタル制御発振器(DCO)を第1の周波数で動作させ、前記対象信号と前記リファレンス信号との時間差に応じて前記リファレンス信号期間中に動作周波数を前記第1の周波数から第2の周波数に変更することにより、対象信号とリファレンス信号の時間差が測定される。時間測定回路は、前記リファレンス信号期間において前記デジタル制御発振器の出力で何回の信号遷移が発生したかを継続的に計数する。対象信号とリファレンス信号の時間差は、前記リファレンス信号期間において計数された前記信号遷移の回数に基づいて推定される。

(もっと読む)

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

モード設定回路及びそれを用いたカウンタ回路

【課題】本発明は多種の時短モード設定が可能なモード設定回路及びそれを用いたカウンタ回路を提供することを目的とする。

【解決手段】外部から供給されるパルス信号によりトリガされる縦続接続された複数段のフリップフロップ13,14と、複数段のフリップフロップそれぞれの出力信号を演算して複数種類のモード信号を生成する論理回路15〜19とを有する。

(もっと読む)

81 - 100 / 259

[ Back to top ]