Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

101 - 120 / 259

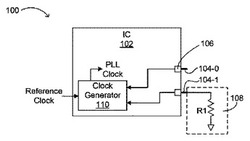

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

低電力非同期カウンタ及び方法

【解決手段】低電力非同期カウンタの設計技術。典型的な実施形態では、複数のフリップフロップのクロック入力及び信号出力が、非同期カウント構造を実現するように直列に連結される。複数のフリップフロップの信号出力は、参照信号の順次遅延されたバージョンによってサンプリングされる。更に、参照信号の順次遅延されたバージョンを生成する設計方法が開示される。典型的な実施形態では、非同期カウント技術は、デジタル位相ロックループ(DPLL)の高速カウンタに使用され得る。 (もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

2値化回路と位相差判別装置

【課題】 入力電圧を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と第1出力端子26と第2出力端子28とピークホールド回路30とボトムホールド回路40と閾値演算回路50と第1比較回路60と第2比較回路70と第1選択回路80と第2選択回路90と第3選択回路100と第4選択回路110を備えている。第1選択回路80は2値化信号を出力し、第2選択回路90は遅れ2値化信号を出力する。ピークホールド回路30は遅れ2値化信号に基づいてピーク電圧を減少させ、ボトムホールド回路40は遅れ2値化信号に基づいてボトム電圧を増加させる。そのため、遅れ2値化信号を2値化信号に対して確実に遅延させることが可能となる。

(もっと読む)

クロック信号出力回路及びクロック信号出力回路の発振動作方法

【課題】外部発振子を用いずとも、継続して逓倍クロック信号を生成出力できるクロック信号出力回路を提供する。

【解決手段】記憶用メモリ12に、基準クロック信号PREFの周期をリングオシレータ1及び周期カウンタ5によりカウントしたデータを記憶させ、クロック信号出力回路11は、セレクタ13を介すことで、除算器7及びシステムクロック生成部9が記憶用メモリ12に記憶させたデータに基づいて演算処理を行い、逓倍クロック信号を生成して出力する。したがって、外部発振子3を発振動作させて基準クロック信号を常時得る必要がなくなる。

(もっと読む)

ノイズ除去回路および方法

【課題】デジタルデバイスに入力される周期的パルス信号の一周期にわたってノイズパルスを除去することができるノイズ除去回路および方法を提供する。

【解決手段】周期的パルス信号からノイズパルスを除去するノイズ除去回路は、固定高レベルを入力とし、周期的パルス信号aおよびリセット信号dに従って高レベルと低レベルとの間で回路出力を変化させるフリップフロップ回路10と、周期的パルス信号aのレベルが変化してから一周期内で次にレベル変化するまでは固定高レベルの入力により、それ以後はリセット信号dによりフリップフロップ回路の出力を固定するリセット制御部20と、を有する。

(もっと読む)

パルスレート変換器

【課題】 大容量メモリを使用せずとも均等化されたパルスを出力し得るパルスレート変換器を提供する。

【解決手段】 入力パルスのパルス数に対してパルスレート設定値に対応した出力パルスを送信するパルスレート変換器において、

前記入力パルスのパルス数を保持する入力パルス数レジスタと、

前記出力パルスのパルス数を保持する出力パルス数レジスタと、

(前記出力パルスのパルス数)/(前記入力パルスのパルス数)と前記パルスレート設定値を比較し、前記出力パルスを出力するかしないか決定する制御回路と

を備える。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

自動クロック切替回路および方法、ならびに電子機器

【課題】入力されたクロックが適切なものであるか常時監視することができ、クロックの切り替えを常時適切に行うことができるようにする。

【解決手段】判定回路10に固定クロックCLK1を常時入力する。判定回路10では、その常時入力される固定クロックCLK1に基づいて対象クロックCLK2の状態を監視し、対象クロックCLK2が入力停止状態にあるか、もしくは対象クロックCLK2の周波数が所定の周波数の範囲外にあるか否かを判断する。固定クロックCLK1を常時入力としているため、常にクロックの判定を行うことが可能であり、固定クロックCLK1から対象クロックCLK2へ、または対象クロックCLK2から固定クロックCLK1への切り替えが常時可能となる。また、対象クロックCLK2の入力停止状態から所望とするクロックの周波数範囲の判定まで、切れ目のない判定が可能となる。

(もっと読む)

位相検出装置、位相検出方法、再生装置及び再生方法

【課題】

記録媒体から再生される再生信号とクロック信号との位相差を正確に検出することが可能な位相検出装置、位相検出方法、該位相検出装置を備えた再生装置、再生方法を提供する。

【解決手段】

位相同期回路39がリミット位相ディテクタ41を備えるので、例えば図4に示すゼロクロスのタイミング(C)が検出されたとき(ST605でYES)、クロックカウンタ47によるカウント値と所定の値とを比較し(ST606)、カウント値が所定の値より小さいときに(ST606でNO)Cから次のクロックの立ち上がりまでの間、位相カウンタ51をイネブルでない状態とすることができる。つまり、リミット位相ディテクタ41(の位相カウンタ51)の出力を無効にすることができる。この結果、例えばノイズ等の影響を受け易い所定カウント値より小さいパルス幅のRF信号(入力信号)に基づき位相エラー信号が求められることを防止することができる。

(もっと読む)

セットアップ/ホールドタイム測定装置

【課題】テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供する。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

(もっと読む)

周波数変換器

【課題】小数点を含んだ自由な変換関係を選択することができる周波数変換器を提供すること。

【解決手段】逓倍器を用いて入力パルス列信号を予め設定した逓倍数Nで逓倍して逓倍パルス列信号に変換する。次に、逓倍パルス列信号を分周器によって分周数mで分周し、入力パルス列信号の周波数Fiと一定の関係を保った周波数Foを有する出力パルス列信号を得る。入力パルス列信号の周波数と出力パルス列信号の周波数の関係を示す周波数変換係数Rは、

R=N/m

により決定される。逓倍数Nと分周数mの値を変えることにより、少数を含んだ値の周波数変換係数Rとすることができる。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

発振器および位相同期回路のループ帯域補正方法

【課題】安定した高周波信号を発振する発振器および位相同期回路のループ帯域補正方法を実現する。

【解決手段】基準周波数の基準信号を発生する基準信号発生部と、前記基準信号とフィードバック信号との位相差に応じた電圧を出力する位相比較部と、前記位相比較部から出力された電圧が入力され、外部制御信号により、前記位相比較部から出力された電圧のゲインを調整するループフィルタと、前記ループフィルタによりゲインが調整された調整信号に応じた周波数の出力信号を発振する電圧制御発振部と、前記出力信号を分周した分周信号を前記フィードバック信号として前記位相比較部にフィードバックする分周部とを備える。

(もっと読む)

半導体装置

【課題】Loopbackテストの際に電圧振幅マージン不足の半導体装置が次工程へと流出するのを防止する。

【解決手段】シリアライザ17は、テストモード期間にクロック信号CLK1に応じてパタン発生器20が出力するパラレルのテストパタン信号をシリアル信号に変換して出力バッファ16よりテスト治具側の外部ループバックパスへ出力する。CPU21は、遅延制御信号DLC1,DLC2によって一方の可変遅延素子VDL1,VDL2の遅延時間を制御する。入力バッファ10の出力であるテストパタン信号VRxとLSIテスタ等より印加される外部基準電圧Vrefとの差動信号VRx1がCDR12に印加され、クロック信号CLK2が生成される。両信号VRx,CLK2の一方の位相が変更されて、外部基準電圧Vrefの値毎にタイミングマージンがチェックされる。

(もっと読む)

半導体装置

【課題】高速なクロックを必要とせずに、時間分解能を向上させたデジタルPWM制御を実現できる半導体装置を提供する。

【解決手段】複数段の第1遅延素子を有し、これら第1遅延素子に印加される制御電圧に応じて発振周波数が制御される電圧制御型クロック発生回路と、直列に接続された複数段の第2遅延素子を有する遅延回路と、複数段の第2遅延素子がそれぞれ出力するパルス信号の中から1つを選択する選択回路と、を備え、第1遅延素子と第2遅延素子とは同じ半導体基板に形成された同じ構成の遅延素子であり、第2遅延素子の遅延量は制御電圧に応じて調整される。

(もっと読む)

デューティ比補正回路

【課題】デューティ比補正回路のデューティ比検知速度を固定せずに、必要に応じて調整することによって、速いデューティ比の補正が必要な場合はデューティ比検知速度を増加させ、必要でない場合はデューティ比検知速度を減少させるデューティ比補正回路を提供する。

【解決手段】検知速度制御信号によりデューティ比検知速度が調整され、クロックのデューティ比を検知して補正信号を出力するデューティ比検知部と、前記補正信号に応答して前記クロックのデューティ比を調整するデューティ比補正部とを備える。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

パルス検出装置及びパルス検出方法

【課題】パルス信号を高精度に検出すること。

【解決手段】パルス検出装置1は、所定期間に中間電位を含むパルス信号を検出する。また、パルス検出装置1は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定手段を備えている。さらに、信号固定手段は、パルス信号が入力される入力信号線に接続されたプルダウン抵抗9又はプルアップ抵抗であるのが好ましい。なお、パルス検出方法は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定工程を含んでいる。

(もっと読む)

101 - 120 / 259

[ Back to top ]