Fターム[5J039KK28]の内容

Fターム[5J039KK28]に分類される特許

1 - 20 / 157

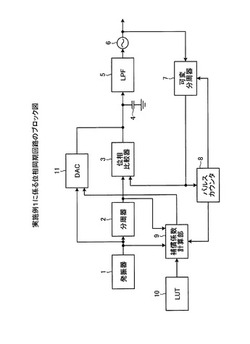

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

コンパレータシステム、アナログデジタルコンバータおよびコンパレータの閾値補正方法。

【課題】 閾値のずれを補正できるコンパレータシステムを提供する

【解決手段】 コンパレータは、一対のキャパシタを介して入力端子から入力信号を受ける一対の入力ノードと、入力信号の電圧差を示す出力信号を出力する出力ノードとを有する。第1制御回路は、コンパレータの閾値を補正する補正期間に、所定量の負荷が出力ノードに接続された状態で、出力信号の論理が反転するまで一対の入力ノードに設定するコモン電圧を変更し、出力信号の論理が反転するときのコモン電圧の値を求め、求めたコモン電圧を補正期間後の通常動作期間に使用する。第2制御回路は、出力ノードに接続される負荷の量を設定する。第3制御回路は、補正期間に、所定量の負荷が出力ノードに接続されているときのコンパレータの標準の閾値の変動量に対応する電圧差を有する第1電圧および第2電圧を入力端子にそれぞれ供給する。

(もっと読む)

電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

CDR回路

【課題】線形位相比較器を用いながら、チャージポンプやVCO等のアナログ回路を不要とすることができ、回路面積を抑えたCDR回路を提供する。

【解決手段】位相比較器902は、データエッジ検出回路111〜114により伝送データのエッジを検出し、データエッジマスク回路115〜118、サンプリング回路119〜122、低域通過型フィルタ123〜126、及びアナログ・デジタル変換回路127〜130により、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

比較器及びAD変換器

【課題】高速に、かつ高精度で動作する比較器及びADC等を構築すること。

【解決手段】従来の比較器は、比較器に入力される2つの入力電圧の差が小さいほど、安定した比較結果を得るまでに時間がかかり、また、2値の出力しか得られない。安定した比較結果が得られるまでの状態を、通常メタステーブル状態と呼んでいる。本発明は、このメタステーブル状態を積極的に利用する。すなわち、メタステーブル状態を検出することで、ハイとロウの中間レベルの判定を合わせて行える。これによって、3値以上を出力する比較器が容易に実現できる。本発明の比較器は、比較器の数を減少させることができると同時に、通常では判定が終了していない状態で比較動作を終了させることが可能になるため、速度向上にも役立ち、高速、高精度のADC(アナログデジタル変換器)等の機器に応用できる。

(もっと読む)

比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

電圧検知回路および半導体装置

【課題】入力電圧範囲が上限基準電圧から下限基準電圧までの範囲であるか否かについては検知できるが、その範囲内において、どの電圧レベルであるかを検知することができない。

【解決手段】電圧検知回路は、上限値と下限値との間を周期的に変化する非方形波信号と、入力電圧とを比較し、前者が後者より大きいか後者が前者より大きいかを示す二値の電圧検知信号を出力するコンパレータ3と、前記電圧検知信号に含まれるパルスの幅を計測することにより前記入力電圧の電圧レベルを検出する検知部5とを備える。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

比較装置

【課題】簡易な構成で複数の閾値を動的に選択することを可能にする。

【解決手段】比較装置100が、検知結果に応じて信号を出力するセンサ12、14と、複数の閾値Vrefを選択して出力する閾値選択部20と、センサ12、14が出力する信号と閾値選択部20が出力する閾値Vrefとを比較して、2値化された比較信号COMPを出力するコンパレータ30と、動作モードに応じた閾値Vrefを出力するように閾値選択部20を制御する制御部40と、制御部40の動作モードを切り替える動作モード切替部50とを備える。

(もっと読む)

時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

クロック逓倍回路、固体撮像装置及び位相シフト回路

【課題】クロック周波数が大きく変動しても、所望のデューティ比のクロック信号を精度よく生成する。

【解決手段】クロック逓倍回路10を、第1インバータ2と、第2インバータ3と、容量素子4と、電流供給部1と、差動検出部6と、逓倍信号生成部9とを備える構成とする。本発明では、電流供給部1は、第1クロック信号CKの周波数が高くなると電流を増大して第1インバータ2及び第2インバー3の電流シンク端子2aに該電流を供給する。また、差動検出器6は、容量素子4の両電極間の電位差信号が入力され、該電位差信号の変化範囲の中間値における比較結果に基づいて、第1クロック信号CKの正相信号に対して90度の位相差を有する第2クロック信号Xを生成する。そして、逓倍信号生成部9は、第1クロック信号CK及び第2クロック信号Xに基づいて第1クロック信号CKの2逓倍信号を生成する。

(もっと読む)

1 - 20 / 157

[ Back to top ]