Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

181 - 195 / 195

位相比較回路及びクロックリカバリ回路

データ信号とクロック信号の位相差を示す位相差信号を出力する位相比較回路であり、異なる複数の識別レベルを用いてデータ信号の位相を検出し、位相を示す複数の信号を出力する検出部と、検出部から出力される複数の識別レベルに対応する複数の出力信号の各々とクロック信号との位相差を示す複数の位相差信号を出力する位相比較部と、位相比較部から出力される複数の位相差信号の全部又は一部を用いて、複数の位相差信号のうちの1つの信号を出力するか又は出力しないかを制御する制御部とを有するように構成する。  (もっと読む)

(もっと読む)

半導体集積回路装置

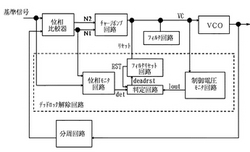

【課題】 高信頼性のデッドロック解除機能を持つPLL回路を備えた半導体集積回路装置を提供する。

【解決手段】 PLL回路のデッドロック解除回路として、制御電圧モニタ回路によりPLL回路の位相比較出力に対応したVCO制御電圧が規定値を超えることを検出し、位相モニタ回路により基準信号と帰還信号の位相が入力半サイクル以上外れていることを検出し、判定回路により上記制御電圧モニタ回路と位相モニタ回路の両検出信号が成立した場合にのみデッドロック状態と判定して、上記VCO制御電圧を強制的に下げてデッドロック状態の解除を行う。

(もっと読む)

データスライサ

【課題】 データ受信中に同一符号が連続した場合でも、受信信号に応じた適正な閾値電圧を生成することができる直流電位補償回路を備えたデータスライサを提供する。

【解決手段】 出力信号OUTの変化時に直列接続したNMOS31,32に流れる貫通電流によって充電される容量34と、この容量34の電荷を放電させる抵抗35と、容量34の電圧から高周波成分を除去するLPF36とを有する調整回路30を設ける。LPF36の出力信号を調整電圧ADJとして可変時定数型の積分回路10に与え、ベースバンド信号の変化が多いときには時定数を減少させ、該ベースバンド信号の変化が少ないときには該時定数を増加させて、その時定数に従って入力信号INを積分して基準電圧S10を生成する。これにより、比較回路23では、入力信号INに応じて適正に生成された基準電圧に基づいて、出力信号OUTを出力することができる。

(もっと読む)

画像転送調整アダプタ

【課題】画像転送インターフェースにおける画像データとクロック信号との同期を実用状態と同じ条件で簡単に評価できると共に、表示装置側の位相調整にも利用可能な画像転送調整アダプタを提供することを目的とする。

【解決手段】ビデオコントローラと表示装置との間を接続するコネクタにクロック信号を遅延させる遅延器を設け、遅延器の遅延量を外部から可変可能にすることで、画像データとクロック信号との位相調整を行い、表示装置側で受信される画像データ信号のセットアップ時間及びホールド時間を確保出来るようにした。

(もっと読む)

接点入力装置

【課題】 DIモジュールには接点入力信号に重畳するノイズを除去する機能はあるが、どの程度ノイズが重畳しているかを知ることはできなかった。そのため、機器の老朽化や環境の変化によって徐々に増加するノイズを早期に発見することができなかったという課題を解決する。

【解決手段】 接点入力信号の変化をカウントする入力値変化カウンタと、この接点入力信号の確定値の変化をカウントする入力確定値変化カウンタを有し、入力確定値変化カウンタと入力値変化カウンタのカウント値の差が設定値を越えると警報メッセージを出力する。接点入力信号にどの程度ノイズが重畳しているかを知ることができる。

(もっと読む)

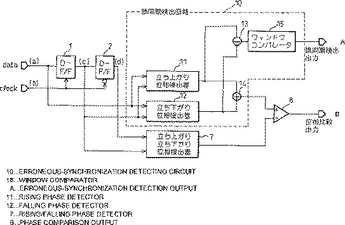

位相誤同期検出回路

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

ギガヘルツ周波数に効率的な遅延同期ループを有する多重位相クロック発生器を備える光学駆動回路

【課題】800MHzまたはそれ以上の周波数を有する入力クロックから、32個の異なる位相を発生させうる遅延同期ループ基盤の多重位相クロック発生器回路を備える光学(ディスク)駆動システムを提供する。

【解決手段】Nで分周されたクロックを、フィードバックループ内のM個の電圧制御される第1遅延素子に出力するための周波数分周器を有する遅延同期ループを備え、分周されていないクロックを遅延させて、M個の多重位相クロックを出力するために、フィードバックループの外部に同じM個の電圧制御される遅延素子を更に備える多重位相クロック発生器。光学駆動システムの光学駆動回路と、光学ディスク上の隣接する溝に書き込まれるマークの重複を防止するための書き込みストラテジを行う方法とを提供し、該回路及び方法は、GHzの周波数範囲で高解像度(例えば、T/32)でスイッチングする多重の書き込みストラテジ波形(チャンネル)を生成する。

(もっと読む)

変調回路、同変調回路を有する位相同期回路及び同位相同期回路を有するインタフェース装置

【課題】ジッタが低減される変調回路、又はそれを用いた、小数点以下の分周数を有する位相同期回路、或いは同位相同期回路を用いたインタフェース装置を提供すること。

【解決手段】本発明の変調回路は、レベルに応じて分離された信号modiと信号modtを出力するレベルシフト部0901と、信号modiを入力し、入力されるクロックclockによって動作して信号modoを出力する変調器0903と、信号modoと信号modtとを入力して演算を行ない、振れ幅1の信号divoを出力する演算器0905とを備える。信号divoは、例えば、任意の整数M,Nに対して、整数値N,(N+1),・・・・・・,(N+2M),(N+2M+1)を表す信号として実現される。

(もっと読む)

同期式ディジタルフィルタ

【課題】 装置の小型化を図り、しかも、クロック信号に同期し、且つ入力信号に重畳されたノイズを除去する。

【解決手段】 入力信号は第1フリップフロップF/F1の入力端D、正入力論理積回路AND1と負入力論理積回路AND2の第1入力端に供給される。第1フリップフロップF/F1の出力信号は、正入力論理積回路AND1と負入力論理積回路AND2の第2入力端に供給される。正入力論理積回路AND1と負入力論理積回路AND2の出力信号は、マルチプレクサMUXの選択信号端S1,S0に入力され、この選択信号でマルチプレクサMUXのデータ入力を切り替えて、マルチプレクサMUXの出力信号を第2フリップフロップF/F2に入力し、第1、第2フリップフロップF/F1,F/F2のクロック信号入力端CLKに供給される基準内部クロック信号発生部OSCからの内部クロック信号により第2フリップフロップF/F2に出力信号を得る。

(もっと読む)

ジッタ印加回路、及び試験装置

【課題】広帯域、高分解能、大振幅の位相ジッタ成分を、クロック信号に容易に印加することができるジッタ印加回路を提供する。

【解決部】与えられるジッタデータに応じた位相ジッタ成分を含むクロック信号を生成するジッタ印加回路であって、与えられる基準信号に応じて発振信号を生成するPLL回路と、発振信号を遅延させたクロック信号を出力する可変遅延回路と、ジッタデータの低周波成分に基づいてPLL回路の発振周波数を制御し、発振信号に位相ジッタ成分の低周波成分を印加する低周波印加部と、ジッタデータの高周波成分に基づいて可変遅延回路における遅延量を制御し、クロック信号に位相ジッタ成分の高周波成分を印加する高周波印加部とを備えるジッタ印加回路を提供する。

(もっと読む)

ダイオード回路

【課題】

小面積で集積可能なダイオード回路を形成することは困難であった。

【解決手段】

本発明のダイオード回路は、ソースが第1の入力端子に接続された第1のMOSトランジスタと、ソースが第2の入力端子に接続され、ゲートおよびドレインが前記第1のMOSトランジスタのゲートに接続された第2のMOSトランジスタ、および前記第1のMOSトランジスタのドレインに接続された第1の抵抗性負荷を有する差動回路と、前記差動回路の出力に基づいて導通状態が制御される第3のMOSトランジスタとを有している。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

クロックフィルタ回路及びクロックフィルタテスト回路

【課題】 入力信号に対する位相遅延の少ない、不要な高周波信号を除去したクロック信号を得ることができるクロックフィルタ回路を提供することを課題とする。

【解決手段】 ドレイン間が抵抗素子102を介して接続され、ゲートに入力クロック信号CLK1が入力される、ソースがVDDに接続されたトランジスタ100及び、ソースが接地されたトランジスタ102、トランジスタ102のドレインと接地とに接続されたコンデンサ103、トランジスタ100のドレインに接続されたCMOSインバータ104を備えた遅延回路2、遅延回路2と同様の構成で信号CLK1の代わりに、信号CLK1の反転が入力される遅延回路3、信号CLK1の反転と遅延回路2の出力とを入力とするAND回路4、入力クロック信号CLK1と遅延回路3の出力とを入力とするAND回路5、及びAND回路4の出力をRESETとし、AND回路5の出力をSETとするRS型フリップフロップを備えた。

(もっと読む)

妨害耐性を向上させるための方法及び集積回路

少なくとも一つのマイクロプロセッサチップ又はマルチプロセッサマイクロコントローラ(1)と少なくとも一つの別のモジュール(2)との間で、誤り信号が一つ以上の誤り信号の形で伝送される、集積回路(16)の妨害耐性を改善する方法であって、その伝送に関して、このマイクロプロセッサ又はこれらのマイクロプロセッサのクロック周波数に依存しない最小パルス長を規定して、その最小パルス長以降において、誤り配線上で所定のパルス長を持つ信号を誤りと解釈する方法を記載している。また、この発明は、特に、前記の方法を実行するための集積回路であって、特に、分離して配置された電力部品を有する、少なくとも一つのマイクロプロセッサチップ又はマルチプロセッサマイクロコントローラ(1)及び少なくとも一つの別のモジュール(2)と、少なくとも一つの誤り配線(3,4)を介して、誤りパルス(6,6’)を順番に出力するための一つ以上のパルス拡大機器と信号遅延機器の両方又は一方とを備えた集積回路に関する。  (もっと読む)

(もっと読む)

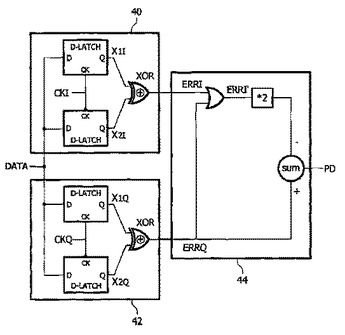

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

181 - 195 / 195

[ Back to top ]