Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

121 - 140 / 195

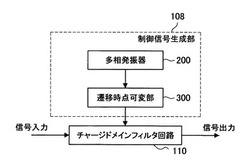

信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法

【課題】信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法を提供すること。

【解決手段】信号レベルが第1のレベルと第2のレベルの間で遷移し、各々が同一の周波数および所定の位相の差分を有する複数の基礎信号であって、任意の基礎信号の信号レベルが第1のレベルである期間、および該任意の基礎信号に対して前記所定の位相遅れを有する次の基礎信号の信号レベルが第1のレベルである期間が重複する複数の基礎信号を生成する多相発振部と、前記各基礎信号の第1のレベルから第2のレベルへの遷移時点を、前記各基礎信号の前記次の基礎信号の第2のレベルから第1のレベルへの遷移時点以前に変化させてパルス信号を生成する遷移時点可変部300と、を備える信号生成装置。

(もっと読む)

スイッチング回路

【課題】 装置に依存することなく良好なノイズ特性と損失特性を実現することができるスイッチング回路を提供すること。

【解決手段】 フィードバック回路部41を備える規範電圧波形追従駆動部4によりスイッチング素子を駆動して負荷を作動させるスイッチング回路1において、フィードバック回路部41を備える規範電圧波形追従駆動部4へ入力する信号波形を、予めノイズ特性と損失特性を設定した波形にして出力する規範電圧波形生成部3を備えた。

(もっと読む)

半導体集積回路装置及びデューティ制御方法

【課題】動作速度を向上出来る半導体集積回路装置及びデューティ制御方法を提供すること。

【解決手段】第1クロックCLK1に同期して動作し、該第1クロックCLK1が“H”レベルでアクティブとなる第1クリティカルパス12と、“L”レベルでアクティブとなる第2クリティカルパス13とを含むプロセッサコア2と、第2クロックCLK2のデューティを制御して前記第1クロックCLK1を生成する第1クロック生成部3と、前記第1クロックCLK1と、前記第1クリティカルパス12で生じる遅延時間Δtd1だけ遅れた第3クロックCLK3との第1位相差UPと、前記第1クロックCLK1と、前記第2クリティカルパス13で生じる遅延時間Δtd2だけ遅れた第4クロックCLK4との第2位相差DNとが最小となるように前記デューティを制御するよう、前記第1クロック生成部3に命令する制御部4とを具備する。

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

並列接続トランジスタ

【課題】配線のための面積増加なしに各トランジスタの入力信号の強度及び位相を均一にできる並列接続トランジスタを提供する。

【解決手段】並列接続トランジスタ50は、信号入力端子60に接続される伝送線路70、72と、伝送線路70及び72に沿って一列に配列されたトランジスタ84−1〜84−8及び88−1〜88−8と、伝送線路70、72に沿って一列に配列され、伝送線路70、72に一端が接続され、トランジスタ84−1〜84−8及び88−1〜88−8の対応する1つのベース端子に他端が接続された複数の容量素子82−1〜82−8及び86−1〜86−8とを含み、容量素子82−1〜82−8及び86−1〜86−8の容量値は、信号入力端子60からの伝送線路の線路長が大きいほど、小さくなっている。

(もっと読む)

信号処理システム、記録情報再生システムおよび信号受信システム

【課題】製造コスト上昇を抑える。

【解決手段】信号処理システムであって、制御端子に与えられた制御信号に応じた遅延を、入力端子に入力された信号に与えて出力端子から出力する第1の遅延回路と、前記第1の遅延回路と同様に構成され、入力端子と出力端子とが接続された第2の遅延回路を有し、発振信号を出力する発振器と、前記発振器の発振信号に応じた信号と基準となる信号との間の位相を比較し、比較結果を示す信号を出力する位相比較回路と、前記位相比較回路の出力信号の低周波成分を、前記第1及び第2の遅延回路の制御信号として用いられるように出力するフィルタ回路とを有する。前記第1の遅延回路の入力端子に与えられ、その出力端子から出力された遅延した信号が、前記基準となる信号として前記位相比較回路に与えられている。

(もっと読む)

クロックデータリカバリー回路及び通信装置

【課題】LSI化に適し且つ従来のPLLを用いたのと同等の特性を設定できるシリアルデータインターフェースのCDR回路を提供する。

【解決手段】本発明のCDR回路は、所定周波数のクロックの周期T1をN分割したT2時間ずつずらしたN相のクロックを出力する手段、シリアル転送されたデータをT2時間毎にサンプリングする手段、サンプリングしたデータを周期T1毎に第1のNビットパラレルデータに変換する手段、サンプリングしたデータのデータ変化点を示す第2のNビットパラレルデータに変換する手段、及び、第2のNビットパラレルデータを位相情報入力としてシリアルデータのデータ変化点の略中間位置を示す第3のNビットパラレルデータを出力する手段を有し、第3のNビットパラレルデータが示したビット位置と同じ、第1のNビットパラレルデータのビット位置データを復元データとすることを特徴とする。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

ディジタル信号の位相差検出方法

【課題】比較的低速かつ小規模のディジタル回路により精度の高い位相差検出を行う。

【解決手段】トラッキングサーボ回路10において、入力部のローパスフィルタ(LPF)12〜18および利得制御増幅器(GCA)20〜26はアナログ回路であり、A/D変換器28〜34より後段のオフセット・キャンセル回路36〜42、イコライザ(EQ)44〜50、位相差検出器52,54、加算器56、LPF58、利得制御増幅器(GCA)60およびサーボDSP154はすべてディジタル回路で構成される。両位相差検出器52,54は本発明の位相差検出方法にしたがって両入力信号の位相差を検出する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の内部でデータ抽出回路のジッタ耐性をテストする。

【解決手段】半導体集積回路10は、第1のクロックを生成するクロック生成回路13と、第1のクロックを位相変調し、かつこの変調されたクロックを用いてジッタが付加されたテストデータを生成するテストデータ生成回路15と、テストデータをサンプリングして再生データを抽出するデータ抽出回路14と、再生データのエラーを検出する検出回路16とを具備する。

(もっと読む)

ノイズ除去回路

【課題】少ない素子数のノイズ除去回路で、入力信号のノイズ除去を行う。

【解決手段】ノイズ除去回路30には、信号処理部1及びシュミットトリガ回路2が設けられる。信号処理部1には、2入力NOR回路NOR1、インバータINV1、Pch MOSトランジスタPT1、及びNch MOSトランジスタNT1が設けられ、クロック信号CLK及びイネーブル信号ENbを入力する。シュミットトリガ回路2には、インバータINV2、Pch MOSトランジスタPT2、Pch MOSトランジスタPT3、Nch MOSトランジスタNT2、及びNch MOSトランジスタNT3が設けられ、クロック信号CLK及び信号処理部1から出力される2つの信号を入力し、ノイズが除去されたクロック信号CLKを出力信号Soutとして出力する。

(もっと読む)

信号発生装置

【課題】所望の位相雑音が付加された信号を簡易な構成で生成できるようにする。

【解決手段】2相キャリア信号生成手段21により90゜位相が異なる2相のキャリア信号Sc、Sc′を生成し、その一方Scと雑音信号発生器23から出力される雑音信号θnとを乗算器24に入力し、その乗算器24の出力信号Aの大きさを可変減衰器25で調整しBPF26で帯域制限して、他方のキャリア信号Sc′とともに合成器27に与えて加算合成または減算合成する。この構成で、雑音信号θnの振幅がキャリア信号Scの振幅に対して十分小さければ、振幅雑音が極めて少なく、雑音信号θnに対応した位相雑音が含まれた信号Snを合成器27から出力することができる。

(もっと読む)

PLL回路

【課題】入力信号の断、回復状態でも出力の周波数変動を抑制し、周波数精度を維持するPLL回路の提供。

【解決手段】入力を所望周波数に分周する第1分周手段3と、電圧制御発振器7出力を所望周波数に分周する第2分周手段8と、前記第1分周手段3出力と前記第2分周手段出力8間の第1位相比較手段4と、前記第1分周手段3出力と前記第2分周手段8出力の反転の一方の第1選択手段11と、前記第2分周手段8出力と前記第1選択手段11出力間の第2位相比較手段12と、前記第1位相比較手段4出力と、前記第2位相比較手段12出力の一方の第2選択手段6と、入力信号監視手段9と、前記入力信号監視手段9からの監視結果に対して一定時間のタイミングを生成するタイミング生成手段10と、を備え、前記第1選択手段11及び前記第2選択手段6は、前記タイミング生成手段10からの信号状態に従って選択する。

(もっと読む)

波形整形回路及び無線受信装置

【課題】波形整形特性の低下を抑制しつつ、立ち上り特性を向上させることができる波形整形回路を提供すること。

【解決手段】入力信号Vinを基準信号Vrefに基づいて二値波形に整形した出力信号Voutを生成する波形整形回路1において、基準信号Vrefを生成する基準信号生成器2と、入力信号Vinと基準信号Vrefとの比較結果に応じて出力信号Voutを生成する比較器COMP1とを備え、基準信号生成器2は、入力信号Vinにおけるピークホールド値(Vp)とボトムホールド値(Vb)の中間電圧Vcを基準信号Vrefとして比較器COMP1に出力した後、入力信号Vinを積分した電圧を基準信号Vrefとして比較器COMP1に出力する。

(もっと読む)

光学的分配回路網を有する光電気発振器クロック

【課題】スキューおよびジッター等が低減されたクロック信号の分配システムおよび方法を提供する。

【解決手段】クロック信号を必要とするコンポーネントを含む電子システム用のクロック回路は、光クロック出力(6)において光クロック信号を発生するための光電気発振器(4)と、光クロック出力(6)を光電気発振器(4)に結合し戻すフィードバックループ(8)とを備える。

(もっと読む)

クロック信号停止判定回路

【課題】クロック信号の立ち上がりエッジを検出するようにして、波形の悪いクロック信号の停止判定を行うことができるようした。

【解決手段】エッジ検出回路11は、排他的論理和11aと、コンデンサと抵抗からなる遅れ回路11bから構成される。このエッジ検出回路11の入力端にクロック信号12が入力されると、エッジ検出回路11は、入力されるクロック信号を排他的論理和11aと遅れ回路11bにより、出力には幅の狭いパルス信号13を送出する。

この幅の狭いパルス信号13は、LPF14に入力されて処理されると、LPF14の出力には、図示波形の信号15を得る。この波形の信号15は、ウィンドウコンパレータ16で異常判定レベルH,Lと比較判定される。判定結果がウィンドウコンパレータ16から出力される。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

情報処理装置および情報処理方法

【課題】低実装コスト、低消費電力、マルチスタンダード対応のサンプリングレート変換を実現する。

【解決手段】バッファ142は、シリアル信号をLビットのパラレル信号に変換してデシメーションし、ある時刻の入力信号からFIRの次数分だけ遅延した信号までを1グループの入力系列とする。セレクタブロック143のセレクタ151は、Lビットの入力に対して、後段の加算平均または間引きの係数に対応するNビットの信号が出力されるように、入力信号を選択、補間する。加算処理部144の加算または出力選択部161は、コントローラ141の制御に基づいて、セレクタ151のNビットの出力を加算して出力するか、Nビットのうちの1ビットを出力する。デジタルフィルタ145は、加算または間引きによって得られた系列とFIRフィルタのタップ係数を用いて、フィルタの演算を実行する。本発明は、受信装置などのデジタルブロックに適用できる。

(もっと読む)

入力信号処理回路

【課題】入力信号をフィルタ処理すると共に処理された信号の初期及び終期の変化における遅延時間に差が生じないようにする。

【解決手段】電源VBと入力端子I1との間に直列に接続されたコンデンサC1及び抵抗R1からなるローパスフィルタLPFと、そのコンデンサC1と並列に時定数切替回路CTを構成するコンデンサC2及び抵抗R2を設け、コンデンサC2及び抵抗R2の入力端子I1側をダイオードD1を介して抵抗R1及びコンデンサC1のノードに接続し、抵抗R1及びコンデンサC1のノードとトランジスタQ1のベースとをダイオードD2を介して接続する。フィルタ回路による初期変化の応答遅れと略同一の応答遅れとなる入力信号の終期変化とすることができ、入力信号処理回路に対する入力信号と出力信号との信号長さを同じにすることができる。

(もっと読む)

パルス幅検出回路、直流成分キャンセル回路及び受信回路

【課題】受信電流のパルス幅に応じたほぼ正確なパルス幅を持つ受信信号を出力する受信回路を提供すること。

【解決手段】第1フィルタ回路24は、電圧信号VA1を高域通過フィルタを通した第1の成分と、前記電圧信号VA1の低周波成分もしくは直流成分に基づく第2の成分を含む第1の処理信号S1を生成する。第2フィルタ回路25は、第1の処理信号S1を増幅した電圧信号VA2を高域通過フィルタを通した成分からなる第2の処理信号S2を生成する。そして、2値化回路26は、第2の処理信号S2を増幅した電圧信号VA3を2値化して受信信号RXを生成する。

(もっと読む)

121 - 140 / 195

[ Back to top ]