Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

141 - 160 / 195

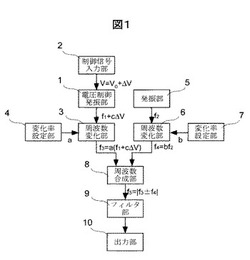

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

信号処理回路

【課題】たとえば非接触形ICカードの読取信号などのように、クロック信号に2値信号が重畳しており、しかもノイズが混入するような入力信号を適切に処理するための信号処理回路構成を簡単化する。

【解決手段】逆並列接続のダイオードD1 、D2 を介して入力信号S1 を非反転入力端子に入力させる比較器11と、非反転入力端子に接続する片端接地のコンデンサCとを設け、比較器11の反転入力端子には、入力信号S1 を分岐入力させる。

(もっと読む)

IC

【課題】外部ピンまでのL成分と、ICを実装した基板上のL成分を介して、IC外部のバイパス・コンデンサによって流れる過渡電流による電圧変動により引き起こされる放射ノイズの低減を目的とする。

【解決手段】同期式のロジック回路において、基準クロックを分周して周波数が同じで位相の異なる動作クロックを生成して、同期式のロジックを複数のブロックに分割して、それぞれのブロックを前記 位相の異なる動作クロックで駆動するシステムであって、各動作クロックは、立ち上がり、立下り、共に重ならない位相とする。

(もっと読む)

パルス生成回路及び変調器

【課題】高いOn/Off比を実現するパルス生成回路及び変調器を、小回路規模、低消費電力で提供する。

【解決手段】短パルス生成回路は、発振回路101と、制御信号発生回路102と、間欠逓倍回路103と、フィルタ104と、出力端105からなる。発振回路101、及び間欠逓倍回路103は能動素子で構成されるアクティブ回路である。発振回路101から連続信号が出力されて間欠逓倍回路103に入力され、制御信号発生回路102から出力される制御信号によって間欠逓倍回路103が間欠的に動作することで短パルス信号を生成し、スプリアス成分はフィルタで除去される。

(もっと読む)

デジタルフィルタ装置、位相検出装置、位置検出装置、AD変換装置、ゼロクロス検出装置及びデジタルフィルタ用プログラム。

【課題】ゼロクロスする信号からチャタリング等のノイズの影響を除去可能なデジタルフィルタ装置を提供する。

【解決手段】2値のデジタル信号DINをフィルタリングして2値のデジタル信号DOUTを出力するデジタルフィルタ装置4は、トリガ信号が入力される度に、デジタル信号DOUTの信号レベルを切り換えるトグルフリップフロップ12と、デジタル信号DINの信号レベルと、出力デジタル信号DOUTの信号レベルとが、不一致となる間、第1イネーブル信号EN1を出力するXOR回路13と、第1イネーブル信号EN1が出力されている間、クロック信号CLKに同期して計数していき、計数値が上限値に到達したときに、計数値を初期値に戻すとともにトリガ信号としてのキャリーオン信号ON_RCOをトグルフリップフロップ12へ出力するチャージカウンタ14とを備える。

(もっと読む)

RCキャリブレーション回路と、それを用いたRCキャリブレーション機能付RCフィルタ回路、受信チューナおよび携帯端末

【課題】低価格で校正時間が短いRCキャリブレーション回路を提供する。

【解決手段】このRCキャリブレーション回路では、基準クロック信号RefCLKを2分周して分周信号VINを生成し、分周信号VINの立ち上がりエッジに応答してキャパシタを充電し、キャパシタの端子間電圧VOUTが基準電圧Vrefを超えたとき、基準クロック信号RefCLKのレベルに応じてカウント値C1〜CNが増加または減少し、カウント値C1〜CNによってRCフィルタ回路およびRCリファレンス回路3の時定数を制御する。したがって、従来の遅延器75やラッチ回路76が不要となる。

(もっと読む)

信号発生器、信号発生方法、試験装置および半導体チップ

【課題】信号の位相を調整する精度を高める。

【解決手段】出力信号の位相を、指定された位相シフト量に応じて制御する信号発生器を提供する。信号発生器は、与えられる制御電圧の電圧値に応じた周波数の信号を生成し、出力信号として出力する電圧制御発振器と、出力信号を所定の分周比で分周した分周信号を生成する分周器と、分周信号と、与えられる基準信号との位相差に応じた電圧値の電圧を、制御電圧として出力する位相比較回路と、位相シフト量に応じて位相をシフトした基準信号を位相比較回路に入力する基準信号生成部と、出力信号に対して生成すべき位相シフト量から、基準信号生成部が基準信号に対して生成する位相シフト量を減じた位相シフト量に応じた電圧を、位相比較回路が出力する制御電圧に加算して、電圧制御発振器に入力させる加算電圧生成部とを備える。

(もっと読む)

周波数選択機能を有するミキサ

【課題】サンプリング周波数より高い周波数の動作制御信号を用いることなく、通過損失の無い周波数選択特性の高いミキサを提供する。

【解決手段】制御信号を供給するタイミング制御部と、積分制御信号によって入力信号の離散時間サンプルストリームを出力する第1のスイッチトキャパシタ回路と、電荷共有による高次IIRフィルタを構成する第2のスイッチトキャパシタ回路とを備え、積分制御信号の周波数は他の制御信号の周波数よりも高い。

(もっと読む)

パルス整形およびプログラマブル周波数シンセサイザを備えたSAWデバイスを利用するRFモデム

アナログおよびデジタルパルス変調を送信および受信するための、双方向直接シーケンススペクトル拡散半二重RFモデムが提供される。そのモデムは、送信器および受信器の拡散および逆拡散機能を行うためにSAWベースの相関器を組み込む。プログラマブル周波数シンセサイザは、局部発振器(LO)、IF質問パルスおよびクロック信号を含むモデムにおける種々の信号について周波数源を提供する。アップコンバータ/ダウンコンバータは、所望の周波数帯域への周波数変換を提供する。パルスゲーティングおよび質問パルス整形は、送信された拡散パルスのスペクトル側波帯を低減する。RFモデムは、アナログまたはデジタルパルス送信器および受信器として作動し、そしてOOK、PWM、PPMのようなデータ通信システムにおいて利用可能である。  (もっと読む)

(もっと読む)

シリアル・パラレル変換用の半導体集積回路

【課題】

確実な高速転送を実現可能なシリアル・パラレル変換用の半導体集積回路を提供する。

【解決手段】

シリアル・パラレル変換部2と、シリアル・パラレル変換部2で変換されたパラレルデータDPnをラッチするラッチ回路3と、シリアル入力データDSnと共に送信された入力クロック信号CLKinを位相比較器5の一方の入力端子において受信し、入力クロック信号CLKinを逓倍した逓倍クロック信号CLKm1を電圧制御発振器8で生成して、シリアル・パラレル変換部2に出力し、分周器9で逓倍クロック信号CLKm1を分周して第1分周クロック信号CLKd1を生成するPLL回路4と、逓倍クロック信号CLKm1に同期して第1分周クロック信号CLKd1をラッチし、位相比較器5の他方の入力端子とラッチ回路3に第2分周クロック信号CLKd2として出力するフリップフロップ回路10を備える。

(もっと読む)

位相同期ループ回路及びこの位相同期ループ回路の制御方法

【課題】電圧制御水晶発振器の経年変化による異常が発生しても、この異常を確実に検出できるようにした位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号W1を生成し、カウンタ115にて内部クロック信号から電圧制御水晶発振器12の異常を検出するために必要なウインドウ信号W2を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号W1,W2のハイレベル期間内に入っているか否かを判定し、ウインドウ信号W1のハイレベル期間に入っていて、ウインドウ信号W2のハイレベル期間内に入っていない場合に、電圧制御水晶発振器12の異常と判定するようにしている。

(もっと読む)

集積回路装置

【課題】 集積回路装置が静電気雑音により誤って初期化されるのを効果的に防止する。

【解決手段】 集積回路装置であるプロセッサ100は、複数のリセット入力端子101と、ANDゲート103を有している。ANDゲート103は、複数のリセット入力端子101から与えられる信号の論理積をとり、プロセッサ100内の順序回路を初期化するリセット信号として出力する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】偶数番目、奇数番目のデータのデューティの変動等に個別に対応し補正可能な、クロックアンドデータリカバリ回路の提供。

【解決手段】互いに位相が90度ごと離間した4相のクロック信号を生成する4相生成回路10と、位相が180度離間した2つのクロックを入力して位相を補間し、前記補間した信号、及び、前記補間した信号と逆相の信号を出力する第1及び第2のインタポレータ301及び302と、前記第1、第2のインタポレータからの4相のクロックを入力し、第1及び第2インタポレータ301及び302から出力される4相のクロック信号はそのままバッファリングして出力し、第1及び第2のインタポレータ301及び302からの4相のクロック信号のうち、位相が相隣る2つのクロック信号を補間してなる4相のクロックを生成する4相8相変換回路80とを備える。

(もっと読む)

拡散スペクトラムクロック発生装置としての非線形フィードバック制御ループ

【課題】この特許開示は、クロック信号とその高調波から生成されるスプリアス放射のために、最大限可能な限りの出力密度の削減を提供するクロック信号のための、ランダム拡散を生成するために、クロック信号を拡散する回路、システムおよび方法を示す。

【解決手段】これらの新規な発明は、拡散スペクトラムクロックの生成において、支援のために非線形フィードバック制御ループ116を利用し、高価な遮蔽や他のEMI抑制方法を利用することなく、クロック信号とその高調波によって生成されるスプリアス放射のためのFCC要求に合格できる電子製品が得られる。

(もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

ジッタ注入を組み込んだ高速トランシーバテスタ

高速シリアルトランシーバ回路をテストするためのテスタである。このテスタはジッタ生成器を含み、このジッタ生成器は、急速に変化する位相選択用信号を使用し、2つ以上の互いに異なる位相のクロック信号から選択し、位相変調した信号を生成する。この位相選択用信号は低い周波数の成分および高い周波数の成分を含むよう設計する。前記位相変調した信号は位相フィルタへの入力であり、この位相フィルタは所望でない高い周波数の成分をフィルタする。前記位相フィルタのフィルタ処理出力は、データ送信シリアライザへの入力であり、このデータ送信シリアライザは、前記トランシーバ回路への入力のため、ロースピードパラレルワードを高速のジッタ付与テストパターンへシリアライズする。  (もっと読む)

(もっと読む)

ノイズフィルタ及びフィルタリング方法

【課題】 本発明は、ノイズ除去時間をハードウエアにより決定し、プロセッサが使用される環境に最適なノイズ除去時間を決定することが出来るノイズフィルタ及びフィルタリング方法を提供することを課題とする。

【解決手段】 選択回路18はフィルタの段数が1段の信号Xをフィルタ出力信号OUTとして選択出力している。波形チェック部18は、フィルタ出力信号OUT上のパルス幅が、最小パルス幅指定レジスタ20の設定値より小さいとき、選択回路19にフィルタの段数が2段の信号Y、3段の信号Zを選択出力させる。段数の最適化処理が終了するとフィルタ値最適化完了フラグ(STATUS BIT)21をセットする。

(もっと読む)

ノイズフィルタ回路

【課題】 遅延時間以上の幅のノイズパルスが入力されたために完全にノイズが除去しきれなかった場合においても、ノイズパルスを後段へと通過させず、正規の信号パルスのみをクロック信号に同期させて出力させることができるノイズ除去回路を提供する。

【解決手段】 前記課題を解決するために、本発明によるノイズフィルタ回路は、遅延回路を用いたノイズ除去回路の後段にフリップフロップを追加する構成とし、そのフリップフロップへ入力されるクロック信号をノイズ除去回路とは別時間遅延させた正規の信号パルスとし、これに同期させる構成とした。

(もっと読む)

状態検出回路及び発振停止検出装置

【課題】 従来の発振停止検出回路は、クロック信号が何ら停止していないにも拘わらず、通常用電源電圧及び予備用電源電圧の切り替えにより、瞬間的に、クロック信号が停止している旨が出力されるという問題があった。

【解決手段】 本発明に係る発振停止検出回路は、インバータ回路と、1段目、2段目のトランジスタと、第1、第2のコンデンサと、抵抗器と、相互に並列接続された第1、第2のトランジスタと、通常用電源電圧の入力及び予備用電源電圧の入力を選択的に受け、第1のトランジスタの入力端に、通常用電源電圧の入力を受けるとき定電圧を出力し、予備用電源電圧の入力を受けるとき予備用電源電圧を出力する定電圧生成回路とを含む。

(もっと読む)

信号分離回路および信号送信回路

【課題】 同一の信号線を介しての複数の信号の伝送を可能することを目的とする。

【解決手段】 同一の信号線から受信した複数のパルス信号を分離する信号分離回路21において、PCオン信号分離回路40が、信号線を介して受信したPC/TVオン信号から第1のパルス幅を有するPCオン信号を検出して対応する第1の出力信号を生成する。TVオン信号分離回路50が、PC/TVオン信号から第1のパルス幅よりも短い第2のパルス幅を有するTVオン信号を検出して対応する第2の出力信号を生成する。

(もっと読む)

141 - 160 / 195

[ Back to top ]