Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

101 - 120 / 195

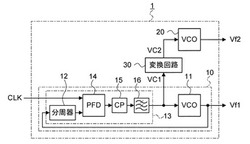

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

充放電回路および2値化回路

【課題】RSSIを使用したASK信号の復調時においても、2値化の閾値と比較される入力信号の振幅を一定に保つ。

【解決手段】RSSI検波器17にて復調されたASK信号はピークホールド回路23に入力され、ピークホールド回路23は、充放電部24に入力される入力信号のピーク値を検出し、クリップ回路22は、充放電部24に入力される入力信号のピーク値から一定値以下のレベルをクリップし、充放電部24は、クリップ回路22にてクリップされた信号を用いてコンデンサC2を急速充放電することで、コンパレータ27の閾値として用いられる基準電圧Vrefを発生させる。

(もっと読む)

振幅制限増幅回路

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40とを備える。

(もっと読む)

発振装置

【課題】通信機などが必要とする発振装置の発振周波数範囲の広帯域化が、簡単な構成で精度よく行えるようにする。

【解決手段】8GHzから12GHzなどの第1の周波数帯域幅の可変範囲を持つ低位相雑音な発振手段と、発振手段の発振出力を分周する周波数分周器とを備える。発振手段が出力する発振信号の周波数と、周波数分周器で分周する分周比を制御して、周波数分周器の出力周波数を、発振手段の発振周波数以下の周波数で、第1の周波数帯域幅と同じかそれ以上の周波数帯域幅で可変設定される所望の周波数とする制御を行う。

(もっと読む)

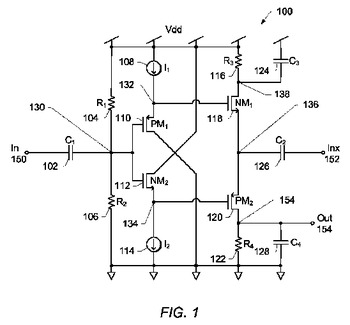

電気物理層活動検出器

低電流差分信号活動検出器回路は、1組の差分入力線に付加されるより小さな差分信号を検出しつつ、同一の1組の差分入力線上の大きな同相信号を除去するように、構成され得る。前記検出回路は、トランスリニア・バッファを含み得る。前記トランスリニア・バッファは、前記バッファ入力および前記バッファ出力において前記差分入力信号によって駆動される。これにより前記検出回路の前記入力を駆動する前記差分信号は、前記バッファ出力デバイスを通じて半波整流され得、検出された出力を提供するようにフィルタリングされ得る。同相信号が付加されると、前記バッファの入力および出力は相互に追跡し合い、前記出力デバイス内において整流される電流は無く、これにより、同相信号は除去される。前記検出回路は、2つのバッファと共に構成することもできる。これらの2つのバッファの出力は、共通ノードに連結され、各バッファ入力は、前記差分入力信号のうちそれぞれ1つによって駆動される。これにより前記検出回路の前記入力を駆動する前記差分信号を、前記2つのバッファの前記出力デバイスを通じて全波整流することができ、検出された出力を提供するようにフィルタリングすることができる。前記2つのバッファは、対称構造で構成することができ、これにより、前記バッファの前記出力が共通ノードに連結された際に同相信号を除去することが可能になる。  (もっと読む)

(もっと読む)

ミキサ

【課題】ダイレクトコンバージョン方式や低IF方式では局部発振器信号の高調波成分によるノイズを低減させる。

【解決手段】位相差がそれぞれ120°異なる3相信号を局部発振信号として受信信号と乗算し、それぞれの復調波の同相信号をキャンセルすることで、局部発振信号の高調波成分のうち、第3高調波によるノイズ成分をキャンセルすることができるミキサを提供する。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

半導体装置

【課題】半導体装置において、ユーザボードの違いや製造ばらつきがあっても、電源共振ノイズによる問題を回避することができる技術を提供する。

【解決手段】半導体装置内の電源ノイズを観測する電源ノイズ観測回路1と、電源ノイズ観測回路1の出力に基づいて、生成クロック301の周波数が変化するクロック生成回路2と、生成クロック301が入力される演算回路ブロック3と、を備える。そして、前記電源ノイズ観測回路1によって観測される電源ノイズが低減するように、生成クロック301の周波数が調整される。

(もっと読む)

電子回路、情報再生装置

【課題】 セットアップ違反に対するより一般的な検出技術を提供する。

【解決手段】 外部からの入力データを受ける第1のフリップフロップと、前記入力データを受けるラッチと、このラッチの出力と前記第1のフリップフロップの出力との排他的論理和を入力する第2のフリップフロップとを備えた電子回路。また前記第1のフリップフロップの出力を入力とし前記第2のフリップフロップの出力に基づく通知信号を抑制信号入力として用いる電子回路を具備した情報再生装置。

(もっと読む)

ジッタ増幅回路、信号発生回路、半導体チップ、及び試験装置

【課題】入力信号に含まれるジッタを増幅するジッタ増幅回路150。

【解決手段】入力信号に含まれるジッタを増幅するジッタ増幅回路であって、入力信号を受け取り、入力信号の波形を歪ませることにより、入力信号の高調波成分を生じさせる歪回路と、歪回路が出力する歪信号を、ジッタを増幅すべき増幅率に応じた次数の高調波成分以外の成分を除去して通過させるフィルタとを備えるジッタ増幅回路。

(もっと読む)

信号変調回路

【課題】発振回路からの連続信号のレベル調整を行う場合であっても、送信電力を制御することが可能な信号変調回路を提供する。

【解決手段】信号変調回路の一例であるパルス生成回路は、発振回路と、制御信号発生回路と、逓倍回路と、フィルタと、制御部からなる。発振回路、及び逓倍回路は能動素子で構成されるアクティブ回路である。発振回路から連続信号が出力されて逓倍回路に入力され、制御信号発生回路から出力される制御信号によって逓倍回路が間欠的に動作することでパルス信号を生成し、制御部からの信号により電力レベルを簡易に調整する。

(もっと読む)

クロック信号生成回路、及びクロック信号生成回路の使用方法

【課題】リングオシレータを利用して基準クロック信号の周波数を逓倍した逓倍クロック信号を生成するクロック信号生成回路において、逓倍クロック信号のジッタを抑制する。

【解決手段】高速クロック発生回路2の主要部であるリングオシレータへの電源供給を時定数がτに設定されたローパスフィルタ23を介して行い、高速クロック信号CKrで基準クロック信号CKs(周波数fs)の周期をカウントする周期カウンタ4のカウント値(周期カウント値)DGを、基準クロック信号CKsに従って動作する逓倍クロック生成回路5が、nクロック周期で、逓倍クロック信号CKoに反映させる。そして、基準クロック発生回路3は、周波数fsがτ>n/fsを満たす基準クロック信号CKsを発生させる。

(もっと読む)

ノイズフィルタ回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60)は、入力信号(IN)を入力するラッチ回路(14;64)を備える。ラッチ回路(14;64)は、第1および第2の論理演算回路(たとえば、NAND回路)を含む。第1および第2のNAND回路のそれぞれにおいて、セット信号(S)またはリセット(R)信号を入力するP型トランジスタ(P1)の能力は、セット信号(S)またはリセット(R)信号を入力するN型トランジスタ(N1)の能力、および、このN型トランジスタ(N1)と直列に接続されるN型トランジスタ(N2)の能力(トータルな能力)より低い。ノイズフィルタ回路(10;60)は、ラッチ回路(14;64)からの出力信号(OUT(XQ;Q))を入力する波形整形回路(16)を、備えてもよい。

(もっと読む)

データセンタートラッキング回路及びこれを含む半導体集積回路

【課題】本発明は、外部環境の影響にも安定的に動作し、より向上した電力及び面積効率を具現するデータセンタートラッキング回路及びこれを含む半導体集積回路を提供する。

【解決手段】本発明は、直列連結した複数のクロックバッファーからなり、クロックをバッファーリングして出力信号を出力するクロックツリー;クロックに基づき、出力信号の位相の変化を感知して感知信号を出力する感知部;及び、感知信号に応じて、クロックツリーに供給される電流を調節し、出力信号の位相を調節するディレイ補償部を含む。

(もっと読む)

半導体集積回路

【課題】発振回路により作成される動作クロックによる不要な電磁輻射ノイズを低減する。

【解決手段】乱数発生回路10から出力された乱数データは、周波数可変データレジスタ12に格納される。周波数可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。発振回路13はクロックを発生する回路であり、クロックは不図示の動作クロック作成回路を通して動作クロックとして、内部回路14に供給される。発振回路13のクロックの周波数は、周波数可変データレジスタ12に格納された乱数データに応じて可変制御されるようになっている。また、周波数可変データレジスタ12に格納された乱数データに応じて可変制御される周波数の幅を制御するための制御データが格納される周波数可変幅制御レジスタ15が設けられている。

(もっと読む)

位相クロック発生器

【課題】より少ない数のトランジスターを使いながらも、高周波特性が反映されたクロック信号を生成でき、具現可能なクロック周波数帯域に限界がない位相クロック発生器を提供することと、回路サイズ及び電力消費量を最小化して、半導体設計及び工程が容易になり、トランジスターの動作周波数がそのまま反映された高周波クロック信号を生成することができ、ノイズ成分の影響を最小化することができる位相クロック発生器を提供する。

【解決手段】電源線及び接地線の間に繋がって4行とN列を構成して、多数の位相遅延信号をゲート端子を通じて入力されるトランジスターを含み、単位列を構成する4個のトランジスターの中で、一方の側の2個のトランジスターはNMOSでペアを構成し、他方の側の2個のトランジスターはPMOSでペアを構成して、前記単位列を構成するNMOSペアとPMOSペアの間のラインに繋がってクロック信号を送り出すバッファーを含む。

(もっと読む)

グリッチに備えるセルフタイマ回路の強化

グリッチに対する自己クロック回路を強化するための複数の技術が開示されている。グリッチフィルタが、デジタル設計の同じ場所に設けられている。ある実施例では、グリッチフィルタが動的に同調可能である。一実施例では、入力が出力によってロックアウトされる。差動信号のための回路のように、コード符号を見積もるための方法が与えられている。 (もっと読む)

PLL発振回路

【課題】分数分周型のPLL発振回路における抵抗やキャパシタの定数を小さくすると共に、雑音を低減する。

【解決手段】入力信号INと帰還信号FBaの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10aと、入力信号INと帰還信号FBbの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10bと、このノードNcに出力される信号の高周波成分を除去して制御電圧VCを生成するループフィルタ20と、制御電圧VCに応じた周波数foの出力信号OUTを生成するVCO30と、出力信号OUTの周波数をそれぞれ1/Mと1/Nに分周して帰還信号FBa,FBbを出力する分周器40a,40bを設ける。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

101 - 120 / 195

[ Back to top ]