Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

21 - 40 / 195

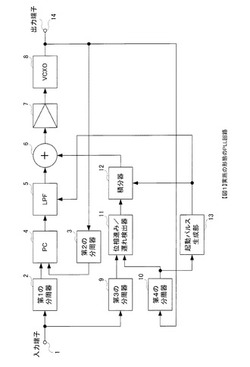

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

(もっと読む)

データ判定回路、受信器およびデータ判定方法

【課題】 データ判定回路の回路規模を大きくすることなく、孤立パルスを確実に検出する。

【解決手段】 閾値判定部は、2値データのデータ列を表すアナログデータ信号をオーバーサンプルすることにより生成されるデジタルコードを順に受け、負のデジタルコードが連続するときに増加値を示す閾値信号を出力し、正のデジタルコードが連続するときに減少値を示す閾値信号を出力する。孤立パルス判定部は、デジタルコードに閾値信号が示す値を加えて補正デジタルコードを生成し、連続する補正デジタルコードを用いて孤立パルスを検出する。バイナリ判定部は、連続するデジタルコードの符号を用いて2値データの論理を求める。データ選択部は、孤立パルスが検出されるときに、孤立パルスの論理を2値データの論理として出力し、孤立パルスが検出されないときに、バイナリ判定部により求められた2値データの論理を出力する。

(もっと読む)

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

PLL回路、PLL回路の動作方法およびシステム

【課題】 回路規模を増加することなく、PLL回路の精度を向上する。

【解決手段】 時間計測回路は、基準クロックの遷移エッジが現れてから、出力クロックの遷移エッジが2回現れるまでの時間間隔をカウント値として計測する。位相差正規化回路は、計測された時間間隔を出力クロックのクロック数で表される微少位相差に正規化する。また、位相差正規化回路は、PLL回路のロック後に、”1”または”2”を示す微少位相差が連続して現れるときに、”1”と”2”がランダムに現れるまで正規化係数を徐々にずらす。演算回路は、出力クロックの積算値から微少位相差の値を引いた値を、周波数制御語の積算値から差し引いて、基準クロックと出力クロックの位相差を示す位相差信号を生成する。発振回路は、基準クロックと出力クロックの位相を合わせるために、位相差信号に基づいて出力クロック信号の周波数を変更する。

(もっと読む)

ダイレクトサンプリング回路

【課題】時分割統合された信号系列に対して、時分割で兼用する場合であっても、各系統間で信号の混ざりを回避するダイレクトサンプリング回路を提供する。

【解決手段】スイッチトキャパシタフィルタ160の前段に系統毎にヒストリキャパシタ153,155を接続し、スイッチトキャパシタフィルタ160の後段に系統毎にバッファキャパシタ173,175を接続し、スイッチトキャパシタフィルタ160のローテーションキャパシタと接続するヒストリキャパシタ及びバッファキャパシタを入力している時分割系統毎に切り替える。

(もっと読む)

発振回路動作状態検出回路

【課題】発振回路の動作状態を短時間で検出する。

【解決手段】VDDの電源端子とVSSの電源端子の間にノードN1を共通接続点とするトランジスタMP1,MN1を直列接続し、ノードN2を共通接続点とするトランジスタMP2,MN2を直列接続する。ノードN1,N2の間に容量C1を接続する。ノードN1,N2にNOR1の入力側を接続する。トランジスタMP1,MN1に直列に電流源I1を接続し、トランジスタMP2,MN2に直列に電流I2を接続する。トランジスタMN1,MN2のOFF抵抗をトランジスタMP1,MP2のOFF抵抗より小さくする。発振回路の発振クロック信号が第1の論理のとき、トランジスタMP1,MN2をONさせると共にトランジスタMP2,MN1をOFFさせ、第2の論理のとき逆にする。

(もっと読む)

デジタル位相差検出器およびそれを備えた周波数シンセサイザ

【課題】高精度で回路面積および消費電力が小さいデジタル位相差検出器を提供する。

【解決手段】デジタル位相差検出器は、第1の信号を累積的に遅延させて各遅延量の信号を生成する遅延回路(10)と、第2の信号に同期して各遅延量の信号をラッチするフリップフロップ群(20)と、フリップフロップ群の出力から、第1の信号の立ち上がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第1の位相差、および第1の信号の立ち下がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第2の位相差を検出するエッジ検出器(30)と、第1および第2の位相差を記憶する記憶回路(40)と、記憶回路が記憶している過去の第1および第2の位相差の差分およびエッジ検出器が新たに検出した第1および第2の位相差の差分から第1の信号の周期を算出し、当該周期を基準にして第1および第2の信号の位相差を正規化する正規化回路(50)とを備えている。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

ノイズ対策回路

【課題】送,受信装置の動作に必要な差動信号とコモン信号を伝送して、コモンモードノイズのみを低減させることができるノイズ対策回路を提供する。

【解決手段】ノイズ対策回路1−1を2つのフィルタ回路2,3で構成した。フィルタ回路2(3)は、逆方向に巻回されたコイル25(35),26(36)を有し、コイル25,26(35,36)の両端が、入力端子21,22(31,32)と出力端子23,24(33,34)とに接続されている。フィルタ回路2(3)にディファレンシャルモード電流が流れると、高インピーダンスになり、コモンモード電流が流れると、低インピーダンスになる。フィルタ回路2を差動伝送路100に接続し、フィルタ回路3をフィルタ回路2とグランド線路110とに接続した。そして、フィルタ回路3の出力側をグランド領域120に接続した。

(もっと読む)

21 - 40 / 195

[ Back to top ]