Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

41 - 60 / 195

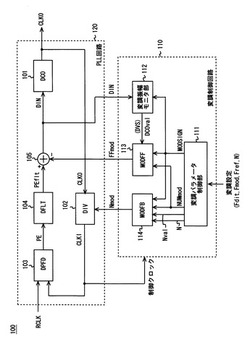

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

受信機器及び画像形成装置

【課題】周波数を周期的に増減させた拡散クロック信号を用いてデータを受信する場合に生じ得る通信の不成立を未然に防止でき、確実にEMI低減効果を得ることができる受信機器及び画像形成装置を提供する。

【解決手段】拡散クロック信号に基づいて、複数のビットを含むフレーム単位でデータを受信する際、受信速度に基づいて受信すべきデータのビット当たりの受信時間を算出し、該ビット当たりの受信時間に応じて前記拡散クロック信号の変更周期を調整する。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

クロック発生装置

【課題】出力するクロックの周波数を意識的に拡散して、テレビ受像機やパソコンモニタ映像受像機への電磁妨害のピークを減らすクロック発生装置を提供する。

【解決手段】周波数拡散情報発生回路90を設け、第二のDTO91と第二のDAC92にてデジタルLPF8から出力される位相誤差情報と周波数拡散情報から正弦波を発生し、アナログPLL93で逓倍することにより、クロック出力端子94から周波数拡散されたクロックを出力することができ、システムが用いる高い周波数からでる妨害を抑制するために意識的に周波数を拡散できるクロック発生装置を得ることができる。

(もっと読む)

電源制御タイミング信号発生回路および電源装置

【課題】 ある波形の電圧値を異なる閾値と比較するので、比較精度によって、不安定であった。

【解決手段】 制御波形発生回路12で発生された台形波形を各チャンネルの増幅器13a〜13cで設定されているゲインで増幅する。すると、高ゲインであるほど増幅器13a〜13cの出力電圧の台形波のエッジ部分の勾配が急であり、各電源回路11a〜11cのオン電圧に早く到達するので、スイッチ12aのオン時は、高ゲインの増幅器13a〜13cほど出力電圧が早いタイミングでオン電圧に達し、低ゲインでは遅いタイミングでオン電圧に達する。この結果、この例では、電源回路11a〜11cの順に起動することになる。逆に、スイッチ12aのオフ時は、低ゲインの増幅器13a〜13cほど出力電圧は早いタイミングでオン電圧以下に下がり、高ゲインでは遅れてオン電圧以下になる。この結果、この例では、電源回路11c〜11aの順に終了することになる。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

信号発生装置および試験装置

【課題】精度良く信号を出力する。

【解決手段】DA変換器と、DA変換器から出力される電圧をサンプルしてホールドするサンプルホールド部と、出力信号を伝搬して入力データに応じた信号を出力するアナログ回路から出力される信号の電圧とDA変換器の出力電圧とを比較する比較部と、DA変換器に設定データを与えて設定データに応じた設定電圧を出力させて、サンプルホールド部に設定電圧をサンプルさせ、サンプルホールド部によりホールドされた設定電圧をアナログ回路に与え、設定電圧が与えられてから安定化するまでのアナログ回路から出力される信号の電圧のセットリング波形を測定する測定部と、を備える信号発生装置を提供する。

(もっと読む)

信号発生装置および試験装置

【課題】簡易な構成で精度良く信号を出力する。

【解決手段】DA変換器と、DA変換器と当該信号発生装置の出力端との間に設けられたサンプルホールド部と、DA変換器の出力電圧を伝搬して入力データに応じた信号を出力するアナログ回路から出力される電圧とDA変換器の出力電圧とを比較する比較部と、ホールド期間において、入力データに代えて比較データをDA変換器に与えて比較データに応じた比較電圧を出力させ、比較部にアナログ回路から出力される信号の電圧と比較電圧とを比較させ、比較部の比較結果に基づいて、入力データに応じてDA変換器から出力される出力電圧を調整する制御部と、を備える信号発生装置を提供する。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

DCオフセット及び位相差検出装置及びDCオフセット及び位相差検出方法

【課題】互いに位相の異なるクロック信号の段階的な調整に適したDCオフセット及び位相差検出装置及びDCオフセット及び位相差検出方法を提供すること

【解決手段】本発明にかかるDCオフセット及び位相差検出装置50は、互いに位相の異なる第1及び第2のクロック信号の各々のDCオフセット量を検出し、各クロック信号のDCオフセット量を示すDCオフセット信号を生成するDCオフセット検出部51と、前記DCオフセット信号に応じて前記第1及び第2のクロック信号をDCオフセット調整することで生成された第3及び第4のクロック信号の位相差量を検出し、前記位相差量を示す位相差信号を生成する位相差検出部52とを備える。

(もっと読む)

1/fゆらぎ信号発生回路

【課題】

複数出力の、且つそれぞれの出力が異なる値の1/fゆらぎ信号を発生させ、複数の白熱電球やLED素子の発光をそれぞれに接続された1/fゆらぎ信号によって駆動し、イルミネーション効果を実現する。

【解決手段】

複数段のLFSR(リニアフィードバックシフトレジスタ)で構成されたGold系列の乱数発生回路において、各LFSR段のシフトレジスタ中の任意のレジスタのビット出力の値を、排他的論理和素子で構成された複数の加算器で加算し、それぞれの加算器の出力をシリアル−パラレル変換器に入力し、パラレルビットの値として、複数の乱数値を同時に出力

し、複数のデジタル・フィルタに入力し、複数の個々異なる1/fゆらぎ信号を同時に発生させることができる。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

画像形成装置、画像形成方法、及びプログラム

【課題】消費電力増加を抑制した画像形成装置、画像形成方法、及びプログラムを提供する。

【解決手段】上位装置からの印刷データを受信し、印刷する画像形成装置であって、コントローラが省エネ復帰信号を省エネ制御コントローラに出力した際は復帰要因送信ビットに“1”を立て、MAIN CPUが省エネ状態から復帰した後、復帰要因送信ビットが“1”ならば処理は行わず、復帰要因送信ビットが“0”ならば入力された全てのノイズの特性から最適なノイズキャンセル回路の設定値を計算し、設定変更するようにした。

(もっと読む)

同期化結晶発振器ベースのクロックを採用するシステム

【課題】改良された同期クロックシステムを提供する。

【解決手段】同期クロック信号を必要とする複数のシステムノードを有する電子システム用の同期クロックシステム。クロックシステムは、第1の同期バスと第1の同期バスから絶縁された第2の同期バスと、交互にバスに接続された少なくとも1対、そして好ましくは複数対のSXOモジュールを含む。システムノードの各々は、第1のバスに沿った任意の場所において適宜選択されたあらゆる接続点のうちの異なる1つで接続される。SXOモジュールが接続されるバスに沿った点は、およそ等間隔で隔てられる。システムノードは信号調整回路を用いてバスに接続され、信号調整回路は、補正回路、増幅器、周波数逓倍器、論理変換器、およびファンバッファを含んでいてもよい。

(もっと読む)

41 - 60 / 195

[ Back to top ]