Fターム[5J039KK33]の内容

Fターム[5J039KK33]に分類される特許

81 - 100 / 195

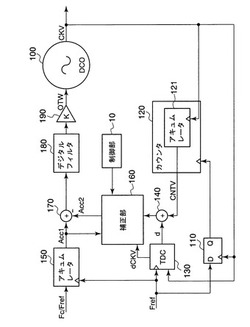

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

オーディオ装置及びオーディオ処理方法

【課題】従来技術における高周波クロック信号が生成する電磁妨害(EMI)を軽減させる。

【解決手段】本発明一実施例は、オーディオ装置を提供する。オーディオ装置は、デジタルマイクモジュールとオーディオコーデックを有する。デジタルマイクモジュールは、スペクトラム拡散クロックに基づき外部音源を捉えて、デジタル音源信号を発生する。オーディオコーデックは、クロック発生モジュール、格納ユニット、オーディオコーデックコアを有する。クロック発生モジュールは、クロック信号とスペクトラム拡散クロックを発生する。格納ユニットは、スペクトラム拡散クロックに基づきデジタルマイクモジュールからの第一デジタル音源信号を一時記憶し、クロック信号に基づき第一デジタル音源信号を出力する。オーディオコーデックコアは、デジタル−アナログ変換回路とアナログ−デジタル変換回路を有する。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

検波装置、無線受信装置及び検波装置の駆動方法

【課題】検波対象の信号に対応する平衡信号に混入する同相ノイズのレベルを低減して、検波精度を向上するのに好適な検波装置、無線受信装置及び検波装置の駆動方法を提供する。

【解決手段】無線受信装置1を、アンテナ10と、検波装置11と、帯域制限型増幅器12と、判別部13とを含んだ構成とし、検波装置11を、LNA11aと、整流回路11bとを含んだ構成とし、LNA11aにおいて、無線信号に対応する第1の交流信号及び第2の交流信号からなる平衡信号を生成すると共に、同じタイミングで、第1の交流信号を整流回路11bを構成するNTr5のゲート端子とNTr6のソース端子とに入力し、第2の交流信号をNTr5のソース端子とNTr6のゲート端子とに入力して、これら交流信号に含まれる同相ノイズ成分を打ち消すようにした。

(もっと読む)

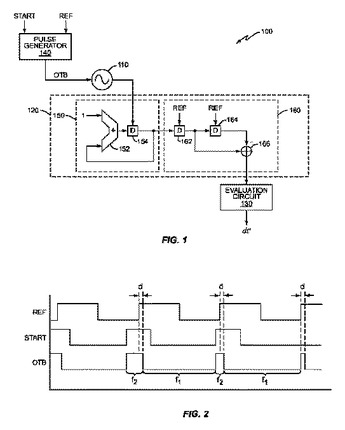

ノイズシェーピング時間測定回路

時間測定回路のある実施形態では、リファレンス信号期間の第1の部分においてデジタル制御発振器(DCO)を第1の周波数で動作させ、前記対象信号と前記リファレンス信号との時間差に応じて前記リファレンス信号期間中に動作周波数を前記第1の周波数から第2の周波数に変更することにより、対象信号とリファレンス信号の時間差が測定される。時間測定回路は、前記リファレンス信号期間において前記デジタル制御発振器の出力で何回の信号遷移が発生したかを継続的に計数する。対象信号とリファレンス信号の時間差は、前記リファレンス信号期間において計数された前記信号遷移の回数に基づいて推定される。

(もっと読む)

(もっと読む)

信号生成回路及びその信号生成方法

【課題】信号生成回路において、容易に、十分な出力信号レベルを確保したまま、スプリアスとなる高調波を除去し、正弦波を生成することである。

【解決手段】本発明の信号生成回路の一態様は、第1の入力信号に基づき第1の信号を出力する第1の分周器1bと、第2の入力信号に基づき第2の信号を出力する第2の分周器1bと、第1の入力信号と第2の入力信号との間に第1の位相差φを与える第1の移相器2a、2bと、第1の信号と第2の信号とを合成し、出力信号を生成する合成回路3a〜3dと、を有し、第1の移相器2a、2bは、第1の信号において除去対象となる第1の高調波成分が、第1の信号と第2の信号との間で逆位相となる第1の位相差φを第1の入力信号に付加して第2の入力信号を生成する。

(もっと読む)

位相補間回路

【課題】線形領域での信号重ね合わせを行なうことなく所望の位相のクロック信号を生成可能な位相補間回路を提供する。

【解決手段】位相補間回路は、一定の周波数及び位相を有する基準タイミング信号のパルスの位相と同一の位相の第1のパルスと前記基準タイミング信号のパルスの位相からずれた位相の第2のパルスとを含むパルス列を生成するパルス列生成回路と、前記第1のパルスの位相と前記第2のパルスの位相との重み付け平均に応じた一定の位相位置にパルスを有する出力パルス信号を前記パルス列に基づいて生成するパルス位相平均化回路とを含み、前記重み付け平均の重みは、所定期間内において前記パルス列に含まれる前記第1のパルスの数と前記第2のパルスの数との比率に応じた重みである

(もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出する検出回路102と、FM信号の復調後の信号に基づいて閾値を設定する閾値設定回路104と、を備えるFM信号のノイズ検出回路とする。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出し、検出信号を欠落が発生している期間出力する検出回路102と、検出信号を受けた時点におけるFM信号の復調後の信号を保持するホールド回路40と、検出信号が出力されていない間はFM信号の復調後の信号を選択して出力し、検出信号が出力されている間はホールド回路40の出力を選択して出力するセレクタ回路42と、を備えるノイズキャンセラ部106を含む。

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

スイッチ装置

【課題】スイッチと判定部とを接続する電線の削減、並びに小型化及び軽量化が可能なスイッチ装置の提供。

【解決手段】複数のスイッチの各接点SW1,SW2,・・・SWnに信号を与えて、スイッチのそれぞれのオン/オフ状態を検出するスイッチ装置。各接点SW1,SW2,・・・SWnは並列に接続されており、各接点に同一の信号を与える信号出力部2と、各接点SW1,SW2,・・・SWn及び固定電位部間に接続された互いに異なるインピーダンス回路Y1,Y2,・・・Ynと、信号出力部2が与えた信号を検出する信号検出部1と、信号検出部1が検出した信号に基づき、スイッチのそれぞれのオン/オフ状態を検出する状態検出部3とを備えている。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

ピークレベル検出装置

【課題】1ビットオーディオ信号のピーク値を求めることを、低演算量かつ高精度で実現可能な装置を提供すること。

【解決手段】1ビットストリームが供給されるとディレイバッファ30に順次データが書き込み記憶される。そして、ピーク位置検出部10が、ディレイバッファ30に記憶されたピーク値のアドレスである最大ピークアドレスを検出しこれをデータ読み出し部20に送る。データ読み出し部20は、送られてきた検出された最大ピークアドレスに応じてディレイバッファ30の対応するデータを読み出す。そして、LPF40は、この読み出されたデータの低域を通過させ、最後にABS部50が信号を絶対値化してマルチビットピーク値を出力する。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

多周波発振装置

【課題】装置の大型化を招くことなく、位相のコヒーレントを保つことができる多周波発振装置を得ることを目的とする。

【解決手段】基準発振器1により発振されるクロックの周波数fclkに応じた周波数切替時間間隔Δtで、周波数の切替を指示する制御信号を出力する周波数切替制御器2と、周波数切替制御器2から制御信号を受ける毎に、基準発振器1により発振されるクロックの周波数fclkに応じた周波数間隔Δfで、出力信号の周波数f1,f2,…,fnを切り替える信号発生器3とを備え、クロックの周波数fclkと、周波数間隔Δfと、周波数切替時間間隔Δtとの間に、式(6)または式(7)の関係が成立しているように構成する。

(もっと読む)

81 - 100 / 195

[ Back to top ]