Fターム[5J039LL01]の内容

Fターム[5J039LL01]に分類される特許

1 - 11 / 11

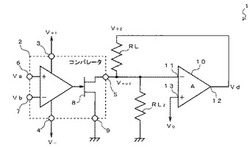

コンパレータ回路

【課題】プルアップ抵抗の抵抗値や接続する外部回路に依存せず、ハイレベル出力電圧を所望の電圧に精度よく設定することが可能なコンパレータ回路を提供する。

【解決手段】オープンドレイン型またはオープンコレクタ型のコンパレータ2と、一端がコンパレータ2の出力端子5に電気的に接続されたプルアップ抵抗RLと、反転入力端子11がコンパレータ2の出力端子5に電気的に接続され、出力端子12がプルアップ抵抗RLの他端に電気的に接続され、非反転入力端子13にハイレベル出力電圧となる基準電圧V0が印加される増幅回路10と、を備えたものである。

(もっと読む)

波形整形回路

【課題】 複数のツェナーダイオードを用いることによって、簡易な構成で、所望の波形に変換できる波形整形回路を提供する。

【解決手段】 オルタネータGからの出力信号に基づいて、矩形状に信号変換された矩形波信号を制御手段2へ出力する波形整形回路において、アノード側に接続されたオルタネータGからの前記出力信号が所定レベル以上の電圧である場合に、カソード側からの電源出力によってハイレベルに設定し、前記矩形波信号として制御手段2が検出可能に接続される第1のツェナーダイオード3と、アノード側に接続されたオルタネータGからの前記出力信号が所定レベルよりも低い電圧である場合に、アノード側の電源出力を、カソード側の接地によってローレベルに設定し、前記矩形波信号として制御手段2が検出可能に接続される第2のツェナーダイオード4と、を備えてなる。

(もっと読む)

コンパレータ回路

【課題】簡単な構成で低消費電流化を図ることができ、しかも電源電圧の上昇に伴う消費電流の増加を抑制することのできるコンパレータ回路を提供する。

【解決手段】カレントミラー回路を構成するPMOSFET 11及びPMOSFET 12の各ソースは電源Vddに接続され、そのゲートは互いに接続される。ダイオード接続されているPMOSFET 11のドレインはNMOSFET 13のドレインに接続される。NMOSFET 13のゲートには信号V1が印加される。一方、PMOSFET 12のドレインはNMOSFET 14のドレインに接続される。またPMOSFET 12及びNMOSFET 14の各ドレインを結ぶ共通接続点から出力信号Voが導出される。NMOSFET 14のゲートには入力信号V2が印加される。そして、信号V1の値を定電圧素子によって決めることにより、電源電圧や入力信号V2が変わってもテール抵抗18の両端電圧が一定であるようにする。

(もっと読む)

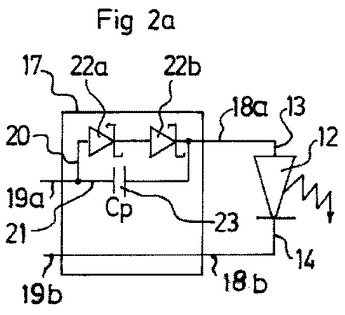

光電素子の超高速駆動用受動素子回路

本発明は、光電素子の超高速駆動回路において、時間400ps以下のエッジを有する電圧矩形波の発生器、ならびに、光電素子の電源端子(13)に直列に接続するように適合された出力、および、電圧矩形波発生器に接続され、そこで形成される電圧矩形波を受け取る入力を備える制御パルス成形回路(17)を含み、前記入力端子と前記出力端子の間に、ゼロでない閾値電圧を有する受動整流回路(22a、22b)からなる第1の分岐(20)であって、その受動整流回路(22a、22b)が第1の分岐内において直列をなし、光電素子の前記電源端子(13)に対して順方向をなす第1の分岐(20)と、第2の容量性分岐(21)とが互いに並列につながれていることを特徴とする駆動回路に関する。  (もっと読む)

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

電子スイッチ制御システム及び電子スイッチ駆動方法

本発明は、電子スイッチに電気的に接続される制御回路に基づいて、様々なタイプの負荷を駆動することができ、広く使用される電子スイッチに関する。制御回路は、本スイッチの少なくとも導通の時点で、制御回路に電力を供給するように設計された電圧レギュレータブロックに接続される。従って、少なくとも一つの交流電圧源(4)と、少なくとも一つの電子スイッチ(1)と、少なくとも一つの負荷(5)と、少なくとも一つの制御回路(3)とを備え、交流電圧源(4)は、第1の電力端子(20)を介して電子スイッチ(1)の第1の導通端子(25)と電気的に接続され、電子スイッチ(1)の第2の導通端子(35)は、第1の負荷端子(40)を介して負荷(5)と接続され、負荷(5)は、第2の負荷端子(80)を介して第2の電力端子(30)と接続され、制御回路(3)は、第1の電位端子(101)、第2の電位端子(102)及び第3の電位端子(103)を備え、制御回路(3)は、トリガー端子(100)を介して電子スイッチ(1)に命令を出すように配置され、制御回路(3)は、電圧レギュレータブロック(200)と電気的に接続され、電圧レギュレータブロック(200)は、第1の電気接続端子(104)及び第3の電気接続端子(106)と、第1の導通端子(25)及び第2の導通端子(35)とをそれぞれ介して電子スイッチ(1)と電気的に接続され、電圧レギュレータブロック(200)は、電子スイッチ(1)の少なくとも導通の時点で制御回路(3)を稼動するように、最小電圧(Vmin)を供給するように配置される、電子スイッチ制御システム(10)が記載される。 (もっと読む)

ゼロクロス検出装置及び画像形成装置

【課題】 低消費電力で駆動して交流電圧のゼロクロス点を検出することが可能なゼロクロス検出装置及び該ゼロクロス検出装置を有する画像形成装置を提供する。

【解決手段】

交流電圧のゼロクロス点を検出するゼロクロス検出装置において、交流電圧を整流して全波整流電圧を出力する全波整流手段と、全波整流電圧の印加で所定の充電電圧に充電され、全波整流電圧が充電電圧以下になると、充電電流を出力する充電手段と、充電電流の入力でゼロクロス検出信号を出力する信号出力手段とを含む。

(もっと読む)

交流電圧ゼロクロス検出回路、位相制御回路およびモータ制御装置

【課題】 電源電圧に影響されない安定した交流ゼロクロス信号を得る。

【解決手段】 フォトカプラ5の電流によって交流信号のゼロクロス信号波形を得る交流電圧ゼロクロス検出回路10。フォトカプラ5に、フォトカプラの入力側通電路に流れる電流を制御するトランジスタ4を接続し、トランジスタには、ツェナーダイオード6を接続する。ツェナーダイオードにより電流が分岐されるため、トランジスタがフォトカプラに流す電流が一定の値以下に制限されるが、ゼロクロス信号を得る電圧領域ではトランジスタは大きな増幅率を示し、電源電圧に依存しにくい交流ゼロクロス信号が得られる。

(もっと読む)

半導体素子制御装置

【課題】電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

(もっと読む)

波形改善回路

【課題】コンデンサに充電された電荷の放電タイミングを最適にし、高速信号に対応できるようにした波形改善回路を提供する。

【解決手段】信号線4に伝送されるデジタルの信号Stの波形を改善する波形改善回路1は、信号Stのレベルが所定値を超えたことをレベル検出回路11Aが検出すると、その出力電圧Vdに基づいてスイッチ回路12Aが導通状態になり、電源電圧VBを充電回路13Aのコンデンサ131に印加してコンデンサ131を充電する。信号Stの電圧レベルが、コンデンサ131の充電電圧Vcよりも低くなったタイミングでコンデンサ131から信号線4へ、放電回路14Aのダイオード141を介して放電が行われ、アンダーシュートが改善される。

(もっと読む)

電圧監視回路

【課題】 電源電圧の低下ばかりではなく、電源電圧の上昇に対しても被駆動回路をリセットして、被駆動回路の誤動作を防止することのできる電圧監視回路を実現する。

【解決手段】 電源電圧の大きさを検出して、その大きさが所定の範囲を超えた時に被駆動回路をリセットする電圧監視回路において、前記電源電圧を第1の基準値と比較して電源電圧が所定の基準レベルを下回った時に第1の比較出力を発生する低電圧検出回路と、前記電源電圧を第2の基準値と比較して電源電圧が所定の基準レベルを超えた時に第2の比較出力を発生する高電圧検出回路と、前記第1および第2の比較出力を受け前記被駆動回路のリセット信号を発生する論理回路とを具備したことを特徴とする。

(もっと読む)

1 - 11 / 11

[ Back to top ]