Fターム[5J039MM07]の内容

Fターム[5J039MM07]に分類される特許

1 - 17 / 17

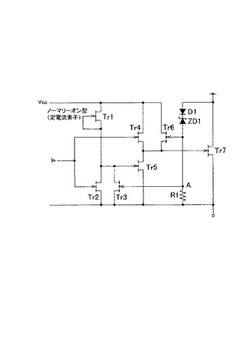

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

ピークホールド回路

【課題】一定期間内のピーク振幅を安定して保持することができるピークホールド回路を提供する。

【解決手段】変調された入力信号と該入力信号のDC電位とを入力して比較する第1の比較器2と、入力信号と所定の参照電圧とを入力して比較する第2の比較器2と、第1の比較器1からの出力と第2の比較器2からの出力とを入力し、AND出力結果に基づいて第2のスイッチ素子7をオン・オフ制御して、保持用コンデンサ5に入力信号のピーク振幅のDC電位を保持させる第2の論理回路(AND回路)4とを有している。

(もっと読む)

車載機器用二値信号処理装置

【課題】車両側から車載機器に入力される二値信号の高レベル/低レベルの電位が未知の場合であっても、前記二値信号の2つの状態を正しく弁別し、高レベル及び低レベルの状態に応じてパルス状に変化する出力側二値信号を生成する。

【解決手段】入力側二値信号SG1の波形のアナログレベルをデジタル情報に変換して入力し、このデジタル情報から第1のレベル(高レベル)と第2のレベル(低レベル)とを検出し、前記第1のレベル及び第2のレベルに基づいて少なくとも1つの閾値を決定し、前記閾値に応じて基準レベル生成部の状態を自動的に調整するマイクロコンピュータ11と、前記基準レベル生成部に配置され前記マイクロコンピュータ11からのデジタル制御入力に従って抵抗値が決定される少なくとも1つのデジタルポテンショメータ16、17とを備える。

(もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

単位回路および電子回路

【課題】出力回路における各トランジスタのゲート・ソース間に印加される電圧を制限するための構成や単位回路へ入力される制御信号の振幅を小さくするための構成を簡素化する。

【解決手段】単位回路Jは、電源線101と接地線103との間に直列に接続された第1のPチャネルトランジスタ、第2のPチャネルトランジスタ、第1のNチャネルトランジスタ、および第2のNチャネルトランジスタとを備える。そして、第1のPチャネルトランジスタがオン状態のときにその電位がVDDとなり、第1のPチャネルトランジスタがオフ状態のときにその電位がVREF+Vtp2となる第1出力信号V1を第1出力端子から出力し、第2のNチャネルトランジスタがオン状態のときにその電位がGNDとなり、第2のNチャネルトランジスタがオフ状態のときにその電位がVREF−Vtn1となる第2出力信号V2を第2出力端子から出力する。

(もっと読む)

パルスディテクタ

【課題】プラズマを発生させるようなQ値の高い負荷が接続され、パルス幅変調において高周波信号が出力される場合、信号レベルの減衰が遅くとも、サンプルホールド信号を発生させ、高周波信号の信号レベルをホールドするパルスディテクタを提供する。

【解決手段】本発明は、高周波信号の電圧の包絡波形の電圧レベル信号を出力する電圧レベル検出部と、電流の包絡波形の電流レベル信号を出力する電流レベル検出部と、電圧と電流の位相差を求める位相差検出部と、包絡波形が一端途切れ、その後出力される包絡波形の立上りを、包絡波形の信号レベルと設定された閾値とを比較して検出し、立上り信号を出力する入力検出部と、立上り信号の入力後にサンプルホールド信号を出力する制御部と、電圧レベル信号、電流レベル信号及び位相差信号の信号レベルをホールドするサンプルホールド回路を有し、閾値は、直前の包絡波形の信号レベルの設定された割合の数値である。

(もっと読む)

ディザ処理型クロック発生器

【課題】 位相分解能を高くし周波数スペクトラムのピークを低減したスペクトラム拡散クロック発生器を提供する。

【解決手段】 本発明のスペクトラム拡散クロック発生器100は、基準クロック信号と帰還クロック信号の位相差を検出する位相比較器20、チャージポンプ22、ループフィルタ24、多相のクロック信号を発生する多相VCO22、多相VCO26からの隣合う位相のクロック信号の位相を補間する位相補間部120、位相補完部120の位相選択を制御する位相選択部130、一定のステップ幅で段階的に変化する1周期分の変調波形データを記憶する変調データ部140、ディザステップ信号DSを出力するディザ処理部150、変調波形データとディザステップ信号を加算する加算器160を有する。位相選択部130は、ディザステップ信号が加算された変調波形データに基づき位相の補間を行う。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、しきい値電圧を決定する参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、前記基準電圧を基準とした、検出すべき電圧を入力する第4の端子と、前記第1、第2の端子を制御端子に接続され、前記参照電圧の電位差に応じた電流をそれぞれ流す、第1導電型の第1、第2のトランジスタと、前記第1のトランジスタと前記第4の端子との間に接続される第2導電型の第3のトランジスタと、前記第2のトランジスタと前記第3の端子との間に接続され、前記第3のトランジスタの流す電流に応じたミラー電流を流す第2導電型の第4のトランジスタと、を有し、前記第2、第4のトランジスタの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

高電圧、高速、高パルス繰返し数のパルス発生器

【課題】RF電力増幅器と関連する高パルス繰返し数の制限を解決する高電圧、高速、および高繰返し数パルス発生器(30)を提供する。

【解決手段】パルス発生器(30)は共振技術を利用して、短絡および開回路の双方の負荷状態中に、パルス発生器(30)の機能障害なしに、パルス発生器(30)の継続的な高電圧、高速、および高繰返しパルス数動作を可能にする電流制限特徴をもたらす。本発明の好適な実施例において、パルス発生器(30)は、DC電圧を高周波AC電圧に変換するように構成されているインバータ(40)と、前記AC電圧に応答して、AC電流源として動作するように構成されているコンバータ(50)と、前記AC電流源によって発生するAC入力電流に応答して、高電圧、高速、高繰返し数電圧パルスを発生させるように構成されているパルス整形部分(60)とを備える。

(もっと読む)

バッファ回路、増幅回路、および、試験装置

【課題】出力信号の信号レベルを、設定されるクランプ電圧に応じて精度よく制御するバッファ回路を実現する。

【解決手段】入力信号に応じた信号を出力するバッファ回路であって、入力信号をベース端子に受け取る第1受信トランジスタと、エミッタ端子およびコレクタ端子が第1受信トランジスタの対応する端子に接続され、バッファ回路が出力する信号レベルを制限する第1クランプ電圧をベース端子に受け取る、第1受信トランジスタと同一極性の第1クランプトランジスタと、第1受信トランジスタおよび第1クランプトランジスタに対して共通に設けられ、第1受信トランジスタおよび第1クランプトランジスタに流れるエミッタ電流の総量を規定する第1電流規定部とを備え、第1受信トランジスタのエミッタ電圧に応じた出力信号を出力するバッファ回路を提供する。

(もっと読む)

デジタル型ヘリウム−ネオン安定化レーザ

【目的】 安定化のために、デジタル量を用いる安定化ヘリウム−ネオンレーザの高度の安定度をうるため、デジタルのパルスの形状を正確に揃える手段の提供を行なうと共に、前記安定化のためのデジタル量のパルスの周波数を正確に一定にする手段の提供を行なうことを目的とする。

【構成】

レーザから安定化のために使用出来るデジタル量のパルス周波数を、基準周波数を完全に、しかも安定に一致させるため、ダイオードの順方向の電圧を利用して、正負のパルスの基線を零ボルトにし、さらに、このデジタル量をアナログ量に変換する際、F/V変換回路と正負のパルスの電荷をゆっくり積分する回路を並列にして誤差信号の値を完全に零にしている。

(もっと読む)

ピーク検出回路

【課題】出力信号の低下を抑えることが可能なピーク検出回路を提供することを目的とする。

【解決手段】NチャネルのMOSFET2に並列接続されるPチャネルのMOSFET4のソース端子と電源電圧VDDが印加される端子10との間に抵抗6を接続し、NチャネルのMOSFET3に並列接続されるPチャネルのMOSFET5のソース端子と電源電圧VDDが印加される端子10との間に抵抗7を接続し、MOSFET2、5のそれぞれのゲート端子に入力信号INPを入力し、MOSFET3、4のそれぞれのゲート端子に入力信号INPの反転信号INNを入力する。

(もっと読む)

波形改善回路

【課題】コンデンサに充電された電荷の放電タイミングを最適にし、高速信号に対応できるようにした波形改善回路を提供する。

【解決手段】信号線4に伝送されるデジタルの信号Stの波形を改善する波形改善回路1は、信号Stのレベルが所定値を超えたことをレベル検出回路11Aが検出すると、その出力電圧Vdに基づいてスイッチ回路12Aが導通状態になり、電源電圧VBを充電回路13Aのコンデンサ131に印加してコンデンサ131を充電する。信号Stの電圧レベルが、コンデンサ131の充電電圧Vcよりも低くなったタイミングでコンデンサ131から信号線4へ、放電回路14Aのダイオード141を介して放電が行われ、アンダーシュートが改善される。

(もっと読む)

振幅制御回路

【課題】 個体やIC面内のばらつきがあっても増幅回路の出力振幅を一定にする。

【解決手段】 増幅回路100からのパルス出力信号がコンパレータ1の−側入力端子とコンパレータ2の+側入力端子、出力信号のハイレベルに対応するVref20がコンパレータ1の+側入力端子、出力信号のロウレベルに対応するVref21が−側入力端子に接続される。/EX-OR3はコンパレータ1とコンパレータ2の出力が同レベルのときにハイレベルを出力する。LPF4は出力信号の振幅が小さ期間においては、/EX-OR3からのハイレベルが入力するとハイレベルとロウレベルの中間レベルに向かって進む信号を出力し、電圧参照回路5はLPF4の出力に応答して電流源の電流を増減するための参照電圧を電流源8に供給する。

(もっと読む)

1 - 17 / 17

[ Back to top ]