Fターム[5J039MM15]の内容

Fターム[5J039MM15]に分類される特許

1 - 20 / 23

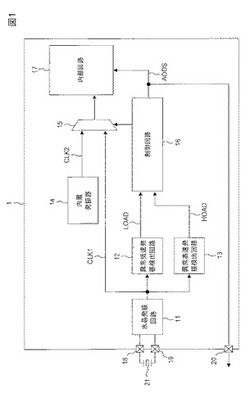

周波数変換回路

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

PWMコントローラーのフェーズ調節システム及びフェーズ調節方法

【課題】PWMコントローラーの使用寿命を延長できるPWMコントローラーのフェーズ調節システム及びフェーズ調節方法を提供すること。

【解決手段】本発明に係るPWMコントローラーのフェーズ調節システムは、マイクロコントローラー、多相PWMコントローラー及び前記多相PWMコントローラーによって前記マイクロコントローラーに接続される制御しようとする部品を備えてなる。前記マイクロコントローラーは、毎回システムが起動されて初期化プログラムを実行する際、前記多相PWMコントローラーが提供したデフォルトフェーズの作動時間が予定値より大きいか否かを計算し、且つ前記デフォルトフェーズの作動時間が予定値より大きければ、前記多相PWMコントローラーが提供するデフォルトフェーズを変更して、前記多相PWMコントローラーが提供する各々フェーズの作動時間を大体に均衡させる。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

回転方向判別装置

【課題】 第1のパルス信号が第2の値に反転する時刻と、第2のパルス信号が第2の値に反転する時刻との間の時間が短い場合であっても、正確にロータリースイッチの回転方向を判別すること。

【解決手段】 パルス信号A及びパルス信号Bの一方がローレベルに反転してから、他方のパルス信号がローレベルに反転するまでの時間が所定時間未満である場合、パルス信号A及びパルス信号Bのうち、どちらのパルス信号が先にハイレベルからローレベルに反転したかによって回転方向を判別せずに、どちらのパルス信号が先にハイレベルからローレベルに反転したかによって回転方向を判別する。従って、回転方向を正確に判別することができる。

(もっと読む)

電圧制御発振回路

【課題】動作が誤発振状態または準安定状態となったことを検出し、誤発振状態または準安定状態から抜け出して正常な発振状態にとすることができるVCOをを提供する。

【解決手段】本発明の電圧制御発振回路は、互いに逆相の差動のクロック信号が入力される差動遅延素子を縦続接続し、バイアス電圧によって差動遅延素子に流れる電流の量を制御することで、該差動のクロック信号の遅延量を制御する差動リングオシレータ型の電圧制御発振回路であり、いずれかの差動遅延素子の差動出力の出力電圧と、異常動作を検出する電圧に設定されたリファレンス電圧とを比較することにより異常発振を検出して検出信号を出力する位相検出部と、差動遅延素子毎に設けられ、検出信号が入力されると、差動出力対間の電位差を増幅するクロスカップル回路とを有している。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

PLL回路および記録情報再生装置

【課題】PD出力から微分値を求めると、平均値が“0”の周期関数の微分の平均値はやはり“0”となり、上下バランスが崩れた位相誤差検出特性が得られない。

【解決手段】加算器4203の加算結果ADDである位相誤差絶対値を絶対値比較器4205でしきい値Vthと比較し、当該位相誤差絶対値がしきい値Vthを超えた時点でのPHERR信号の極性と、現時点でのPHERR信号の極性とを不一致検出回路4208で比較する。そして、不一致のときにビットスリップが起きたと判断し、現時点でのPHERR信号の極性を極性反転回路4210で反転し、最終的なPD出力とすることで、上下バランスが崩れた位相誤差検出特性を実現する。

(もっと読む)

ビデオアンプ

【課題】ビデオアンプにおける非活性ラインのエミッタフォロアのベースエミッタ逆バイアスを排除する。

【解決手段】モード制御信号2によりスルーモード時には、ダイオード9が活性ライン側(エミッタフォロア13のベース)の電位をVf だけシフトダウンし、スイッチ10はVf シフトを非活性ライン側(エミッタフォロア14のベース)に伝達する。また、ローパスフィルタモード選択時には、ダイオード12が活性ライン側(エミッタフォロア14のベース)の電位をVf だけシフトダウンし、スイッチ11はVf シフトを非活性ライン側(エミッタフォロア13のベース)に伝達する。これにより、エミッタフォロア14または13のベースとエミッタが同電位になる。

(もっと読む)

クロックツリー合成装置、クロックツリー合成方法、制御プログラムおよび可読記録媒体

【課題】複数のクロック信号源と、複数のクロック信号源が各入力端子に接続された論理回路との各クロック出力について、同期関係を解析してクロックツリーを最良に生成する。

【解決手段】複数のクロック信号源と、この複数のクロック信号源が各入力端子に接続された論理回路との各クロック出力について、クロック同期関係解析手段10によって、同期関係を解析し、この解析結果に基づいて、クロックツリー構成手段20によって、クロックツリーを生成するため、クロックツリーを再構成することなく、クロックスキューを低減することができる。また、論理回路からクロックが供給されるクロック同期素子(フリップフロップ)が、どちらの信号源に同期して動作するかが分かるため、クロックスキューが小さく、消費電力が少ないクロックツリーを簡単に構成してタイミング違反による回路誤動作を防ぐことができる。

(もっと読む)

半導体装置

【課題】

従来の半導体装置では、簡単な回路でソフトエラーを検出し、エラーの伝播を防ぐことが困難であった。

【解決手段】

本発明にかかる半導体装置は、複数の論理回路を直列に接続した発振回路10と、複数の論理回路のうち少なくとも2つ以上の論理回路の出力信号が入力され、前記出力信号の間の位相差が所定の位相差の範囲外となる場合に発振回路10を一時停止させ、他のブロックに発振回路10にエラーが発生したことを通知するリセット信号を出力するエラー検出回路20とを有するものである。

(もっと読む)

半導体集積回路

【課題】多雑音環境であったり、サンプリング周期に同期して雑音が発生しやすい状況下においても、その雑音信号を誤入力しない半導体集積回路を提供する。

【解決手段】半導体集積回路は、サンプリング部と、遅延部と、第1演算部と、第2演算部とを具備する。サンプリング部は、外部から入力される入力信号をクロック信号に同期してサンプリングし、第1信号として出力する。遅延部は、第1信号をクロック信号に基づいて遅延させ、第2信号として出力する。第1演算部は、第1信号と第2信号に基づいて、入力信号が所定の時間以上信号レベルが持続しているか否かを演算する。所定の時間以上信号レベルが持続するとき、第1演算部は、所定の時間以上持続する信号レベルを有する出力信号をクロック信号に同期して出力する。第2演算部は、入力信号と出力信号とに基づいて、サンプリング部を非同期に制御する。

(もっと読む)

1 - 20 / 23

[ Back to top ]