Fターム[5J039NN00]の内容

パルスの操作 (9,993) | 用途 (378)

Fターム[5J039NN00]の下位に属するFターム

Fターム[5J039NN00]に分類される特許

1 - 20 / 21

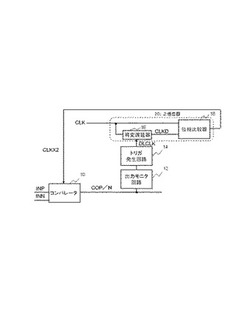

半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

コンパレータおよびそれを用いたDC/DCコンバータの制御回路、電子機器

【課題】コンパレータを小型化、および/または、低消費電力化する。

【解決手段】第1電圧V1と第2電圧V2を比較するコンパレータ10が提供される。デプレッション型PチャンネルMOSFETの第1トランジスタM1のソースには、第1電圧V1が、そのゲートには、第2電圧V2が印加される。デプレッション型PチャンネルMOSFETの第2トランジスタM2のソースおよびゲートは、第1トランジスタM1のドレインと接続され、第2トランジスタM2のドレインの電位は固定される。コンパレータ10は、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1に応じた出力信号OUTを生成する。

(もっと読む)

時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

(もっと読む)

ポップ音のしないスイッチ

【課題】スイッチに関し、より具体的には、2つ以上の入力の間でスイッチを切り換える際にポップ音等の好ましくない効果を低減できる方法及び装置を提供する。

【解決手段】スイッチ130は、第1の入力110で第1の信号を受取り、そのスイッチ130の状態により、出力120において出力信号を供給することができるように構成される。スイッチ状態変化は、現在のスイッチ状態とは異なる、要求されたスイッチ状態の指示115が受取られ、その第1の信号がしきい値に達するまで、遅らせることが可能である。

(もっと読む)

パルス生成回路およびミュート装置

【課題】 矩形波信号の立ち上がりエッジおよび立ち下がりエッジを検出し、一方のレベルのパルス信号を生成するパルス生成回路において、トランジスタの数を削減すること。

【解決手段】 立ち下がりエッジ検出部2は、矩形波信号の立ち下がりエッジを検出し、所定時間だけ、トランジスタQ1をオン状態に制御する。立ち上がりエッジ検出部は、矩形波信号の立ち上がりエッジを検出し、所定時間だけ、トランジスタQ2をオン状態に制御する。トランジスタQ1は、立ち下がりエッジ検出部2が矩形波信号の立ち下がりエッジを検出した時から所定時間、および、トランジスタQ2がオン状態である期間に、オン状態になり、ハイレベルのパルスを出力する。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

同期信号発生回路

【課題】 PWM信号からその同期信号を発生する。

【解決手段】 三角波発生回路101は、PWM信号PWMINの立ち上がりエッジおよび立ち下がりエッジの各々を検出する度に、先行して開始した三角波信号の発生と並行して三角波信号を発生する手段であり、立ち上がりエッジまたは立ち下がりエッジの検出後、三角波信号を基準レベルから一定の時間勾配で変化させ、その後、同種のエッジが検出された以降、同じ大きさの逆方向の時間勾配で三角波信号を変化させる。同期信号発生部160は、三角波発生回路101が発生する三角波信号TRIA、TRIB、TRICに基づいてPWM信号PWMINに同期した同期信号SYNCを発生する手段であり、相前後して発生を開始した2個の三角波信号の大小関係が逆転したとき、同期信号SYNCのレベルを反転させ、先行して発生を開始した三角波信号を基準レベルに初期化する。

(もっと読む)

ラッチ回路を有する信号処理装置

【課題】 ラッチ回路がノイズによって誤動作することがある。

【解決手段】

信号処理装置は、セットパルス発生回路3と、リセットパルス発生回路5と、ラッチ回路4との他に補正セットパルス形成回路30を有する。補正セット信号形成回路30は、セットパルスからリセットパルスまでの時間幅にほぼ対応する補正セット信号を形成してラッチ回路4に送る。ラッチ回路4はノイズによってリセットされても補正セット信号によって再びセットされる。

(もっと読む)

デューティ補正装置

【課題】同一の符号化方式で符号化され、かつ伝送速度が任意の複数種存在する受信信号のいずれに対してもデューティ比を補正可能にする。

【解決手段】符号化された受信信号の“H”または“L”の継続時間を観測する観測手段と、受信信号の符号シンボル周期に関する長パルス用設定値と短パルス用設定値に基づいて、観測された“H”または“L”の継続時間から波形歪みを検出する波形歪み検出手段と、波形歪みが検出された場合に、波形歪み発生期間の受信信号を反転することにより波形の補正を行う波形補正手段と、受信信号の立上りまたは立下りを検出し、その次の立上りまたは立下り検出までの間隔に基づいて判定した現在の受信信号の符号シンボル周期に基づいて上記長パルス用設定値と短パルス用設定値を設定する符号シンボル周期判定手段を備えた。

(もっと読む)

光センサ回路および光センサアレイ

【課題】光センサ回路のレイアウト面積を増大させることなく、光センサ回路の消費電流を一定に保ち、熱平衡状態を維持することのできる光センサ回路および光センサアレイを提供する。

【解決手段】光センサ回路は受光した光量に応じた値の光電流を生成する光電変換手段,増幅回路,増幅回路の入出力端子間に接続されて前記光電流を積分するコンデンサおよびコンデンサの両端に接続されたリセットトランジスタを有し、リセットトランジスタを待機モードでオンさせる。また、この光センサ回路を複数有する光センサアレイについても適用できる。

(もっと読む)

電力変換装置および電力変換方法

【課題】所望の周波数帯域におけるノイズスペクトルを平坦化することができる電力変換装置および電力変換方法を提供することにある。

【解決手段】

インバータシステム1は、入力される電力を所望の形態に変換するスイッチング素子の開閉動作をデジタル制御する、演算装置を有する制御装置10は、スイッチング素子を開閉するための制御信号を生成する比較器8a、8b、8cに出力するキャリア信号の周波数fcを、離散的かつ周期的に時間変化させるキャリア周波数生成部9を備えている。キャリア周波数生成部9は、キャリア周波数fcの値fc11におけるm11次高調波の周波数m11×fc11と、キャリア周波数fcの他の値fc12におけるm12次高調波の周波数m12×fc12とが、演算装置のクロック周波数Fより低い周波数で重畳しないように、キャリア周波数fcの各値fc11およびfc12を選択した。

(もっと読む)

浮遊抵抗体ラダーを用いたインバータベースのフラッシュA/D変換器

【課題】低消費電力などのインバータベースのフラッシュADCの特徴を保有する一方、インバータのサイズまたはパラメータを変えないでインバータ不整合を指示するフラッシュADCを持つことが望まれる。

【解決手段】アナログ信号をデジタル信号に変換するA/D変換器であり、複数の比較器を含む比較器アレーと、直列に接続された複数の抵抗を含む抵抗列と、抵抗列に流れる一定の電流を与えるための電流発生器とを備え、前記比較器の各々は第1のインバータおよび第1のインバータと直列に接続された第2のインバータを含み、前記抵抗器の各々は複数の比較器の1つに対応することを特徴とする。

(もっと読む)

電流スイッチング回路、レーザー駆動回路および記録再生装置

【課題】光ディスク記録装置には、発光素子を駆動するレーザーダイオード(LD)ドライバが用いられる。レーザーダイオードは、経時変化にて劣化しやすく、長寿命化のためには、LD駆動装置の大電流化が求められている。しかしながら、大電流を駆動するLDドライバは、グリッジ、サグといった電流波形の異常(誤差)を生じやすく、データ記録上の信頼性に問題があった。

【解決手段】カレントミラーを構成するMOSトランジスタのソース側にスイッチとなるMOSトランジスタを備え、スイッチとなるMOSトランジスタから生じる変位電流を、電源、スイッチ−出力トランジスタ間と、カレントミラーのゲート間に備えたダミーMOSトランジスタによりキャンセルすることで、グリッジ、サグを低減、もしくは除去する。それらにより、大電流の電流スイッチング回路においても、理想的な電流矩形波形を得ることができる。

(もっと読む)

高速パルスの生成装置及び高速パルスの生成方法

【課題】局部発振器を介して出力された比較的低い周波数のパルスを用い、比較的安価に高速パルスを生成できるとともに、任意の数のパルス数を有するパルス列を生成できる高速パルスの生成装置を提供することを目的とする。

【解決手段】S103で、局部発振器から出力されるパルス列を逓倍する第一の逓倍数を設定し、S104で、駆動量の指令値を第一の逓倍数で除算して整数解と余数を算出し、S107、S112で、整数解のパルス数を有するパルス列を出力すると共に、余数のパルス数を有するパルス列を出力し、S108、S113で、整数解のパルス数を有するパルス列を第一の逓倍数で逓倍して第一の逓倍パルス列を生成すると共に、余数のパルス数を有するパルス列を逓倍数1で逓倍して第二の逓倍パルス列を生成し、S115で、第一の逓倍パルス列に前記第二の逓倍パルス列を加えて、出力パルス列を生成する。

(もっと読む)

マイクロコンピュータ

【課題】温度が変化する環境下において、CR発振回路の発振出力に基づいて行われる所定の処理時間が一定となるように補正する構成を、より簡単に実現するマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータのEEPROMに、温度により変動するCR発振回路の発振出力特性に基づき、通信回路により管理される1フレームのデータ送信時間を一定とするための通信レートCMRを決定するデータを記憶しておく。CPUは、温度検出回路によって検出される温度(ステップS2)に応じてEEPROMに記憶されているデータを読み出し(ステップS3)、決定した通信レートCMR(ステップS4)を通信回路に設定する(ステップS5)。

(もっと読む)

絶縁型電圧検出回路

【課題】回路構成が単純で、廉価な部品のみにより構成される、簡易的な絶縁型電圧検出回路を提供する。

【解決手段】レジスタ1に設定されたデータに比例したパルス幅の第1のPWM信号を出力するパルス幅変調回路2と、その出力を絶縁して第2のPWM信号として出力する第1の絶縁手段3と、第2のPWM信号をアナログ電圧信号aに変換する変換回路4と、アナログ電圧信号aと検出対象であるアナログ電圧信号bを比較し、2つの極性をもつ比較信号を出力する比較器5と、その比較信号を絶縁して2つの極性を有する第2の比較信号cとして出力する第2の絶縁手段6とを備え、第2の絶縁手段6から出力される第2の比較信号cの結果を所定の周期で検出し、アナログ電圧信号aと検出対象であるアナログ電圧信号bが等しくなるように、レジスタ1に設定するデータをCPU7により増減させるようにした絶縁型電圧検出回路。

(もっと読む)

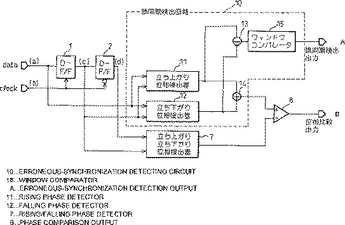

位相誤同期検出回路

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

データ読取装置および車載機器無線制御システム

【課題】 少ないCPU負担で、受信信号からデータを読み取る事ができるデータ読取装置を提供する。

【解決手段】 このデータ読取装置は、複数ビット周期Tp,Tdを繰り返し周期とするパルス信号列を含む受信信号9から前記パルス信号列に乗せられたデータを読み取るものであり、受信信号9の複数ビット周期Tp,Tdの特定ビット部分(例えば2ビット目部分)をサンプリングするサンプリング手段と、前記サンプリング手段のサンプリング結果に基づいて受信信号9に乗せられた前記データを読み取るデータ読取手段とを備える。

(もっと読む)

車載用コンパレータ回路

【課題】 電源電圧の変動により誤パルスを出力することがない車載用コンパレータ回路を提供する。

【解決手段】 電源電圧Vcの変動に対して差動増幅器OP1からの出力が鈍化(鈍る)して変動しコンパレータCPの信号入力端子Csに加えられる。一方、コンパレータCPの基準電位入力端子Crに加えられる基準電位Vrefも波形鈍化回路20により鈍化(鈍る)して変動する。このため、コンパレータCPから誤パルスが出力されることが無くなる。

(もっと読む)

ダイオード回路

【課題】

小面積で集積可能なダイオード回路を形成することは困難であった。

【解決手段】

本発明のダイオード回路は、ソースが第1の入力端子に接続された第1のMOSトランジスタと、ソースが第2の入力端子に接続され、ゲートおよびドレインが前記第1のMOSトランジスタのゲートに接続された第2のMOSトランジスタ、および前記第1のMOSトランジスタのドレインに接続された第1の抵抗性負荷を有する差動回路と、前記差動回路の出力に基づいて導通状態が制御される第3のMOSトランジスタとを有している。

(もっと読む)

1 - 20 / 21

[ Back to top ]