Fターム[5J039NN06]の内容

Fターム[5J039NN06]に分類される特許

1 - 20 / 99

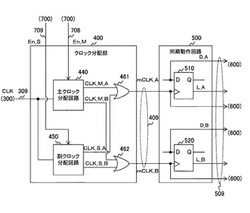

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

位相調整回路及び半導体装置

【課題】回路規模を増やすことなく、スキュー調整及び位相調整を実現する。

【解決手段】本実施形態の本実施形態の位相調整回路12は、第1クロック信号と第2クロック信号との位相差に応じて動作する。位相調整回路12は、調整用駆動素子120と、駆動素子121及び122とを備える。調整用駆動素子120は、入力信号を駆動させ、調整信号を生成する。駆動素子121及び122は、第1クロック信号と第2クロック信号との間に位相差が生じた場合、調整信号と並行した同相及び/又は逆相のクロストーク信号を生成する。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

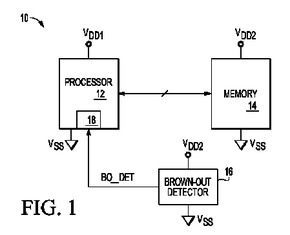

ブラウンアウト検出回路を有するデータ処理システム

ブラウンアウト検出回路(16)は、第1抵抗素子(38)と、第1トランジスタ(46)と、第2トランジスタ(50)と、比較器(40)とを備える。第1抵抗素子(38)が、第1電源電圧端子および第2端子に接続される第1端子を有する。第1トランジスタ(46)は、第1導電性タイプであり、第1抵抗素子(38)の第2端子に接続される第1電流電極と、制御電極と、第2電流電極とを有する。第2トランジスタ(50)は、第2導電性タイプであり、第1トランジスタ(46)の第2電流電極に接続される第1電流電極と、制御電極と、第2電源電圧端子に接続される第2電流電極とを有する。比較器(40)は、第1抵抗素子(38)の第1端子に接続される第1入力端子と、第1抵抗素子(38)の第2端子に接続される第2入力端子と、ブラウンアウト検出信号を供給するための出力端子とを有する。  (もっと読む)

(もっと読む)

半導体集積回路の設計方法及びプログラム

【課題】タイミング制約を満たすためにセルの物理的な位置やRTL(Register Transfer Level)を変更する必要がなく、回路の最適化を短時間に行うことができ、半導体集積回路の設計期間を短縮することができる半導体集積回路の設計方法、設計プログラムを提供する。

【解決手段】半導体集積回路のネットリストに対して静的タイミング解析を行うことにより、所定のタイミング制約を満たさないタイミングエラーパスを検出し、前記タイミングエラーパスを含む第1の論理ブロックと、フリップフロップを介して前記第1の論理ブロックに接続され、所定のタイミング制約を満たす第2の論理ブロックとを抽出し、前記第1の論理ブロックと前記第2の論理ブロックとの間のフリップフロップが正相/逆相フリップフロップである場合は、当該正相/逆相フリップフロップを逆相/正相フリップフロップに変更する。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

ビット配列入れ替え半導体回路

【課題】基板上で接続されたマイコンとROM、RAMのデータのやりとり及びROM、RAMの内容を解析しづらくする。

【解決手段】

基板上で接続されたマイコンとROM、RAMを接続するデータバスに、スイッチング素子1を配置したビット配列入替回路を設け、アドレスバスの一部と、RAMまたは電気的に書き換え可能なROMとして実現されるメモリ3の内容を用いて、組み合わせ回路であるビット配列入替スイッチ駆動回路2により各スイッチング素子1のオンオフを決定することにより、データバスのビット配列の入替を行う。

(もっと読む)

デューティ検出回路及びこれを備えるクロック生成回路、並びに、半導体装置

【課題】デューティ検出信号を高頻度に更新する。

【解決手段】内部クロックRCLK,FCLKのデューティを検出する複数のデューティ検出部210−1〜210mと、複数のデューティ検出部を互いに異なる位相で動作させる制御部220と、複数のデューティ検出部からのデューティ検出信号を選択する出力選択部230とを備える。本発明によれば、複数のデューティ検出部が互いに異なる位相で動作することから、各デューティ検出部におけるデューティ検出信号の生成頻度よりも高頻度でデューティ検出信号DCCSを出力することが可能となる。このため、本発明によるデューティ検出回路をDLL回路のクロック調整に使用すれば、DLL回路の制御周期を短縮することが可能となる。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

昇圧回路、および降圧回路

【課題】入力電圧を昇圧して出力する半導体集積回路における、トランジスタの耐圧が、入力電圧以下に抑えられる昇圧回路を提供する。

【解決手段】コンデンサCpは、一方の端子がクロック信号を出力するクロック端子に接続され、他方の端子が整流回路4に接続されている。コンデンサCpの他方の端子の最低電圧を第1の電圧にクランプするクランプ回路3を備えている。このクランプ回路3は、第1のN型トランジスタN1、および第2のN型トランジスタN2を有している。この第1のN型トランジスタN1は、ドレインをコンデンサの他方の端子に接続し、ソースを前記第2のN型トランジスタN2のドレインに接続し、さらに、ゲートを第1の電圧よりも高い第2の電圧Vaに接続している。また、第2のN型トランジスタN2は、ソースを第1の電圧Vpに接続し、ゲートを前記クロック信号の反転信号を出力する反転信号端子に接続している。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

1 - 20 / 99

[ Back to top ]