Fターム[5J043BB02]の内容

Fターム[5J043BB02]に分類される特許

1 - 20 / 41

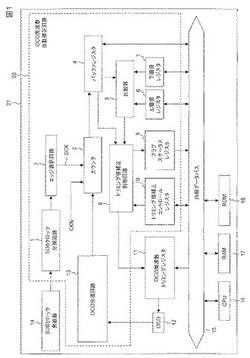

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

ディジタル発振器

【課題】ルックアップテーブル方式のようなメモリを使用せずに、正弦波、余弦波、角度情報が同時に得られるようにしたディジタル発振器を提供する。

【解決手段】初期値Aが設定されクロックで動作する第1の積分器5A、外部入力するアップ/ダウン信号でωの極性が切り替わる第1のω係数器6B、前記クロックで動作する第2の積分器5B、および前記アップ/ダウン信号でωの極性が前記第1のω係数器6Bのωの極性と反対に切り替わる第2のω係数器6Aを順次リング接続して2相発振器を構成する。また、前記アップ/ダウン信号に応じて前記クロックをアップ/ダウンカウントするアップ/ダウンカウンタからなる角度取得ユニット3を設ける。前記第1の積分器5AからAcosωtを、前記第2の積分器5BからAsinωtを、前記角度取得ユニット3から角度情報ωtを、それぞれ同時に生成する。

(もっと読む)

発振回路

【課題】共振部とインバータを並列接続する発振回路では、インバータのトランスコンダクタンスが発振周波数に拘わらず一定なので、スプリアスへの収束を回避することが難しい。本発明はスプリアスへの収束を回避できる発振回路を提供することを目的にする。

【解決手段】インバータの入力信号の遷移点(立ち上がり、立ち下がり)で一定幅のパルス信号を出力するワンショット回路を用い、このワンショット回路のパルス幅がインバータへの入力信号のパルス幅より大きいときに、インバータへの電源供給を停止するようにした。スプリアスではトランスコンダクタンスの時間平均が小さくなり、発振が持続しない。

(もっと読む)

可変抵抗回路および発振回路

【課題】回路規模を比較的小さくすることができ且つ高精度な抵抗値調整が可能な可変抵抗回路を提供し、また、かかる可変抵抗回路を用いた比較的回路規模が小さく高精度な発振周波数を実現し得る発振回路を提供する。

【解決手段】

可変抵抗回路は、複数の抵抗素子からなる第1の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路の所定のノードのうちの1つを選択的に第1の端子に接続せしめる第1のスイッチ部と、を有する第1の抵抗調整回路と、第2の端子に接続された複数の抵抗素子からなる第2の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路を第2の直列抵抗回路の所定ノードのうちの1つに選択的に接続せしめる第2のスイッチ部と、を有する第2の抵抗調整回路と、を含む。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

発振周波数補正方法及び発振周波数補正装置

【課題】電子製品の発振周波数を正確に補正するために用いる発振周波数補正方法を提供する。

【解決手段】発振周波数補正方法は、発振周波数に対応するクロック信号を生成するアジャスタブル周波数生成ユニットを有する電子製品の発振周波数を補正するために用いる。発振周波数補正方法は、標準周波数報時局から発信された時間電波信号を受信する上、前記時間電波信号を対応する複数のパルス信号に変換するステップS1と、前記複数のパルス信号及び前記クロック信号を演算し、対応する制御信号を生成するステップS2と、前記制御信号を利用することにより、前記アジャスタブル周波数生成ユニットが生成する前記クロック信号を調整し、対応する前記発振周波数を補正するステップS3と、を含む。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

半導体集積回路装置

【課題】ノーマルなクロックとSSCとを生成するクロック発生回路における回路面積を低減しながら、高精度のSSCを生成する。

【解決手段】電圧制御発振器から出力されたクロック信号vco1は、分周器13によって分周され、分周クロックph0としてセレクタ15に出力される。分周器13は、制御回路12の制御信号Pconに基づいて、周期の1/mずつ位相のシフトした分周クロックph1〜phmを出力する。セレクタ15は、分周クロックph0〜phmのうち、最も近い位相シフトをもつ2つの分周クロックphj,phj+1を選択する。位相補間回路16は、制御回路12から出力される重み付けデータ信号Aに基づいて、分周クロックphj,phj+1間の位相差の間を更に細分化した位相シフト量で位相シフトさせ、出力クロックfout1として出力する。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振回路およびそれを用いたスイッチング電源装置

【目的】スイッチング周波数を変えてもオン期間Tonの生成精度に影響を与えることがない発振回路、およびそれを用いたスイッチング電源装置を提供する。

【構成】この発明の発振回路は台形波を生成し、発振回路外部からの制御信号により台形波が所定時間同じ値を保持する第2期間の所定時間を変更して台形波の周期を可変とするので、それぞれの周期における台形波の立ち上がりおよび立ち下りの傾きを一定にできる。従い、この発明の発振回路を用いたこの発明のスイッチング電源装置が台形波と誤差信号からスイッチング素子のオン期間Tonを生成するとき、スイッチング周波数が変わってもオン期間Tonの生成精度を一定に保つことができる。

(もっと読む)

発振回路

【課題】従来のゲート発振器のゲート発振器と入力信号間に内在する周波数オフセットの効果的な校正技術を提供する。

【解決手段】発振回路200は、ゲート発振器201と較正回路202とを備える。ゲート発振器201は、制御信号Sctrlに従って発振信号を生成し、ゲート信号SGを受信して、発振信号のエッジとゲート信号SGのエッジを配列させる。較正回路202は、ゲート発振器201に結合されて、第一クロック信号と第二クロック信号を受信し、第一クロック信号と第二クロック信号に従って、ゲート発振器201の配列操作を検出し、検出された配列操作に従って、制御信号Sctrlを生成する。

(もっと読む)

基準信号発生装置

【課題】温度に関連する各種の周波数変動要素の影響を抑制して、高精度な基準周波数信号を発生する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、自走用制御電圧信号を推定して記憶する。制御部10は、温度センサ16からの温度検出信号に基づいて電圧制御発振器14の温度を観測して記憶する。制御部10は、ホールドオーバを検出すると、その時点での温度を検出するとともに(S101)、記憶した過去の温度を含み温度の時間変化率を算出する(S102)。制御部10は、予め設定した制御補正値算出用係数を読み出し(S103)、当該係数により設定される演算式に、検出した温度および算出した温度の時間変化率を代入して、制御補正値を算出する(S104)。制御部10は、この制御補正値に基づいて自走用制御電圧信号を補正し、電圧制御発振器14へ与える。

(もっと読む)

発振器

【課題】 本発明は、発振器が搭載される電子機器に応じた立ち上がり時間を有する出力信号を生成することができ、従って出力信号を高精度に生成することができる発振器を提供することを目的とする。

【解決手段】 発振部200から出力される中間出力信号に対して、それぞれ異なる波形整形を行う複数の波形整形回路500A〜500Cを有する波形整形部300と、複数の波形整形回路500A〜500Cの中から選択された波形整形回路500に対応するデータを記憶する記憶部400と、記憶部400に記憶されているデータに基づいて、波形整形部300が有する複数の波形整形回路500A〜500Cの中から選択された波形整形回路500によって、中間出力信号に対して波形整形を行わせる制御部450とを備える。

(もっと読む)

半導体集積回路

【課題】 振動子型発振回路の発振停止を確実に検出し、発振停止を検出した際には確実に発振回路を再起動できる半導体集積回路を提供すること。

【解決手段】 半導体集積回路は、振動子によりメインクロック信号を生成する一つ以上のメイン発振回路と、メイン発振回路と独立し常に動作するリング発振器と、リング発振器の出力クロック信号を基準にメインクロック信号を監視してメイン発振回路の動作状態を判断するメインクロック検知回路と、メインクロック検知回路の検知結果に応じて、メイン発振回路を構成する素子の組み合せを変更する素子構成変更回路とを備える。

(もっと読む)

CR発振回路

【課題】抵抗及び容量の製造ばらつきや抵抗の温度変化により発振周波数が変動する問題を解決したCR発振回路を提供する。

【解決手段】CR発振回路は、正側の電源と第1の出力端との間を複数のPMOSトランジスタと複数の抵抗とを介して複数の電流経路で結合する第1の抵抗微調整回路と、負側の電源と第2の出力端との間を複数のNMOSトランジスタと複数の抵抗とを介して複数の電流経路で結合する第2の抵抗微調整回路と、第1の出力端と第3の出力端との間を複数のPMOSトランジスタと複数の粗調整抵抗とを介して複数の電流経路で結合する共に、第2の出力端と第3の出力端との間を上記複数の粗調整抵抗と複数のNMOSトランジスタとを介して複数の電流経路で結合する抵抗粗調整回路を含み、抵抗値を可変に調整することにより発振周波数を調整することを特徴とする。

(もっと読む)

パルス幅変調回路及びそれを用いたスイッチングアンプ

【課題】オーディオ信号の振幅が負側に過大になったときのパルス幅変調信号の応答性を安定させる。

【解決手段】基準クロックMCLKの各周期において前半の半周期で第1コンデンサC1が充電され、後半の半周期で第1コンデンサC1が放電される。各放電期間に第1コンデンサC1の電圧が充電終了時の電圧から所定の閾値電圧Vthに低下するまでの放電時間をパルス幅とするパルス信号が第1RSフリップフロップ回路17で生成される。第2コンデンサC2でも第1コンデンサC1と同様の充放電動作が行われ、同様のパルス信号が生成される。信号出力回路19で第1,第2RSフリップフロップ回路17,18からのパルス信号を合成してパルス幅変調信号PWMoutが生成される。充電電流生成回路14ではオーディオ信号を電圧−電流変換した電流に補助電流Iminを加算し、オーディオ信号の振幅が負側に過大にならないように制限される。

(もっと読む)

オシレータ

【課題】本発明は、発振周波数の安定化や低電圧駆動化を実現することが可能なオシレータを提供することを目的とする。

【解決手段】本発明に係るオシレータ161は、回路を構成するトランジスタ(図24の例ではトランジスタN6)のオンスレッショルド電圧に対して、回路で生成される定電流Iが正特性を示す構成の定電流回路161aと;定電流回路161aから供給される定電流Iに対して、回路で生成されるクロック信号CLKの発振周波数foscが正特性を示す一方、回路を構成するトランジスタ(図24の例ではトランジスタN9〜N11)のオンスレッショルド電圧に対して、回路で生成されるクロック信号CLKの発振周波数foscが負特性を示す構成の発振回路161bと;を有して成る構成とされている。

(もっと読む)

発振回路および電子機器

【課題】発振回路の周波数を広範囲で精度良く制御する方法を提供する。また、標準集積

回路生産プロセスに対して有利な回路を提供する。

【解決手段】本発明の回路は第1極性を有する第1電流および第2電流と、第1極性と反

対の第2極性を有する第3電流を受信するキャパシタを含む。回路はバイアス入力を受信

する第1回路と、粗制御入力を受信する第2回路と、微制御入力を受信する第3回路をさ

らに含む。第1回路はさらにバイアス入力に応答して第1電流を提供する。第2回路はさ

らに、第2電流が一般的にゼロから第1電流の大きさの倍数までの大きさを有し、粗制御

入力に応答して第2電流を提供する。第3回路はさらに、キャパシタが微制御入力で決定

されたしきい値電圧を超える電圧を有する時に第3電流を提供する。

(もっと読む)

発振装置、その調整方法及びメモリ装置

【課題】簡単に発振信号の周期のばらつきを防止することができる発振装置、その調整方法及びメモリ装置を提供することを課題とする。

【解決手段】イネーブル信号に応じて発振信号を生成する発振器(105)と、前記発振信号の発振数をカウントし、第1の信号で指定された発振数でリセットするかしないかの選択を行うことができるカウンタ(106)と、前記カウントされた発振数及びリファレンス数を比較する比較器(107)とを有することを特徴とする発振装置が提供される。

(もっと読む)

1 - 20 / 41

[ Back to top ]