Fターム[5J043DD14]の内容

Fターム[5J043DD14]に分類される特許

21 - 40 / 42

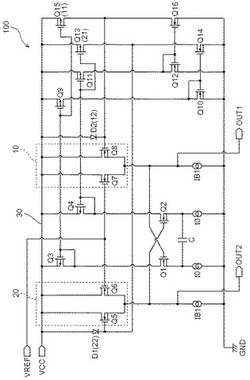

発振器

【課題】発振周波数が一定なパルス信号を出力可能な発振器を提供する。

【解決手段】コンデンサCの一方の電極に接続される第1スイッチ素子Q1の開閉状態と、コンデンサCの他方の電極に接続される第2スイッチ素子Q2の開閉状態とを、コンデンサCの充放電に応じて変化する端子間電圧に基づいて交互に切り替えて所定の周期を有するパルス信号を出力する発振器100は、第1スイッチ素子Q1の開閉状態を制御する制御信号を出力する制御信号出力部10と、第1スイッチ素子Q1の閉状態への移行に応じて、第1スイッチ素子Q1を閉状態にする制御信号の信号レベルを保持する閉信号レベル保持部11と、第2スイッチ素子Q2の閉状態への移行に応じて、第1スイッチ素子Q1を開状態にする制御信号の信号レベルを保持する開信号レベル保持部12と、を備える。

(もっと読む)

プログラマブルデュアルエッジトリガードカウンター

【課題】出力クロック信号のジッターを低減し、デューティサイクル分解能を改善するための回路の提供。

【解決手段】最小のジッターを備えたクロック信号を合成するためのカウンターは、出力クロックの立ち上がりエッジを入力クロック信号の立ち上がりエッジまたは立ち下がりエッジによりトリガーしなければならないかどうかを決定するために、さらに、出力クロックの立ち下りは、入力クロック信号の立ち下りの立ち上がりエッジまたは立ち下りによりトリガーしなければならないかどうかを決定するために進行中のカウントを分析する。カウンターはM/N:Dカウンターとして実施してもよい。このカウンターにおいて、位相アキュムレーターは所定の値と比較され、出力クロック信号の立ち上がりエッジおよび立ち下りを選択する。

(もっと読む)

パルス生成装置

【課題】パルス信号の周期及びデューティ比を、相互に影響を与えることなく独自に設定可能にしたパルス生成装置を提供すること。

【解決手段】本発明にかかるパルス生成装置は、パルス周期を設定する信号を入力し、パルス周期を制御する周期制御信号を出力する周期設定手段11を備える。また、パルスのデューティ比を設定するデューティ比設定信号を入力するとともに、周期設定手段において設定されるパルス周期を含む信号を入力し、当該パルス周期とデューティ比設定信号に基づいて、パルスのデューティ比を制御するデューティ比制御信号を生成するデューティ比設定手段12を備える。さらに、周期制御信号とデューティ比制御信号に基づいて、設定された周期及びデューティ比を有するパルス信号を生成するPWM出力発生手段13を備えることを特徴とする。それにより、パルス周期に影響されることなくパルスのデューティ比を決定することが可能である。

(もっと読む)

遅延回路

【課題】リセット動作に要する時間を短縮でき、リセット動作時に発生する雑音を抑制し、高速な繰り返しの入力信号に対応でき、高集積化、低消費電力化できるランプ波形発生方式の遅延回路を提供する。

【解決手段】ランプ波形を発生する遅延発生容量と、一端が第1の初期電圧源に接続され他端が遅延発生容量の他端に接続の第1のスイッチと、一端が第2の初期電圧源に接続され他端が遅延発生容量の他端に接続の第2のスイッチと、一端がチャージ電流源に接続され他端が遅延発生容量の他端に接続の第3のスイッチと、一端がディスチャージ電流源に接続され他端が遅延発生容量の他端に接続の第4のスイッチと、第1のコンパレータと、入力に第1のコンパレータの出力が接続される第1のワンショットと、第2のコンパレータと、入力に第2のコンパレータの出力が接続される第2のワンショットと、遅延出力信号を出力する論理和ゲートとを備える。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

基準クロック補正回路、基準クロック補正方法およびプログラム

【課題】基準信号を切り替えても発振器を自走状態にさせることの少ない基準クロック補正回路を提供する。

【解決手段】本発明に係る基準クロック補正回路1は、複数の基準信号の各々の安定度が良好であるか否かを判断する複数のクロック安定度検出部21a〜cと、複数の基準信号の中で安定度が良好である基準信号を選択基準信号102とする基準信号設定部22と、選択基準信号と基準クロック信号101を用いて制御値105を算出する発振器制御部12と、制御値に基づいて基準クロック信号を発振する発振器13とを有する。

(もっと読む)

信号形成回路

【課題】正確なクロック信号を発生させることのできるクロック信号形成回路の提供。

【解決手段】第1トランジスタ7のソース端子7aは電源電圧Vddと接続され、ドレイン端子7cは、第3トランジスタ8および直流抵抗9を介して接地されている。第3トランジスタ8のソース端子8cと直流抵抗9との間には、基準電圧Vsが印加されている。第2トランジスタ10は第1トランジスタ7と同特性のFETであり、そのソース端子10aには電源電圧Vddが印加されるとともに、ゲート端子10bには第1トランジスタ7のゲート端子7bが接続され、さらに、ドレイン端子10cにはコンデンサ11が接続されている。これにより、コンデンサ11の充電電流は基準電圧Vsの変動に応じて変化することができる。比較部5には基準電圧Vsおよびコンデンサ11の電圧が入力され、双方の電圧の間の大小関係が逆転した場合に出力信号が反転する。

(もっと読む)

発振回路および電子機器

【課題】発振回路の周波数を広範囲で精度良く制御する方法を提供する。また、標準集積

回路生産プロセスに対して有利な回路を提供する。

【解決手段】本発明の回路は第1極性を有する第1電流および第2電流と、第1極性と反

対の第2極性を有する第3電流を受信するキャパシタを含む。回路はバイアス入力を受信

する第1回路と、粗制御入力を受信する第2回路と、微制御入力を受信する第3回路をさ

らに含む。第1回路はさらにバイアス入力に応答して第1電流を提供する。第2回路はさ

らに、第2電流が一般的にゼロから第1電流の大きさの倍数までの大きさを有し、粗制御

入力に応答して第2電流を提供する。第3回路はさらに、キャパシタが微制御入力で決定

されたしきい値電圧を超える電圧を有する時に第3電流を提供する。

(もっと読む)

発振装置、その調整方法及びメモリ装置

【課題】簡単に発振信号の周期のばらつきを防止することができる発振装置、その調整方法及びメモリ装置を提供することを課題とする。

【解決手段】イネーブル信号に応じて発振信号を生成する発振器(105)と、前記発振信号の発振数をカウントし、第1の信号で指定された発振数でリセットするかしないかの選択を行うことができるカウンタ(106)と、前記カウントされた発振数及びリファレンス数を比較する比較器(107)とを有することを特徴とする発振装置が提供される。

(もっと読む)

クロック信号発生装置

【課題】クロック信号伝送において信号波形歪みや信号遅延による位相ひずみの生じにくいクロック信号を発生するクロック信号発生装置を提供する。

【解決手段】本発明のクロック信号発生装置は、単一の周波数成分からなる第1クロック信号を出力する信号発生部と、上記第1クロック信号の振幅値内に設定された複数の閾値と上記第1クロック信号の瞬時値とをウインドコンパレータによって比較して第1クロック信号の位相を判別し、この位相角度に対応して信号の立ち上がり又は立ち下がりを決定して第2クロック信号を形成する位相角度検出部と、を備える。

(もっと読む)

抵抗・容量可変RC発振器

【課題】シングル・チャンネルの抵抗・容量可変RC発振器を提供する。

【解決手段】抵抗・容量可変RC発振器は、発振器の入力端に設置される抵抗・容量選択スイッチと、抵抗出力端と、容量出力端と、第1端が抵抗・容量選択スイッチに接続されて、第2端が抵抗出力端にフローティングする少なくとも一つの抵抗スイッチと、第1端が抵抗・容量選択スイッチに接続されて、第2端が容量出力端にフローティングする少なくとも一つの容量スイッチと、を備えてなるものであり、抵抗・容量選択スイッチによって、どの抵抗スイッチの第2端を抵抗出力端に接続する、及びどの容量スイッチの第2端を容量出力端に接続するかを選択して、抵抗出力端と容量出力端に異なる組み合わせの抵抗・容量出力値を発生させる。

(もっと読む)

パルス幅変調の方法および装置

【課題】コストがかかる、温度と作製プロセスの変動と共に変化しない正確な値を有する集積抵抗器を実装しないようにする。

【解決手段】電流に応答するパルス幅変調信号を提供する装置および方法が開示される。本発明の態様による回路は、第1の持続時間中に第1の電流をコンデンサの第1の電圧に変換するための、また、第2の持続時間中に、第1の電圧を第2の電圧に変化させるように第2の電流を放電するためのコンデンサを含む。比較器も含まれており、入力電流に応答して周期出力信号のパルス幅を変化させるために、第2の持続時間中にコンデンサの電圧を基準電圧と比較するようにコンデンサの出力に結合される。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】スケルチ検出回路は、差動信号の電位振幅が、スケルチレベルを超えているかどうかを検出し、その検出信号を出力するピーク検出回路と、検出信号のパルス幅を、そのパルス幅の時間を含めて、差動信号のデータの1周期分の時間以上の時間だけ延長するパルス幅延長回路とを備える。ここで、ピーク検出回路は、差動信号の電位振幅に応じた電位を持つ第1および第2の信号を出力する入力アンプ回路と、入力アンプ回路と同一構成であり、スケルチレベルに相当するリファレンス電圧に応じた電位を持つ第3および第4の信号を出力するレプリカアンプ回路と、第1および第2の信号に応じて流れる合成電流と第3および第4の信号に応じて流れる固定電流とを比較し、その電流差に応じて、差動信号の電位振幅がリファレンス電圧を超えているかどうかを表す検出信号を出力する電流比較回路とを備える。

(もっと読む)

クロック生成装置

【課題】クロック生成装置において、リングオシレータが高温になるのを抑える。

【解決手段】クロック生成装置10は、リングオシレータ13の出力信号を割り算器19が算出した分周比で分周する第一分周器21と、第一分周器の出力信号をニ分周する第二分周器23と、リングオシレータの出力信号のパルス数を所定時間計測するカウンタ15,25と、割り算器と、比較器29とを備える。割り算器は、第一分周器からの出力信号が、所定周波数のクロック信号となるよう第一分周器に設定する分周比を演算する。一方、比較器は、カウンタのカウント値と閾値とを比較し、カウント値が閾値以上である場合、第二分周器に入力するイネーブル信号をオフにして、第二分周器の分周機能をオフし、カウント値が閾値未満である場合には、イネーブル信号をオンにして、第二分周器の分周機能をオンにする。これにより、リングオシレータが高温の時、クロック周波数を半減させる。

(もっと読む)

電圧制御発振器および電圧制御発振方法

【課題】回路構成が複雑になることがなく、動作範囲を大きくすることができる電圧制御発振器および電圧制御発振方法を提供する。

【解決手段】電圧制御発振器1は、フリップフロップを構成するNANDゲート3と、オペアンプ17、抵抗5〜13およびキャパシタ15を備え当該オペアンプ17の反転端子に制御電圧を印可するブートストラップ回路とによって、当該制御電圧と発振周波数とを比例させるものにおいて、NANDゲート3の出力路と、オペアンプ17の非反転端子との間に、当該非反転端子から帰還した電圧が当該NANDゲート3の閾値以下になったか否かに基づいて、キャパシタ15に電荷を充電するかキャパシタ15から電荷を放電するか否かを決定するダイオード21を設けた。

(もっと読む)

可変幅パルスを有するハイ側とロー側のスイッチング素子を駆動するための自励発振回路

【課題】ハーフブリッジ構成で接続された、ハイ側とロー側のMOSFETのようなスイッチング素子(50,52)を駆動する自励発振回路を提供する。

【解決手段】この回路は、持続時間すなわち幅を変える交互に切り替わるゲートパルスを提供することによりスイッチング素子(50,52)を交互にターンオンする。そのパルスは、相互誘導を防止するため、デッドタイムにより分離される。起動されると、パルスは最小持続時間のゼロから最大持続時間に増加し、デッドタイムの持続時間は同時にその最小持続時間に減少し、ソフトスタートを与える。その回路は、各サイクルが、立ち上がり部分と、続いてロー部分に向かう立ち下がりエッジとを含む周期信号を供給するため、発振器(60)を含む。参照回路(90)は、可変参照信号を供給する。比較器(100)は、周期信号と可変参照信号とに対して応答し、そのパルス幅が参照信号に比例するパルス出力信号を供給する。

(もっと読む)

半導体装置及びそれを用いた電子機器

【課題】高機能化、多機能化及び付加価値化を実現した半導体装置の提供を課題とする。

【解決手段】基板上に、正確な周波数の信号を出力する回路(フェーズ・ロックド・ループ回路、PLL回路)を設けた半導体装置を提供する。PLL回路は、供給される信号を基に、一定の倍率の周波数の信号を出力する回路である。PLL回路は、位相比較器、ループフィルタ、電圧制御発振器及び分周器を含む。基板上にPLL回路を設けることにより、高機能化、多機能化及び高付加価値化を実現することができる。

(もっと読む)

発振回路

【課題】電源電圧が変動した場合にも、発振周波数の変動を少なくすることができる、抵抗とキャパシタを用いた発振回路を提供する。

【解決手段】第1定電流が流される抵抗回路で基準電圧を発生する一方、第1定電流に比例する第2定電流で充電されるキャパシタ回路で充電電圧に応じた比較電圧を発生する。その比較電圧が基準電圧を超えるときに検出信号を発生する。その検出信号に応じてオンするスイッチ回路により、キャパシタ回路の電荷を放電する。同時に、検出信号の幅を、パルス幅伸張回路により拡げる。そして、その伸張パルスに基づいて、発振パルス生成回路により、発振パルスを生成する。

(もっと読む)

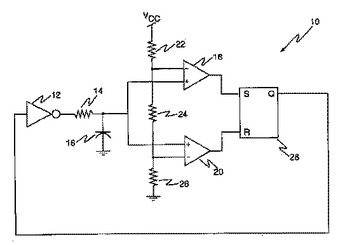

電圧補償及び温度補償されたRC発振回路

入力及び出力を有するインバータを具備する、温度補償された集積RC発振回路。RC網は、前記インバータと、比較器の対との間に接続されている。第1比較器は、第1基準電圧に接続された反転入力と、前記RC網に接続された非反転入力と、出力とを具備する。第2比較気は、前記RC網に接続された反転入力と、第2談笑電圧に接続された非反転入力と、出力とを具備する。セット・リセット・フリップフロップは、前記第1比較器の出力に接続されているセット入力と、前記第2比較器の出力に接続されているリセット入力と、前記インバータの入力に接続されている出力とを具備する。前記比較器の差動増幅器は、各々ミラー接続されたpチャネルMOSトランジスタを制御する、ダイオード接続されたpチャネルMOSトランジスタを具備し、前記pチャネルMOSトランジスタのチャネル幅は、前記ダイオード接続されたpチャネルカレントミラートランジスタの幅より狭い。  (もっと読む)

(もっと読む)

21 - 40 / 42

[ Back to top ]