Fターム[5J043LL01]の内容

Fターム[5J043LL01]の下位に属するFターム

供給電流制御 (48)

Fターム[5J043LL01]に分類される特許

1 - 20 / 142

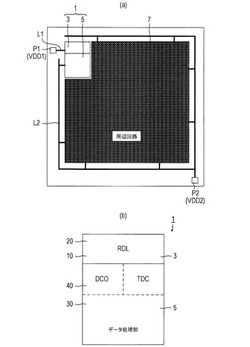

半導体集積回路

【課題】半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させる。

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

(もっと読む)

発振器

【課題】 発振器に含まれる複数の遅延反転増幅回路の配線容量を高い精度で一定にすることにより、容易に正確、かつ高周波数の多相クロックを生成できる発振器を提供する。

【解決手段】 リング状に接続された遅延反転増幅回路101〜105を、1列にレイアウトし、かつ、遅延反転増幅回路102の出力端子から103の入力端子までの配線長と、遅延反転増幅回路103の出力端子から104の入力端子までの配線長と、遅延反転増幅回路104の出力端子から105の入力端子までの配線長と、遅延反転増幅回路105の出力端子から101の入力端子までの配線長と、遅延反転増幅回路101〜105の出力端子と接続されている配線の配線長を全て等しくする。

(もっと読む)

リングオシュレータ回路、A/D変換回路、および固体撮像装置

【課題】偶数個(段)の反転回路をリング状に連結した構成でも、安定した発振動作を行うリングオシュレータ回路、これを用いたA/D変換回路、およびこれを用いた固体撮像装置を提供する。

【解決手段】反転回路が偶数個リング状に連結された円周上でパルス信号を周回させるリングオシュレータ回路であって、反転回路の内の一つが、制御信号に応じて第1のパルス信号を駆動する第1の起動用反転回路であり、他の一つが、第1のパルス信号の先頭エッジに基づいて第2のパルス信号を駆動する第2の起動用反転回路であり、さらに他の一つが、第2のパルス信号を駆動後の第1のパルス信号の先頭エッジに基づいて第3のパルス信号を駆動する第3の起動用反転回路であり、第1〜第3のパルス信号が円周上に同時に存在するとき、パルス信号の進行方向に対して第3、第2、第1の順になるように、第1〜第3の起動用反転回路を反転回路の円周内に配置する。

(もっと読む)

発振器

【課題】簡単な構成で高速立ち上げが可能であり、さらに従来のリング型電圧制御発振器に比べて安定な周波数の信号を生成することができる発振器を提供する。

【解決手段】制御電圧入力端子に印加された制御電圧に従って発振周波数が変化するリング型電圧制御発振器10と、リング型電圧制御発振器10の出力信号を一定時間幅のパルス信号に変換して出力するパルス整形回路20と、参照電圧からパルス整形回路20が出力する周波数が変化するパルス信号の平均電圧を差し引いた電圧を積分してリング型電圧制御発振器10の制御電圧入力端子に出力する積分回路30とを備える。

(もっと読む)

発振器及び発振器を有する半導体装置

【課題】インバータとの接続点であるノードの最高電圧及び最低電圧が最適な電圧になるようにし、各ノードの信号の電圧の変化によって生じるクロック信号の周波数のずれを抑えることのできる発振器を提供する。

【解決手段】複数のインバータI1,I2のうちのインバータI1の接続点であるノードN1の信号S1の最高電圧及び最低電圧が、2つの容量素子C1,C2の容量値c1,c2と抵抗素子R1の抵抗値r1とによって任意の電圧になるようにする。これにより、信号S1の最高電圧及び最低電圧を、本来の最高電圧又は最低電圧にすることができ、ノードN1の信号S1の電圧v1の変化によって生じるクロック信号SOUTの周波数TOのずれを抑えることができる。

(もっと読む)

リング発振器

【課題】LSI等の半導体集積回路に組み込まれたリング発振器は、専用の電源スイッチを有しているわけではないので、それを構成するMOSトランジスタには非発振時中も通電され続けるものがある。そのため、特性が劣化し、リング発振器の発振周期が次第に増大していた。

【解決手段】MOSトランジスタで構成され反転ゲートとして機能する奇数個のNAND回路を、その出力端子と他のNAND回路の第1の入力端子とを接続するというように順次接続し、全体としてリング状とする。発振出力は、任意の1つのNAND回路の出力端子から取り出す。そして、発振または非発振を制御する信号を入力する発振制御入力端子20を、各NAND回路の第2の入力端子と接続する。

(もっと読む)

診断回路、発振回路

【課題】リファレンスクロックを要することなく発振信号の周波数範囲を診断できる、回路規模の小さな診断回路等を提供する。

【解決手段】制御信号102に応じて周波数が変化する発振信号166の周波数範囲を診断する診断回路10であって、制御信号102を受け取り、制御信号102に基づく値である比較値と所定の限界値とを比較する比較器を含み、比較器が比較した結果に基づいて診断出力値100を生成する。所定の限界値として上限値と下限値とを定め、比較値と上限値とを比較する上限比較器と、比較値と下限値とを比較する下限比較器とを含み、上限比較器および下限比較器が比較した結果に基づいて、診断出力値100を生成する。

(もっと読む)

マルチプレクサの選択から出力までの遅延を決定するためのリングオシレータ

【課題】マルチプレクサの選択から出力までの遅延を決定する方法を提供する。

【解決手段】出力リード26、選択入力リード25、第1データ入力リード23および第2データ入力リード24を有する第1のマルチプレクサ21と、出力リード30および選択入力リード29を有する第2のマルチプレクサ22とを備え、前記第1のマルチプレクサおよび前記第2のマルチプレクサは実質上同一の構造を有し、前記第2のマルチプレクサの前記出力リードは前記第1のマルチプレクサの前記選択入力リードに結合され、発振信号は前記第2のマルチプレクサの前記出力リード上に存在し、前記第1のマルチプレクサの前記出力リードは前記第2のマルチプレクサの前記選択入力リードに結合され、第1論理レベルは前記第1のマルチプレクサの前記第1データ入力リード上に常時存在し、第2論理レベルは前記第1のマルチプレクサの前記第2データ入力リード上に常時存在する回路。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

乱数生成回路

【課題】回路動作開始直後の初回サンプリングにおいてもランダム性の高い真性乱数を生成することのできる乱数生成回路を提供する。

【解決手段】奇数段の論理ゲートで構成されたM1個の第1のリングオシレータ10−1と、偶数段のインバータと1段の論理ゲートで構成されたM2個の第2のリングオシレータ10−2と、第1のリングオシレータ10−1の中間ノード出力と第2のリングオシレータ10−2の中間ノード出力の排他的論理和をとる(M1+M2)入力XOR21と、出力をサンプリングクロックでラッチし、乱数値として出力するD−FF22と、サンプリングクロックを生成する制御部100とを備え、第1のリングオシレータ10−1を構成する各論理ゲートの出力にそれぞれインバータが接続され、インバータのいずれか1つの出力をリングオシレータの中間ノード出力とする。

(もっと読む)

半導体集積回路及び測定温度検出方法

【課題】インバータのON抵抗や内部遅延時間の影響を排除して、測定温度を適正に検出することができる、半導体集積回路及び測定温度検出方法を提供する。

【解決手段】、インバータinv11〜inv51には、バイアス回路12により生成されたバイアス信号pbias及びバイアス信号nbiasまたは、バイアス信号pbias及びバイアス信号nbiasに基づいたバイアス信号pbias_inv11、nbias_inv11、pbias_inv21、nbias_inv21が、基準抵抗素子RSによるキャリブレーションの際に、基準抵抗素子RSによる発振周波数fSが基準発振周波数となるように印加される。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

半導体集積回路

【課題】回路規模及び消費電流を増加させることなく、且つ、単純な回路を用いて、出力信号の雑音成分を低減する。

【解決手段】半導体集積回路は、リング発振器10と、ノイズキャンセラ20と、を備える。リング発振器10は、入力信号Vinに基づいて、第1位相を有する第1出力信号Vout1を生成する第1信号生成部12と、入力信号Vinに基づいて、第1位相とは異なる第2位相を有する第2出力信号Vout2を生成する第2信号生成部13と、を備える。ノイズキャンセラ20は、第1増幅係数K1を用いて第1信号生成部12により生成された第1出力信号Vout1を増幅する第1増幅器21と、第2増幅係数K2を用いて第2信号生成部13により生成された第2出力信号Vout2を増幅する第2増幅器22と、第1増幅器21により増幅された第1出力信号Vout1と第2増幅器22により増幅された第2出力信号Vout2とを合成する演算器24と、を備える。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

CMOSインバータ型高周波分周器

【課題】無線通信機器等に用いられるCMOSインバータ型高周波分周器を低消費電流にて実現する。

【解決手段】各々インバータ及び1つ以上のスイッチから構成された第1〜第4のラッチ機能付インバータ4,5,6,7と、第1及び第2のトランス8,9とで分周器を構成する。従来用いていた“2つのインバータを正帰還にして構成されたラッチ”は、不要となり、その代役としてトランス8,9を用いる。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

可変駆動電圧により動作するオシレータ

【課題】安定した発振周期の信号を出力することができるオシレータを提供すること。

【解決手段】複数の論理素子がリング状に接続され、所定の周期の発振信号を出力する可変駆動電圧により動作するオシレータであって、複数の論理素子に選択的に印加される第1及び第2の駆動電圧を発生させる内部電圧発生手段を備え、発振信号の周期が正常状態である場合には、第1の駆動電圧が複数の論理素子に印加され、発振信号の周期が正常状態より短いか又は長い場合には、第2の駆動電圧VOSCが複数の論理素子に印加され、発振信号の周期が一定に維持されるように構成されている。

(もっと読む)

半導体集積回路装置、及び電源電圧制御方法

【課題】短時間に電源電圧を最適値に制御することが可能な半導体集積回路装置を提供することである。

【解決手段】本発明にかかる半導体集積回路装置100は、ターゲット回路2と、ターゲット回路2に電源電圧を供給する電圧供給回路4と、電圧供給回路4の出力電圧を制御する制御回路3と、ターゲット回路2に供給される電源電圧の電圧値を予測する目標電圧予測回路1とを備える。制御回路は、ターゲット回路2の要求動作周波数が第1の動作周波数から第2の動作周波数に変化した際に、電圧供給回路4の出力電圧を所定の電圧値だけ変化させる。目標電圧予測回路1は、所定の電圧値の変化にともなうターゲット回路2の動作周波数の変化量を検出すると共に、動作周波数の変化量と所定の電圧値との関係に基づいて目標電圧値を算出する。電圧供給回路4は、ターゲット回路2に目標電圧値の電源電圧を供給する。

(もっと読む)

1 - 20 / 142

[ Back to top ]