Fターム[5J055AX37]の内容

Fターム[5J055AX37]の下位に属するFターム

フェイルセーフ構成 (60)

Fターム[5J055AX37]に分類される特許

141 - 158 / 158

情報処理装置,及び、半導体集積回路

【課題】同一のクロック信号を複数の半導体集積回路に分配する場合において、基板のアートワークの自由度を高めつつパワーオンリセット機能を安価に実現できる情報処理装置と、このような情報処理装置に組み込まれる半導体集積回路とを、提供する。

【解決手段】情報処理装置10に組み込まれるASIC14の内部のリセット回路モジュール14bは、定電圧電源ユニット11からの電気の電圧を監視するとともに、電圧がリセット電圧を超過した後、CPU13及び他IC15内のPLL回路モジュールのロックアップ時間以上の一定時間だけ待機してからCPU13及び他IC15並びに内部回路モジュール14aへメインリセット信号を出力する。

(もっと読む)

リセット装置

【課題】 電源立ち上げ時のレベル逆転をマスクし、リセットの信頼性を高める。

【解決手段】 電源レベル検出部23は、電源分圧Vdと参照電圧Vfとを比較して、リセット解除を開始すべき電源レベルLの検出を行う。定電流生成部24は、電源電圧Vが電源レベルLに到達したら、コンデンサCを充電させる一定電流Iを生成する。リセット部25は、一定電流Iで充電されるコンデンサCの端子電圧Vcが参照電圧Vfを下回ればリセットを行い、参照電圧Vfを上回ればリセット解除を行う。マスク処理部26は、電源の立ち上げまたは低位レベルから回復する際に、電源電圧Vが電源レベルLに到達していないにもかかわらず、参照電圧Vfが電源分圧Vdを下回る逆転状態が生じた場合は、逆転状態をマスクし、逆転状態が解消したらマスク解除を行うためのマスク信号MSKを生成する。放電制御部27は、マスク信号MSKによってコンデンサCを強制放電する。

(もっと読む)

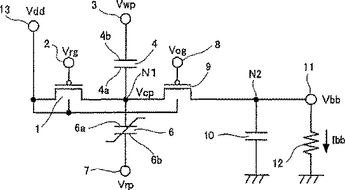

電圧発生回路、電圧発生装置及びこれを用いた半導体装置、並びにその駆動方法

キャパシタ(4)、キャパシタ(4)に直列接続された強誘電体キャパシタ(6)、出力端子(11)、出力端子(11)を接地するキャパシタ(10)、電源電圧供給端子(13)、電源電圧供給端子(13)と2つのキャパシタ(4,6)の接続ノード(N1)とを接続するスイッチ(1)、及び接続ノード(N1)と出力端子(11)とを接続するスイッチ(9)を備え、第1の期間において、スイッチ(1)及び(9)がオフ状態にされた状態で、端子(3)が接地されると共に端子(7)に電源電圧が供給され、第2の期間において、端子(3)に電源電圧が供給され、且つスイッチ(9)がオン状態にされ、第3の期間において、スイッチ(9)がオフ状態にされ、スイッチ(1)がオン状態にされ、且つ端子(7)が接地され、第4の期間において、端子(7)に電源線圧が供給され、前記第1の期間から前記第4の期間までが順に繰り返される、電圧発生回路。  (もっと読む)

(もっと読む)

スタートアップ回路及びこれを用いた定電流回路

【課題】 定電流回路におけるスタートアップ回路において、広温度範囲で動作するスタートアップ回路を実現する。

【解決手段】 電源とPMOSトランジスタ105のソース間にコンデンサ102を設ける事で、電流パスを直流的に完全切断する構成とし、高温時のPMOSトランジスタ105のリークによる、定電流回路の定電流値ずれを防止する。

(もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路の出力電圧をPWM方式のフィードバック制御により安定に制御する。

【解決手段】直列に接続された第1及び第2の電荷転送用MOSトランジスタM1,M2と、第1及び第2の電荷転送用MOSトランジスタM1,M2の接続点に第1の端子が接続されたコンデンサC1と、クロックCLKに応じたランプ電圧を発生する積分回路21と、前記ランプ電圧と第2の電荷転送用MOSトランジスタM2からの出力電圧Voutに応じた電圧とを比較する比較器15と、前記クロックCLKを1/2分周する分周器22と、前記分周器22の分周出力に応じて前記比較器15の出力をマスクするナンド回路16と、を備え、前記ナンド回路16の出力を前記コンデンサC1の第2の端子に印加する。

(もっと読む)

MOSFET装置および関連動作方法

本発明は、MOSFET装置(10)を提供し、このMOSFET装置(10)は、ボディダイオード構造(22)を有し、またこのボディダイオード構造(22)に関連する逆回復過渡信号を減少させるために、このボディダイオード構造(22)の逆回復中にそのMOSFET(12)のゲートに選択的に印加されるバイアス電圧を供給するように構成されるバイアス手段を供給され、このバイアス手段は、その装置(10)のゲートパス内に配置されるダイオード素子(16)を有する。  (もっと読む)

(もっと読む)

スイッチング電源装置

【課題】 過電流の際に,その原因に応じて,過剰にならない適切な対処ができるようにしたスイッチング電源装置を提供すること。

【解決手段】 元電源1からの電流供給を出力トランジスタ2でスイッチングし,コイル3およびコンデンサ4で平滑化して負荷5,6に供給するスイッチング電源装置において,出力トランジスタ2の出力電流による検出電圧を,コンパレータ11,12で2水準の基準値と比較することとした。そして,検出電圧が第1の基準値に達してから第2の基準値に達するまでの間に限り,カウンタ22でカウントすることとした。そして,カウンタ22が第1の基準時間に達しないうちに検出電圧が第2の基準値に達した場合には,電流供給を停止することとした。また,検出電圧が第2の基準値に達しないうちにカウンタ22が第2の基準時間に達した場合には,デューティ比の低下および負荷6の遮断を行うこととした。

(もっと読む)

半導体スイッチの制御装置

【課題】複数の負荷回路を備えた回路で短絡接地が発生した場合に、短絡接地の発生した負荷回路のみを即時に遮断し、その他の負荷回路を継続して動作させることのできる半導体スイッチの制御装置を提供する。

【解決手段】半導体スイッチとしてのMOSFETを備えた複数の負荷回路と、各負荷回路と直流電源VBとを連結する電源配線21とを備え、短絡接地が発生した際にMOSFETを遮断する機能を具備した半導体スイッチの制御装置において、電源配線21に発生する逆起電力を検出する逆起電力検出回路12を有し、各負荷回路は、MOSFETの両端電圧VDSを検出するVDS検出回路13と、VDS検出回路にて、電圧VDSが所定のレベル以上となったことが検出され、且つ、逆起電力検出回路により、電源配線に所定の閾値以上の逆起電力E1が発生していると判断された際に、MOSFETを遮断する制御を行う制御手段17とを備えたことを特徴とする。

(もっと読む)

CMOS駆動回路

【課題】 入力信号の変化時におけるPチャネルMOSトランジスタとNチャネルMOSトランジスタの同時導通による貫通電流が発生しても、駆動回路の動作不安定を防止することができるCMOS駆動回路を提供する。

【解決手段】 CMOSインバータを構成するNチャネルMOSトランジスタ13とPチャネルMOSトランジスタ24の間に、ソース電位に応じてオン状態とオフ状態が自動的に切り替わるNチャネルMOSトランジスタ14とPチャネルMOSトランジスタ25を直列に挿入することにより、プッシュプル回路を構成するMOSトランジスタ12,23のゲート・ソース間電圧を素子耐圧以下に抑え、かつ過渡的にNチャネルMOSトランジスタ13,14とPチャネルMOSトランジスタ24,25が共にオン状態となり貫通電流が流れた際のバイアス電圧の電圧変動を防止でき、安定したスイッチング素子の駆動を可能とする。

(もっと読む)

シフトレジスタ、それを有する表示装置、及び、そのシフトレジスタの駆動方法

【課題】 表示パネルの駆動回路の更なる小型化を阻むことなくその信頼性を更に向上させ、特にゲートラインの電位を更に長期間、安定に調節することで、表示装置の高画質を更に長期間、維持できるシフトレジスタ、を提供する。

【解決手段】 第一のプルアップ駆動制御部(51)が前のステージからゲート信号(GOUTM-1)を受信し、それと同期して制御信号(CNTRM)を出力する。プルアップ駆動部(53)は制御信号(CNTRM)に応じて第一のクロック信号(CLK)をゲート信号(GOUTM-1)として出力端子(OUT)を通してゲートラインに送出する。プルダウン駆動部(54)は第二のクロック信号(CKB)に応じて出力端子(OUT)に接続されたゲートラインを非活性化させる。そのとき、特にプルダウントランジスタ(Td)が第二のクロック信号(CKB)に応じてオンオフする。

(もっと読む)

半導体スイッチの制御装置

【課題】短絡電流と突入電流の識別精度を高めると同時に、短絡電流の発生を検出するまでの判定時間をできるだけ短くすることにより、短絡電流発生時における回路の遮断を早め、半導体素子の電力損失及び温度上昇を最小限とすることのできる半導体スイッチの制御装置を提供する。

【解決手段】直流電源VBと負荷11との間に配置されたMOSFET(T1)を制御することにより負荷11のオン、オフを制御すると共に、短絡電流が流れた際にMOSFET(T1)を保護する機能を具備した半導体スイッチの制御装置において、所定の閾値電圧を設定し、MOSFET(T1)と、直流電源VBとを結ぶ第1の配線に発生する逆起電力E1が閾値電圧よりも大きいか否かを判定する逆起電力検出回路13と、逆起電力検出回路13にて、逆起電力E1の大きさが閾値電圧よりも大きいと判定された際に、MOSFET(T1)をオフとする制御を行う制御回路12とを備える。

(もっと読む)

パワーオン・リセット回路

【課題】 チップ面積の増大を抑制し、且つアナログ・デジタル混在LSIにおける電源投入時でのロジック部の初期化を迅速に安定して行う。

【解決手段】 パワーオン・リセット回路1は、スタートアップ部4及びバンドギャップリファレンス発生部5からなるバンドギャップリファレンス回路2と、検出器3から構成されている。パワーオン・リセット回路1の動作は、まず、電源投入されると電源がスタートアップ部4及びバンドギャップリファレンス発生部5に供給される。次に、スタートアップ部4は動作を開始し、バンドギャップリファレンス発生部5にスタートアップ信号を出力する。続いて、バンドギャップリファレンス発生部5は、スタートアップ信号を入力し、回路動作をしてスタートアップ部4及び検出器3に検出信号を出力する。この検出信号を入力した検出器3はリセット信号をロジック部7に出力する。

(もっと読む)

リセット回路

【課題】 パワーダウン時のパワーダウンリセット信号のタイミング制御を容易にし、繰り返し電源をオン/オフした時の起動不良を防ぐことを課題とする。

【解決手段】 リセット回路は、電源検出回路とパワーダウン検出回路と出力回路とを有する。電源検出回路は、パワーオン及びパワーダウン時に電源電圧(VDD)に応じた第1の電圧が第1のしきい値より大きいと第1の信号を出力し、低いと第2の信号を出力する。パワーダウン検出回路は、パワーダウン時に第2の信号が出力された後、電源電圧(VDD)に応じた第2の電圧が第2のしきい値より小さくなると第3の信号を出力する。出力回路は、パワーオン時に第1の信号が出力されるとローレベルからハイレベルに変化するパワーオンリセット信号(POR)を出力し、パワーダウン時に第3の信号が出力されるとハイレベルからローレベルに変化するパワーダウンリセット信号(POR)を出力する。

(もっと読む)

パルス幅変調されるモーター・コントローラの利得エラー相殺のための電力供給変動の抑止

ディスクドライブ・システムのボイスコイルモーター(22)の位置決めドライバ(32)が開示される。パルス幅変調される前段ドライバ(46)が、ボイスコイルモーター(22)を駆動するため「H」ブリッジに配置されるパワー・トランジスタ(50PH、50NH、50PL、50NL)に結合され、電力供給電圧(VM)でバイアスがかけられる。パルス幅変調される前段ドライバ(46)は、エラー増幅器(36)からのエラー信号とランプ・クロック生成器(48)で生成されるランプ・クロック信号(RMP)との比較に従ってパワー・トランジスタ(50PH、50NH、50PL、50NL)を駆動する。ランプ・クロック生成器(48)は、電力供給電圧(VM)の変動に応答してランプ・クロック信号(RMP)の高及び低限界を変調する制御回路を含む。高及び低限界のこの変調が、電力供給電圧(VM)の変動に起因するパワー・トランジスタ(50)の利得の変動を補償する。制御回路は、例えば、一定の周波数を維持するため、電力供給電圧(VM)の変動に従ってランプ・クロック信号(RMP)の勾配も変調し得る。  (もっと読む)

(もっと読む)

アクチュエータを制御するための電子装置

本発明は複数の誘導負荷を制御する装置に関する。この装置は、

複数の制御段から成る少なくとも1つの第1のグループと、

前記グループの制御段に共通した再導通化回路とを有しており、

前記制御段の各々は、

− 誘導負荷のためのボンディングパッドと、

− 導通化信号のための受信入力側と、

− 前記受信入力側に接続された制御電極と前記ボンディングパッドに接続された出力電極とを有するスイッチと、

− 前記ボンディングパッドに印加された電圧を測定し、該電圧がイネーブルレベルに達した場合にイネーブル信号を発生させるイネーブル回路を有しており、

前記再導通化回路は、前記グループの制御段のボンディングパッドにおける電圧を前記グループの各制御段のイネーブルレベルよりも高い共通のレベルに制限し、前記制御段のうちの1つのイネーブル回路がイネーブル信号を発生した場合に、導通化信号を該制御段のスイッチの制御電極に印加する。

本発明は、特に、ボンディングパッドに接続された負荷に対して同じ給電持続時間を保証するために使用することができる。  (もっと読む)

(もっと読む)

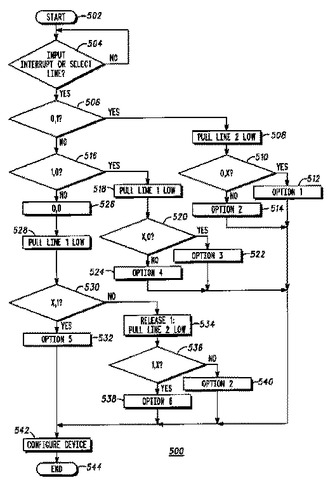

携帯機器のための割り込み駆動の拡張型オプション選択インタフェース

携帯電子機器(102)には周辺コンポーネント(104)が取り付けられ、この周辺コンポーネント(104)はオプション選択回路を使用して周辺コンポーネントのオプションクラスを示す。オプション選択回路は、携帯電子機器に割り込みを生成し、次いで種々のオプション論理ラインの論理レベルの変更により、オプションクラスを決定する。オプション選択ラインのうちの一つの論理状態の反転が検知されると、携帯電子機器はオプション選択回路のプレゼンスを知り、従って周辺コンポーネントのオプションクラスを決定する。  (もっと読む)

(もっと読む)

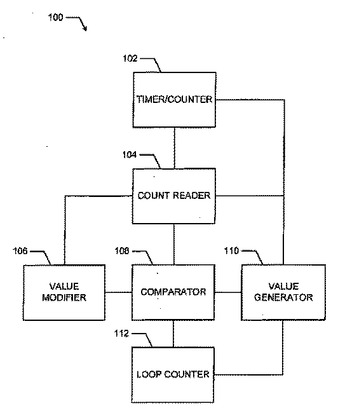

カウンタを用いて遅延を生成するための方法および装置

カウンタを用いて遅延時間を生成するための製造の複数の方法、装置、および複数の製品が開示される。特に、製造の前記複数の方法、装置、および複数の製品は、前記遅延時間に関連する複数のループの数の値およびカウンタに関連する少なくとも1つの特性値を決定する。残りのカウント値は、前記複数のループの数の値に基づいて、その後決定される。前記遅延時間は、前記カウンタと共に、前記複数のループの数の値および前記残りのカウント値に基づいて、生成される。

(もっと読む)

(もっと読む)

トラック/ホールド回路

スイッチ(10)とキャパシタ(12)を備えるトラック/ホールド回路である。第1のブートストラップスイッチ(14a)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第1のブートストラップスイッチ(14a)から出力されるクロック信号clkbootは、スイッチ(10)のゲートに印加される。第1のブートストラップスイッチ(14a)は、電流源(20)という形のレベルシフト手段及びバッファ手段(30)を介して、当該回路の入力Vinと出力Vsとの間に接続されている。第2のブートストラップスイッチ(14b)が設けられており、第2のブートストラップスイッチ(14b)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第2のブートストラップスイッチ(14b)から出力される逆位相クロック信号clknbootは、スイッチ(10)のいずれかの側に接続されている2つのダミースイッチ(16)のゲートに印加される。  (もっと読む)

(もっと読む)

141 - 158 / 158

[ Back to top ]