Fターム[5J055AX37]の内容

Fターム[5J055AX37]の下位に属するFターム

フェイルセーフ構成 (60)

Fターム[5J055AX37]に分類される特許

101 - 120 / 158

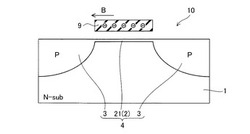

スイッチング素子、スイッチ回路、モータおよび発電装置

【課題】電源を用いることなく、かつ、摩擦により磨耗するなどの接触式のスイッチ構造の不都合を抑制することが可能なスイッチング素子を提供する。

【解決手段】このスイッチング素子10は、pチャネルトランジスタ4と、pチャネルトランジスタ4に対して相対的に移動可能なように設けられ、電荷を蓄積することが可能なエレクトレット部材9とを備えている。そして、エレクトレット部材9のpチャネルトランジスタ4に対する相対的な位置により、静電誘導を用いてpチャネルトランジスタ4のオン状態およびオフ状態を制御する。

(もっと読む)

誘導性負荷の駆動装置

【課題】逆起電圧を吸収するに際しても発熱が生じるのを防止するようにした誘導性負荷の駆動装置を提供する。

【解決手段】外部供給電源12と誘導性負荷14の間に介挿される第1のスイッチング素子28、誘導性負荷14とアース24の間に介挿される第2のスイッチング素子30、第1のスイッチング素子28と誘導性負荷14との間で分岐してアース24に接続される電路40を有すると共に、第1のスイッチング素子28がオフ、第2のスイッチング素子30がオンされるとき、誘導性負荷14の逆起電圧によって生じる逆起電流をアース24に還流させる還流回路18、さらに誘導性負荷14と第2のスイッチング素子30との間で分岐して外部供給電源12に接続される電路44を有すると共に、第1、第2のスイッチング素子28,30がオフされるとき、逆起電流を外部供給電源12に還元する逆起電流還元回路20を備えるように構成する。

(もっと読む)

電圧駆動型半導体素子の駆動方法、及び、ゲート駆動回路

【課題】スイッチング損失の減少や、サージ電圧の低下を図ることができる新たな技術を提案する。

【解決手段】電圧駆動型半導体素子(IGBT1)の駆動方法であって、前記電圧駆動型半導体素子のターンオン又はターンオフの指令のタイミングからサージ電圧発生のタイミングまでのサージ期間(ターンオン時間tON/ターンオフ時間tOFF)を記憶し、次回のターンオン時又はターンオフ時において、今回記憶したターンオン時又はターンオフ時における前記サージ期間に基づいて、前記電圧駆動型半導体素子の実効ゲート抵抗値を変更する、こととするものである。

(もっと読む)

遅延時間生成回路、それを用いた二次電池保護用半導体装置、バッテリパックおよび電子機器

【課題】高速クロックを用いることなしにテスト時間の大幅な短縮が行え、ICチップ面積の増加を抑えることが可能な遅延時間生成回路、それを用いた二次電池保護用半導体装置、バッテリパックおよび電子機器を提供すること。

【解決手段】入力されたクロック信号CLKのパルス数を計数するための縦続接続された複数のフリップフロップ回路FF1〜FFnからなるカウンタ回路12を備え、該カウンタ回路12の最終段FFnまたは所定の段のフリップフロップ回路の出力が反転した信号を遅延時間信号(Delay)として利用する遅延時間生成回路において、電子回路のテスト時に、前記カウンタ回路の最終段または前記所定の段のフリップフロップ回路より前段のフリップフロップ回路の出力信号を用いて遅延時間を生成するようにしたもので、これにより、特別な高速クロックを使用することなしに遅延時間の短縮が可能となった。

(もっと読む)

半導体装置

【課題】 半導体装置のリセット直後における不所望の動作を防止するとともに、半導体装置のリセット後における外部装置の制御に関する設定情報の変更を可能にする。

【解決手段】 半導体装置は、外部端子、制御パラメータ決定回路、レジスタ更新回路を備えて構成される。制御パラメータ決定回路は、レジスタおよび出力セレクタを備えて構成される。レジスタは、半導体装置のリセットに伴って初期化される。出力セレクタは、外部端子を介して供給される外部入力信号のレベル値に応じてレジスタのレジスタ値と同一のレベル値に設定される信号またはレジスタのレジスタ値と反対のレベル値に設定される信号のいずれかを選択して制御パラメータ信号として出力する。レジスタ更新回路は、制御パラメータ信号のレベル値を変更する必要がある場合、レジスタのレジスタ値を更新する。

(もっと読む)

電源回路装置及びこの電源回路装置を備えた電子機器

【課題】 本発明は、並列に接続された負荷それぞれに対して出力する電流値を同等の値とすることができるとともに、広い周波数帯域のPWM制御信号によっても安定して動作することができる電源回路装置を提供することを目的とする。

【解決手段】 安定化電源回路2より電圧供給される負荷3,4それぞれに直列に接続されたMOSトランジスタT1,T2と、このMOSトランジスタT1,T2のゲートに一端が接続されたスイッチ6と、スイッチ6の他端に接続された電流設定回路5とを備える。電流設定回路5の内部回路とMOSトランジスタT1,T2がカレントミラー回路を構成し、スイッチ6がPWM制御信号に基づいてON/OFF切換動作を行う。

(もっと読む)

パワーオンリセット回路

【課題】RC回路の時定数を考慮せずに、電源の立ち上がりにおいて、例えば電源電位が最大値に到達した後にクロックを入力するように設定するだけで、適切なタイミングでパワーオンリセット信号を生成でき、パワーオンリセット信号を制御するクロックの初期の極性設定を不要とする。

【解決手段】パワーオン時に電源電圧の変化を検出してパルスを発生する信号発生回路10と、信号発生回路10のパルスによりリセットを解除し、クロックCLOCKにより電源電圧を取り込むDフリップフロップ4と、Dフリップフロップ4の出力信号を受け電源電圧VDDを取り込むDフリップフロップ5と、Dフリップフロップ5の出力信号をクロックCLOCKにより取り込み出力信号をパワーオンリセット信号PONとして出力し、パワーオンリセット信号PONが出力されるとDフリップフロップ5をリセットするフリップフロップ6とを設ける。

(もっと読む)

負荷断線検出回路

【課題】負荷に生じるフライバック電圧以上の耐圧を持つ負荷断線検出回路を提供する。

【解決手段】指標電圧出力回路17は、電磁コイルが接続される出力端子11dが開放状態になると、ノードN1の電圧VTrefに等しい指標電圧VTを出力端子11dから出力する。電磁コイルの電流が遮断されると、出力端子11dにフライバック電圧Vfbが発生する。分圧回路18は、フライバック電圧Vfbを1/mに分圧してウィンドコンパレータに出力する。ダイオードD3はフライバック電圧Vfbを阻止し、抵抗R8はダイオードD3がブレークダウンしたときの電流を制限する。

(もっと読む)

直列複製及び誤り制御符号化を用いる耐欠陥・耐故障性デマルチプレクサ

本発明の一実施形態は、耐欠陥・耐故障性デマルチプレクサ(図14及び図16)を構成する方法である。この方法は、ナノスケール、マイクロスケール又はさらに大きなスケールのデマルチプレクサ回路に適用することができる。デマルチプレクサ回路は1組のANDゲート(図9A及び図9B)と見なすことができ、各ゲートは、多数のアドレス線(910〜912及び920〜922)、又はアドレス線から派生する信号線と出力信号線(914及び924)との間に1つの可逆切替可能相互接続を含む。可逆切替可能相互接続はそれぞれ、1つ又は複数の可逆切替可能素子(906〜908及び916〜918)を含む。いくつかのデマルチプレクサの実施形態では、可逆切替可能素子として、NMOSトランジスタ(102)及び/又はPMOSトランジスタ(206)が用いられる。本発明の一実施形態を表す方法では、2つ以上の直列に接続されたトランジスタ(410、412及び411、413;1502)が可逆切替可能相互接続のそれぞれにおいて用いられ、これにより、直列に相互接続されたトランジスタの数よりも1だけ小さい数までの短絡欠陥は、可逆切替可能相互接続の故障には繋がらなくなる。さらに、誤り制御符号化技法を用いて、アドレス線から派生する付加的な信号線(1602、1604)及び付加的な切替可能相互接続(1610)を導入し、これによって、多数の個別の切替可能相互接続に開放欠陥があってもデマルチプレクサが機能することができるようにする。  (もっと読む)

(もっと読む)

負荷制御装置

【課題】 温度が上昇しても負荷駆動素子の発熱増大を抑制し、装置の小型化を可能とする。

【解決手段】 開示される負荷制御装置では、三角波生成回路1は、定電圧Vcに接続された、トランジスタQ2〜Q4からなるカレントミラー回路(定電流源)、トランジスタQ5〜Q7からなるカレントミラー回路(定電流源)及び抵抗R2により得られる定電流に基づいて、コンパレータCP1がコンデンサC1の電圧VC1と基準電圧Vt1とを比較することにより、コンデンサC1の充放電を切り換えて三角波信号を生成している。この負荷制御装置では、カレントミラー回路(定電流源)を構成するトランジスタQ2に対して、温度の上昇に伴ってその特性が変化するダイオードD1を付加している。

(もっと読む)

スイッチマトリクス

【課題】 各ポート間の挿入損失及び温度変化による影響を同じにしつつ、スイッチマトリクス全体としての挿入損失及び温度変化による影響を小さくすること。

【解決手段】 端子面にスイッチ端子が設けられた複数のスイッチ素子を用いて入力側から出力側を同軸ケーブルにより接続して構成されるスイッチマトリクスであって、前記複数の素子のうちの2つのスイッチ素子は端子面が対向するように位置し、前記2つのスイッチ素子以外のスイッチ素子は前記2つのスイッチ素子の対向する端子面の間の空間の近傍に位置する。

(もっと読む)

集積回路装置

【課題】個別に遮断制御が可能な3つ以上の電源供給源からそれぞれ電源供給され、かつ順次電源供給が遮断される3つ以上の集積回路から構成される集積回路装置において、集積回路の物理的配置によらず、集積回路間の信号線に挿入される電源遮断回路の制御を容易にする。

【解決手段】集積回路間を接続する信号線に挿入され接続先集積回路の電源遮断時に電源遮断回路の出力を固定状態に制御する電源遮断回路に電源遮断制御信号を与えるために、電源供給が遮断される順に集積回路を選択し、電源遮断回路を選択された集積回路より電源遮断順序が後になる集積回路側又は電源遮断しない集積回路側に挿入し、挿入された電源遮断回路に電源遮断制御信号を与える電源遮断制御回路2を選択された集積回路より電源遮断順序が後になる集積回路側又は電源遮断しない集積回路側に分散して形成する。

(もっと読む)

半導体記憶装置、電源検出器、半導体装置

【課題】電源投入検出回路の出力が取り得る電圧範囲における温度による変動を軽減して、フューズ情報を正確にラッチできる電源電圧最小値と半導体記憶装置が動作する電源電圧最小値の両方に十分なマージンを確保すること。

【解決手段】この半導体記憶装置は、外部電源(VEXT)にドレインおよびゲートが接続されるとともに、ソースをバックゲートに接続したnチャネル型MOSFET1と、nチャネル型MOSFETのソースおよびバックゲートに接続されたノードと、ノードの電位をもとに外部電源の投入を検出する検出部とを具備する。

(もっと読む)

パワーオンリセット回路

【課題】 電源電圧の立ち上がりや立ち下がり速度に依存せずに安定したリセットパルスを出力する。

【解決手段】 パワーオンリセット回路1には、起動時間調整部2、比較電圧発生部3、コンパレータ4、定電流源5、及びNch MOSトランジスタNT5が設けられている。起動時間調整部2はコンパレータ4に入力される入力電圧Vinと基準電圧Vrefの比較開始時間を調整し、比較電圧発生部3は電源電圧の立ち上がり或いは変化に対応して、抵抗分割された電圧を発生する。コンパレータ4は入力電圧Vinと基準電圧Vrefを入力し、比較増幅した出力信号Outを出力する。このため、電源電圧の立ち上がりや立ち下がり速度に依存せずに安定したリセットパルスがコンパレータ4から出力される。

(もっと読む)

電源装置

【課題】負荷の大きさを検出し、この検出した負荷の大きさに応じてPWM制御またはPFM制御の動作を選択的に行う場合に、その切り換え動作の安定化を図ることができ、かつ使い勝手が優れている電源装置の提供。

【解決手段】スイッチングレギュレータ2は、PFM制御回路20によるPFM制御またはPWM制御回路21のPWM制御によって出力電圧を所定値に制御するようになっている。負荷検出部3は負荷の大きさを検出し、この検出した負荷の大きさをPFM制御回路20とPWM制御回路21との動作を切り換えるための基準値と比較し、この比較の結果に基づいてその両回路の動作を選択的に切り換える。その基準値はヒステリシスを有し、そのヒステリシス幅が基準値調整端子5に入力する信号によって、外部から任意の値に調整できるようになっている。

(もっと読む)

半導体集積回路

【課題】プロセス変動にかかわらず、適切なリセットを発行するための技術を提供する。

【解決手段】動作用電源が供給されることによって所定の論理動作を行う内部回路(16)と、電波を受けることで生じた高周波電流を整流可能な整流回路(11)と、上記整流回路の出力から上記内部回路の動作用電源を生成するための電源回路(20)とを含んで半導体集積回路(100)が構成されるとき、上記内部回路内に設けられたモニタセル(160)と、上記モニタセルの論理状態に応じて上記内部回路をリセット可能なリセット回路(15)とを設ける。内部回路内の他のセルのプロセスばらつきをモニタセルに反映させ、上記モニタセルの出力電圧に基づいて、内部回路のリセット信号を形成することにより、プロセス変動応じて適切なリセットを発行する。

(もっと読む)

差動型スイッチドキャパシタCV変換回路

【課題】オフセット容量の大きな差動静電容量型センサであっても、2つのセンサキャパシタの実質的な容量差(信号成分)を初段の演算増幅器により高利得で電圧信号に変換することができる差動型スイッチドキャパシタCV変換回路を実現する。

【解決手段】電荷移転動作は、充電された第1・第2センサキャパシタCsa・Csbと補正キャパシタCoaを充電用電圧源±Vdと補正電圧源±Vocから切り離すとともに、第1・第2センサキャパシタCsa・Csbと補正キャパシタVoaを演算増幅器1の反転入力端子に接続し、第1・第2センサキャパシタCsa・Csbと補正キャパシタCoaの加算された充電電荷を帰還キャパシタCcvに移転させ、加算された充電電荷に比例した電圧を演算増幅器1の出力に発生させる。

(もっと読む)

電源用スイッチング装置

【課題】バッテリーと負荷の接続、遮断時に機械的な開閉接点間に生じるアークを十分に防止するとともに、バッテリーと負荷の接続、遮断の信頼性を高める電源用スイッチング装置を提供すること。

【解決手段】直流電源3のプラス端子、マイナス端子のそれぞれから負荷1,2側に接続される配線17,18のうちの少なくとも一方に直列に接続される機械的な開閉接点12a,14aを備えたリレー12,14と、開閉接点12a,14aに直列に接続されるノーマリオンの半導体スイッチ素子11,13とを有する。

(もっと読む)

高電圧スイッチング回路

【解決手段】高電圧スイッチング回路は、デプレッション型NMOSトランジスタと、エンハンスメント型PMOSトランジスタと、エンハンスメント型NMOSトランジスタを備える。制御回路は第1の制御信号と第2の制御信号を生成する。第1の制御信号はエンハンスメント型NMOSトランジスタを制御し、両方の制御信号の論理結合によってPMOSトランジスタを制御するためのバイアスを与える。PMOSトランジスタへバイアスがかかることによって、高電圧が回路出力へスイッチングされた後、ゲート電圧はアース電位よりも大きくなる。 (もっと読む)

信号処理回路のリセット制御装置及びリセット制御方法並びに信号処理回路のリセット制御回路挿入方法

【課題】複数の機能ブロックのリセット順序を考慮することなくリセットできると共に、所定の機能ブロックをリセットした場合であっても、他の機能ブロックにおいて、リセットによる信号変化の影響が生じることを抑制する。

【解決手段】複数の機能ブロック12A〜12Cとリセット管理部11とを備え、前記機能ブロック12Aと機能ブロック12Bとがリセット制御部13Aを介して接続され、前記機能ブロック12Bと機能ブロック12Cとがリセット制御部13Bを介して接続される。前記リセット管理部11において生成されたブロックリセット信号112A〜112Cは、前記複数の機能ブロック12A〜12Cに供給されて、各機能ブロック12A〜12Cではリセットが行われる。前記リセット制御部13A、13Bはリセット対象の機能ブロックから非リセット対象の機能ブロックへの入力信号の伝播を許容するか阻止するかを制御する。

(もっと読む)

101 - 120 / 158

[ Back to top ]