Fターム[5J055AX37]の内容

Fターム[5J055AX37]の下位に属するFターム

フェイルセーフ構成 (60)

Fターム[5J055AX37]に分類される特許

121 - 140 / 158

オープンドレイン出力回路

【課題】入力電源電圧が出力段のトランジスタの閾値電圧以下の低い領域にあっても、出力電圧の不要な持ち上がりを抑圧し、確実な回路動作を実現する。

【解決手段】出力用NMOSトランジスタ11のバックゲートは、定電流源25が接続されたバックゲート駆動用NMOSトランジスタ12のドレインに接続されており、出力用NMOSトランジスタ11が未だオンとならない入力電源電圧が低い領域にあっては、バックゲートに正の電圧が印加される一方、入力電源電圧が上昇すると、出力用NMOSトランジスタ11と共にバックゲート駆動用NMOSトランジスタ12がオンとされることで、バックゲートはグランドレベルとされるため、出力用NMOSトランジスタ11の閾値電圧の引き下げと、出力電圧の持ち上がりが抑制されるようになっている。

(もっと読む)

ブートストラップ回路

【課題】 低消費電力で信頼性の高いブートストラップ回路を提供する。

【解決手段】 電源VDRVの立上がりに、制御部70はプリチャージ信号S70に予備充電用のパルスを形成し、その後にPWM信号発生回路71がNMOS41をオンオフさせるパルス列を発生する。ブートストラップ回路50は、予備充電用パルスに基づきNMOS52を介してPMOS58を充電し、その後、PMOS58の充電電圧と電源VDRVの電圧を加算した電圧をPMOS56を介してNMOS60のゲートに与え、NMOS60をオンさせてキャパシタ61を充電する。NMOS41をオンさせるタイミングで、キャパシタ61の充電電圧をNMOS41のゲート・ソース間に与え、NMOS41をオンさせる。

(もっと読む)

電圧生成回路、データドライバ及び表示装置

【課題】複数の生成電圧の中からディジタルデータに対応した生成電圧の電圧降下を抑えて出力できる電圧生成回路、データドライバ及び表示装置を提供する。

【解決手段】電圧生成回路は、第1導電型MOSトランジスタにより構成される第1導電型の第1のセレクタと、各第2のセレクタが第1導電型MOSトランジスタにより構成される2a個の第1導電型の第2のセレクタと、第2導電型MOSトランジスタにより構成される第2導電型の第1のセレクタと、各第2のセレクタが第2導電型MOSトランジスタにより構成される2a個の第2導電型の第2のセレクタとを含む。第1導電型の第1及び第2のセレクタの各MOSトランジスタのチャネル幅方向は平行で、第1導電型の第2のセレクタの各第2のセレクタを構成するMOSトランジスタのうち第1導電型の第1のセレクタに接続されるMOSトランジスタがそのチャネル幅方向に隣接して配置される。

(もっと読む)

デッドタイム制御回路

【課題】 各温度で最適なデッドタイムを得ることができる温度特性調整機能を有し、又は、回路が大型化しコスト的に不利になることが無く、又は、デッドタイムの高精度な制御が可能なデッドタイム制御回路を提供する。

【解決手段】 基準電圧発生回路1と、オペアンプ2、トランジスタ11と抵抗3からなる電圧−電流変換部10と、カレントミラーと、遅延回路8及びAND回路9とを具備するデッドタイム制御回路において、負の温度特性を有する基準電圧発生回路1の出力電圧を電圧−電流変換部10によって電流変換し、その電流をカレントミラーによって伝達し、遅延回路8を構成する少なくとも1つのインバータに流れる電流を制御している。

(もっと読む)

高電圧双方向半導体スイッチのための駆動回路

【課題】デプレッション型素子である双方向性スイッチの独特な特徴を考慮して駆動回路および方法を改良する。

【解決手段】本願の一実施形態による双方向半導体スイッチを用いたハーフブリッジのための駆動回路は、ハイサイド双方向半導体スイッチを制御するよう動作可能なハイサイド駆動部を備え、ハイサイド駆動部は、双方向半導体スイッチに負バイアス電圧を供給して、ハイサイド双方向半導体スイッチをOFFにする。ローサイド駆動部は、ローサイド双方向半導体スイッチを制御するよう動作可能であってよい。負端子がハイサイド駆動部に接続された外部電圧源が備えられてよい。電圧源の負端子とハイサイド駆動部との間にハイサイド駆動スイッチが配置され、ローサイド駆動部がローサイド双方向半導体スイッチをONにする時に、ハイサイド駆動部を電圧源の負端子に接続するよう動作可能であってよい。

(もっと読む)

ブートストラップ回路並びにこれを用いたシフトレジスタ、走査回路及び表示装置

【課題】 単一導電型のトランジスタで構成されるシフトレジスタにおいて、回路の小型化及び低消費電力化を図る。

【解決手段】 第1の接点(ノードN1)の電圧が電源電圧よりも高くあるいは低くなることで出力に電源電圧の電圧を出力するブートストラップ回路を含んだシフトレジスタであって、前記第1の接点に2個以上直列接続されたトランジスタ(Tr1、Tr2)と、前期トランジスタのドレイン・ソース間電圧が電源電圧以下となるように前記トランジスタ間の第2の接点(ノードN2)に電圧を供給する手段と、前記第1の接点に接続されゲート電極が第1の入力端子に接続された第1の入力トランジスタ(Tr3)と、出力端子とクロック信号に接続されかつゲート電極に前記第1の接点が接続された出力トランジスタ(Tr7)を有し、出力トランジスタのゲート電極はブートストラップする期間以外、開放状態にならない。

(もっと読む)

車両の電子制御装置

【課題】 複数の系統(グループ)に区分された複数のECUから構成される車両の電子制御装置において、グループごとに設けられたリレーの異常を簡易な構成で検出する。

【解決手段】 複数の電子制御ユニット(ECU)1A〜1C,2A〜2Cは、複数のECUグループ10A,10Bに区分される。リレーRL1,RL2は、ECUグループごとに設けられ、対応のグループにおいて各ECUと電源30との間に接続される。各ECU間は、通信ネットワーク60に接続され、電源投入時には、通信機能に異常が発生しない限り、自身が通信可能であることを示すフラグを出力する。リレー異常検出部70は、それぞれのECUについて通信可能または通信不能を示す通信状態情報に基づき、ECUグループ間で通信状態情報が不一致であるときにリレーRL1,RL2の異常を検知する。

(もっと読む)

故障応答機能を備えた、パワー半導体スイッチを駆動するための回路装置、並びにそれに付属する方法。

【課題】2次側から1次側への故障応答をより簡単で且つ集積可能な手段を用いて可能とする、ブリッジ装置内のパワー半導体スイッチ用の回路装置、並びにそれに付属する方法を紹介する。

【解決手段】回路装置が1次側(20)と2次側(30)の間に故障ステータス伝送のためのダイオード(60)を有する。故障のない稼動時、2次側はダイオードのカソードに「ハイ」レベル(Vd)を印加し、故障のある稼動時には「ロー」レベル(Gd)を印加する。2次側から1次側への故障ステータスは、2次側が、開かれているBOTスイッチ(52)又は高抵抗の抵抗(70)を介してほぼグラウンド・基準電位上にあるためにダイオードを通じて電流の流れが行なわれることにより認識される。

(もっと読む)

リセット回路

【課題】 リセットシーケンスを電源ON時および電源OFF時において確実に守ることができるリセット回路を提供する。

【解決手段】 リセットIC2は、電源端子Vddへ電源V1が加えられた時、一定時間t1の間第1のリセット信号R1を出力した後リセットを解除し、電源端子Vddの電源V1がOFFとされた時リセット信号を”L”レベルとする。第2のリセットIC9は、電源端子Vddへ電源V2が加えられた時、一定時間t2の間第2のリセット信号R2を出力した後リセットを解除し、電源端子Vddの電源がOFFとされた時、リセット信号R2を”L”レベルとする。トランジスタ5、8は、第1のリセット信号R1のリセット状態が解除された時、第2の電源V2を第2のリセットIC9に加える。

(もっと読む)

誘導性負荷の駆動装置

【課題】 増幅部の温度特性に起因したシステムの性能低下を抑制すること。

【解決手段】 パワTr12と電流信号変換・増幅部13とが同一のソレノイド駆動IC11に内蔵され、さらに、ソレノイド駆動IC11の内部において、パワTr12からの発熱が電流信号変換・増幅部13に伝わる(熱伝達する)位置関係に配置されている点に着目し、電流信号変換・増幅部13の温度を速やかに上昇させる目的で、電流信号変換・増幅部13の温度が所定温度(例えば、常温)よりも低い場合、上述した駆動信号生成部は、駆動部からの発熱を促進するための発熱促進信号パターンの駆動信号を生成し、パワTr12は、この発熱促進信号パターンの駆動信号に応じて誘導性負荷の通電を制御することで、増幅部を加熱するための通電(加熱制御)を実行して、電流信号変換・増幅部13の温度を常温域まで短時間に上昇させる。

(もっと読む)

トレラント入力回路

【課題】 入力回路のしきい値を調整することなく、製造ばらつきに関わらず安定して動作するトレラント入力回路を提供する。

【解決手段】 入力パッド1と入力回路2との間にNチャネルMOSトランジスタにてなる降圧素子Tr3を介在させ、降圧素子Tr3のゲートに入力回路の電源VDDを供給して、入力パッド1に入力される高電圧信号を、電源VDD電圧以下に降圧して入力回路2に供給するトレラント入力回路であって、入力パッド1に高電圧信号が入力されたとき、降圧素子Tr3のバックゲート電圧を上昇させるバックゲート電圧制御回路を備えた。

(もっと読む)

PWM制御回路

【課題】 従来のデジタル処理回路を用いたPWM制御回路では、クロック信号に異常があったときには、回路全体の動作が停止してしまっていた。しかし、車両のECBシステム等では、システムの信頼性を保つ上で回路動作の停止を避けたい。

【解決手段】 PWM信号とクロック信号に基づきソレノイド駆動信号および還流側駆動信号を生成する駆動信号生成回路11、クロック信号監視回路16と、リニアソレノイド1を駆動するハイサイド側スイッチング素子14と、ハイサイド側スイッチング素子のオフ時の電流還流用の還流側スイッチング素子15と、各スイッチング素子を駆動するハイサイド側駆動回路12及び還流側駆動回路13とを備え、クロック信号が正常な場合には各駆動信号に基づいて各スイッチング素子を駆動し、異常な場合には前記PWM信号に基づいてハイサイド側スイッチング素子を駆動し、還流側スイッチング素子の駆動を停止する。

(もっと読む)

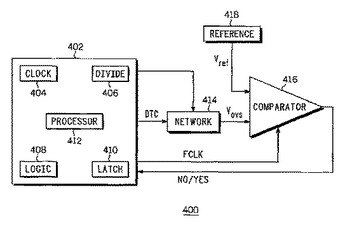

デジタル時定数トラッキング技術及び装置

プロセス、電圧及び温度の変動に起因して回路網(414)の時定数偏差を調整して雑音を無くす方法及び装置を提供する。当該装置(400)は、デジタル時定数が回路網(414)の公称時定数に対して相関されるクロック基準手段(404)を備える。相関されたデジタル時定数は、回路網(414)に印加され、そして出力充電/放電波形スイングが、所定の基準電圧と比較される。当該充電/放電波形スイングが基準電圧と一致しない場合、オフセット信号を発生する。オフセット信号が、制御回路(402)に印加され、当該制御回路(402)は、対応の同調信号を発生する。同調信号は、回路網(414)に印加されて、一致が達成されるまで内部部品を増分的又は減分的に調整する。当該装置(400)は、内蔵型で自己試験型のデジタル時定数トラッキング回路として構成されることでき、且つICチップ上に回路網(414)と一緒に統合化されることができる。  (もっと読む)

(もっと読む)

半導体メモリ装置

【課題】 パワーオンタイムに関与したトリップポイントの変化を最小限に抑制できるスタートアップ回路を提供する。

【解決手段】 外部電源電圧(VCC)を変換して内部電源電圧(VCCP)を発生する内部電源電圧発生回路(6)と、前記外部電源電圧の印加により所定レベルにクランプされるバイアス電圧(VBIAS)を発生するバイアス電圧供給回路(8)と、前記内部電源電圧を電圧源及び差動入力の一方とすると共に、前記バイアス電圧を差動入力の他方とする差動増幅回路を用いてスタートアップ信号(VCCH)を発生すると共に、前記バイアス電圧により動作制御されて前記差動増幅回路の出力端を初期化する初期化手段(26)を有するスタートアップ回路(10)と、を備える。

(もっと読む)

クロック制御装置及び電子機器

【課題】電源電圧の立ち上がりを緩やかにして電源や回路の保護を図ること、オーバートーンで期待した周波数のクロックを確実に得ること、並びに電源投入後可能な限り早い時点で何らかのクロックを得ることが可能なクロック制御装置を提供する。

【解決手段】所定のクロックを供給するクロック供給手段2と、所定時間を計測するタイマ4と、タイマ4を起動すると共にクロック供給手段2の動作を制御するコントローラ3と、を備える。コントローラ3は、外部制御手段5等の外部からのクロック制御指示に従ってクロック供給手段2の動作を停止させると共にタイマ4を起動し、タイマ4が所定時間の計測を終了した後に、クロック供給手段2の動作を再開させると共に外部に対してクロック制御完了を通告する。

(もっと読む)

スイッチ制御回路

【課題】制御対象スイッチのオン抵抗成分を十分に小さくして、アナログ信号の振幅値に依らずそのオン抵抗成分を一定にする制御を、回路規模を増大させずに、かつ制御精度や制御信頼性を損なうことなく行うことができるスイッチ制御回路を得る。

【解決手段】入力端INにはアナログ入力信号電圧Vinが印加される。クロック制御信号Φbが電圧Vddである期間では、制御対象SWaはオフ動作状態にあり、容量素子Cpに電源電圧Vddが充電される。クロック制御信号Φbが電圧0である期間では、MP5がオン動作状態になり、制御対象SWaのゲート電極にVdd+Vinなるオン制御電圧を印加する。制御対象SWaのVgsは常にVddに維持される。このとき、MP5のVgsはVddを超えないように制御されるので、MP5の特性変化や素子破壊が防止される。本回路を適用したアナログ回路の精度劣化や動作不良を防ぐことができる。

(もっと読む)

耐圧入力バッファ回路

【課題】 電源電圧、温度、プロセス変動等によっても立上り遅延のバラツキが小さくなり、且つ、立上り遅延と立下り遅延の差も小さくなるようにすること。

【解決手段】 電源電圧VDDより高い入力電圧Vinを電源電圧VDDより低い電圧に低下させる耐圧回路2と、耐圧回路2の出力電圧から高周波ノイズ成分を除去するRCフィルタ回路4と、RCフィルタ回路4の出力電圧に応じて反転/復帰するシュミットインバータ回路5と、耐圧回路2の出力電圧V1がハイレベルで且つRCフィルタ回路4の出力電圧が所定の電圧以上のときRCフィルタ回路4のRC時定数を小さな値に切り替える時定数切替回路8を設けた。

(もっと読む)

半導体装置及びその冗長救済方法

【課題】 大規模化した半導体装置の歩留向上および信頼性向上が容易に図れるようにすること。

【解決手段】 制御回路108からの制御信号S(i)によって電流測定タイミングになると、各分割論理回路ブロック1051〜r−1の静止電源電流値が測定される。そして制御回路108は、分割論理回路ブロック1051〜r−1の静止電源電流値と基準値とを比較して、静止電源電流が基準値を超える場合、判定信号(i)をLoレベルに設定する一方、静止電源電流が基準値を超えないときは判定信号(i)をHiレベルに設定する。そして、判定信号(i)がLoレベルである不良ブロックを冗長回路ブロック105rと置換するように、セレクタ1062〜r,1071〜r−1に切替え制御信号R(1)〜R(r)を出力し、入出力バスの接続を切り替え、その不良ブロックへの電源供給も停止する。

(もっと読む)

出力バッファ回路

【課題】高スルーレートでスルーレート変動の少ない出力バッファ回路を実現する。

【解決手段】NMOSトランジスタM3をONすることで容量C1と容量C2との容量比で出力トランジスタであるPMOSトランジスタM1のゲート電圧をしきい値電圧以下に低下させ、PMOSトランジスタM1をONさせ、同時に、電流源I1により最終的にPMOSトランジスタM1のゲート電圧を0Vにし、さらに、PMOSトランジスタM4をONすることで容量C3と容量C4の容量比で出力トランジスタであるNMOSトランジスタM2のゲート電圧をしきい値電圧以下に低下させ、NMOSトランジスタM2をONさせ、同時に電流源I2により最終的にNMOSトランジスタM2のゲート電圧を電源電圧レベルにする構成とし、出力トランジスタのゲート電圧を容量分圧制御で行う。

(もっと読む)

電力供給制御装置及び半導体装置

【課題】電力供給制御装置において、異常を精度高く検出しうる構成を提供する。

【解決手段】 電力供給制御装置10は、パワーMOSFET15と、パワーMOSFET15の電流量に応じたセンス電流が流れるセンスMOSFET16と、センス電流と閾値電流とに基づいて、パワーMOSFET15に流れる電流の異常検出を行う異常検出回路13とがワンチップ化されて半導体スイッチ素子11が構成されている。半導体スイッチ素子11の外部には、パワーMOSFET15のソース端子に接続され、他端が、半導体スイッチ素子11の外部端子P4と接続され、一端の接続点の電圧レベルVsに応じた電流を、外部端子P4を通して流す外付け抵抗12が設けられている。異常検出回路13は、外部端子P4に接続されると共に、外部端子P4を通して流れる電流に応じた閾値電流Ia、Ibと、センス電流とを比較することに基づき異常信号SC,OCを出力する。

(もっと読む)

121 - 140 / 158

[ Back to top ]