Fターム[5J055BX16]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 駆動一般 (1,722)

Fターム[5J055BX16]に分類される特許

161 - 180 / 1,722

駆動回路

【課題】複数のスイッチ素子を備える装置を小型化すること。

【解決手段】駆動回路1は、キャパシタC21と、充電部を構成する抵抗R21およびダイオードD21と、を備える。キャパシタC21は、スイッチ素子Q11のゲートと、スイッチ素子Q21のゲートと、の間に設けられ、制御部22の端子Y3には、スイッチ素子Q11のゲートが接続されるとともに、キャパシタC21を介してスイッチ素子Q21のゲートが接続される。抵抗R21およびダイオードD21で構成される充電部は、スイッチ素子Q21のゲートとソースとの間に設けられる。

(もっと読む)

並列接続された半導体スイッチ素子の駆動装置

【課題】 並列に接続された複数の半導体スイッチ素子に過電流が流れているか否かを精度良く検出可能な駆動装置等を提供する。

【解決手段】 駆動装置100は、第1の半導体スイッチ素子IGBT1と、第1の半導体スイッチ素子IGBT1の第2の端子Eでの電流を検出するための検出ノードSOと、第1の半導体素子スイッチIGBT1と並列に接続される少なくとも1つの半導体スイッチ素子IGBT2と、第1の半導体スイッチ素子IGBT1及び少なくとも1つの半導体スイッチ素子IGBT2を駆動する駆動回路DRと、第1の抵抗RG1と、少なくとも1組の抵抗RG2,RE2及び少なくとも1組のコモンモードフィルタLG2,LE2とを備える。RG1の抵抗値は、RG2の抵抗値とRE2の抵抗値とを加算した値に等しい。駆動回路DRの第2の駆動ノードEOは、何れの抵抗も介さず、第1の半導体スイッチ素子IGBT1の第2の端子Eと直接に接続される。

(もっと読む)

ドライバ回路

【課題】 出力オフ時のスイッチング時間を短くすることのできるドライバ回路を提供する。

【解決手段】 実施形態のドライバ回路は、を駆動する出力用MOSトランジスタMV1が、電源端子VDDと誘導性負荷RLが接続される出力端子OUTとの間に接続され、抵抗R1が、出力用MOSトランジスタMV1のゲート端子とゲート電圧印加端子VGとの間に接続され、ゲート電圧印加端子VGに一端が接続された抵抗R2と、一端が抵抗R2の他端に接続され、他端が接地端子GNDに接続され、出力用MOSトランジスタMV1を制御する制御信号VSWにより導通が制御されるNMOSトランジスタMD1とを備える。さらに、このドライバ回路は、一端が抵抗R1の他端に接続され、他端が出力端子OUTに接続され、NMOSトランジスタMD1の一端から出力される信号により導通が制御されるPNPトランジスタQ1を備える。

(もっと読む)

負荷駆動装置

【課題】短絡時にクランプ解除が為されてしまうことでスイッチングデバイスに過電流が流れることを防止する。

【解決手段】短絡状態が検出されたことを示す短絡信号Yが短絡検出フィルタ6を介することなくクランプ回路3に直接入力されるようにする。これにより、短絡時動作として、クランプ解除フィルタ時間の経過が短絡検出フィルタ時間の経過よりも先であった場合にも、クランプ回路3によるクランプ動作を継続することが可能となる。したがって、短絡時にクランプ解除が為されてしまうことでIGBT1に過電流が流れることを防止することができる負荷駆動装置とすることが可能となる。

(もっと読む)

電源回路

【課題】 特殊なスイッチを用いず、手動による動作停止およびコントロール回路からの制御による動作停止が可能であり、無駄な電力消費が少ない電源回路を提供する。

【解決手段】 リレースイッチSW2がOFFの状態でスイッチSW1が押圧されると、交流電圧が給電線101および103間に与えられ、負荷400に対する直流電圧が立ち上がる。すると、コントロール回路210は、リレースイッチSW2をONさせる。このとき、充電回路110および120では、電解コンデンサC1およびC2の充電が行われるが、電解コンデンサC2の充電電流が小さいため、LED104は発光しない。リレースイッチSW2がONの状態で、スイッチSW1が押圧された場合、放電回路130が開くため、電解コンデンサC2が急速充電される。この場合、LED104が発光し、コントロール回路210は、リレースイッチSW2をOFFにする。

(もっと読む)

スイッチ制御回路、及び印刷装置

【課題】スイッチがオフ状態(非導通状態)である場合の消費電力を低減する。

【解決手段】スイッチ制御回路は、制御端子に印加される電圧に基づいて、第1の電源線VDDから供給される電力を出力状態と非出力状態との間で切り替えるP−FET11と、第1の電源線VDDと制御端子との間に接続される抵抗R1と、制御端子と第2の電源線との間に、第1のコンデンサーC1と第2のコンデンサーC2が直列に接続されているコンデンサー分圧回路13と、第1のコンデンサーC1と並列に接続され、自素子の両端間の電位差が、予め定められた閾値以上である場合に導通状態になり、電位差が閾値未満である場合に非導通状態になる制御素子(ZD)と、第2のコンデンサーC2と並列に接続され、自スイッチの両端間を導通状態と非導通状態との間で切り替えるスイッチSWと、を備える。

(もっと読む)

誘導性負荷の駆動回路

【課題】スイッチング素子のオンオフによる誘導性負荷の電流応答性を良好なものとしながら駆動回路内の発熱をより抑制する。

【解決手段】誘導性負荷10を駆動する駆動回路20に、誘導性負荷10と並列接続され且つ互いに直列接続された第1の抵抗42および第2の抵抗44と、第2の抵抗44に並列接続されたコンデンサ46と、誘導性負荷10と並列接続されゲートが抵抗42と第2の抵抗44(コンデンサ46)との接続点に接続されドレインがグランドに接地されたNチャネル型のFET32と、FET32のソースと電源ライン24との間に介在しドレインからソースの方向を順方向とする第1のダイオード34とを設ける。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3を介して、入力電圧Vin2がトランジスタT2のゲートに入力される。そのため、入力電圧Vin1,Vin2がともにハイとなったときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

負荷駆動装置

【課題】短絡保護のためのクランプ電圧の設定に基づいて、損失を抑制することが可能な負荷駆動装置を提供する。

【解決手段】IGBT1の温度、出力電流、ミラー電流もしくはゲート閾値電圧Vthを検出し、これらのいずれかに基づいてミラー電圧Vmirrorのバラツキに応じたクランプ電圧を演算する。これにより、クランプ電圧をその状況下でのミラー電圧Vmirrorに対応する値に低く抑えることが可能となり、クランプ電圧をミラー電圧Vmirrorのバラツキの最大値、つまりすべての環境変化等を含めた最大値を考慮して設計する場合と比較して、クランプ電圧を小さく抑えられる。したがって、クランプ時にIGBT1を損失が大きくなることを抑制しつつ、短絡耐量を向上することが可能となる。

(もっと読む)

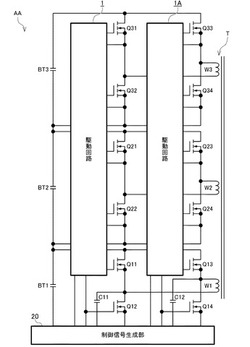

スイッチング回路装置及び制御回路

【課題】スイッチングトランジスタを適切にオフ動作する。

【解決手段】スイッチング回路装置は,高電位端子に接続されたドレインと低電位電源に接続されたソースとゲートとを有し,高電位端子と低電位電源との間に接続されたスイッチングトランジスタと,入力制御信号に応答して,スイッチングトランジスタのゲートにスイッチングトランジスタの閾値電圧より高い高電位と前記低電位電源の電位とを有する駆動パルスを出力する駆動回路とを有し,駆動回路は,スイッチングトランジスタのゲートとソースとの間に設けられた第1の駆動トランジスタを含む第1のインバータを有し,駆動パルスにより前記スイッチングトランジスタがオンからオフに変化するときに,第1の駆動トランジスタが導通してスイッチングトランジスタのゲートとソース間を短絡する。

(もっと読む)

電圧変換回路及び不揮発性半導体記憶装置

【課題】チャージポンプ回路を駆動するクロックバッファ回路に流れる瞬時電流を抑制すること。

【解決手段】

第1のトランジスタ(T11)のドレインを第1のキャパシタ(C11)によって第1の制御信号(DCLK10)に応じて昇圧駆動する第1のバッファと、第1のトランジスタ(T11)のゲートを第2のキャパシタ(C12)によって第2の制御信号(GCLK10)に応じて昇圧駆動する第2のバッファとから構成される電圧変換回路おいて、

第1のバッファは,第1の制御信号(DCLK10)の遷移時の駆動能力が,第2の制御信号(GCLK10)の遷移時の駆動能力よりも低いことを特徴とする電圧変換回路。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

パワー半導体スイッチの制御回路及びその制御方法

【課題】寄生容量の影響を最少化させることのできる、パワー半導体スイッチの改良された制御方法及び制御装置を提供する。

【解決手段】パワー半導体スイッチの制御接続端信号を生成するための信号処理ユニットを備えた、パワー半導体スイッチを制御する制御回路において、少なくとも一つの半導体素子が、定められたパワー半導体スイッチのコレクタ・エミッタ電圧を越えた時に、導通作動され、半導体素子の出力端が導電性の接続線を通じて抵抗直列回路の抵抗の間の接続点と、或いは信号処理ユニットと接続されている抵抗直列回路の出力端と接続されており、半導体素子のブレークダウン電圧が、半導体素子の出力端の電位が、パワー半導体スイッチがスイッチオン状態にある時のパワー半導体スイッチの制御接続端の電位よりも高くなるように選ばれている。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

スイッチング回路およびスイッチング回路を用いた撮像装置

【課題】EM−CCDのCMG駆動回路からEM−CCDの出力信号への飛び込みを低減しながら、負荷容量CMG電圧の振幅の減衰を防ぎ、矩形波特性を改善する。

【解決手段】論理バッファとPchMOSとNchMOSのゲート間にフェライトビーズとダイオードの並列接続を挿入し、MOSがターンオフする方向にダイオードが接続されているスイッチング回路において、PchMOSのドレインソース間導通抵抗が2オーム以上あり、PchMOSのドレインとNchMOSのドレインとが1オーム以上の抵抗で接続され、PchMOSのドレインと容量負荷間に、スイッチング基本波周波数におけるインピーダンスがスイッチング基本波周波数における前記容量性負荷のインピーダンスの1/2より低いインピーダンスのフェライトビーズを直列接続する。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

161 - 180 / 1,722

[ Back to top ]