Fターム[5J055BX16]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 駆動一般 (1,722)

Fターム[5J055BX16]に分類される特許

201 - 220 / 1,722

スイッチング素子駆動回路

【課題】 電力伝送効率がよく、より小型のスイッチング素子駆動回路を提供する。

【解決手段】 実施形態に係るスイッチング素子駆動回路は、電力変換装置を構成するスイッチング素子と、前記スイッチング素子のオン/オフを切り替えるためのゲート信号を発生する制御演算手段と、前記ゲート信号を変調する為の所定周波数の交流信号を発生する発振手段と、前記発生されたゲート信号の立ち上がり及び立下りの各所定時間内において、前記交流信号の振幅を変化させ、前記ゲート信号を変調する変調手段と、前記変調手段にて変調されたゲート信号を復調し、前記スイッチング素子のゲートに供給する復調手段と、

前記制御演算手段と前記スイッチング素子間の絶縁を確保した上で、前記変調手段にて変調されたゲート信号を前記復調手段に伝送し、プリント基板上に実装されたトランスとを具備する。

(もっと読む)

電子装置

【課題】電流制御用トランジスタ、電流検出用抵抗及びオフ駆動用スイッチング素子の少なくともいずれかの異常を検出できる電子装置を提供する。

【解決手段】制御回路は、正常時のミラー期間Tmの終了時t4におけるIGBT110dのゲート電圧がミラー電圧Vmより高い場合、電流制御用FET121aのショート故障、又は、電流検出用抵抗121bのショート故障が発生していると判断する。具体的には、IGBT110dのゲート電圧の立ち上がり時t2を基準として、所定時間T1経過後のt4におけるIGBT110dのゲート電圧に基づいて異常を検出する。これにより、電流制御用FET121a又は電流検出用抵抗121bの異常を検出するころができる。

(もっと読む)

複合半導体装置

【課題】電子回路の誤動作を防止でき、かつ、電力変換装置の小型化に寄与する複合半導体装置を提供する。

【解決手段】複合半導体装置10は、第1の端子G1から入力される信号に応じて第2の端子C1から第3の端子E1へ電流を流す第1のパワー半導体素子13と、第1の端子G2から入力される信号に応じて第2の端子C2から第3の端子E2へ電流を流す第2のパワー半導体素子16が同一基板(チップ)20内に形成された半導体装置であって、第2のパワー半導体素子16の第3の端子E2は、第1のパワー半導体素子13の第1の端子G1に電気的に接続されており、第1のパワー半導体素子13の第2の端子C1の電位が時間経過とともに増加したとき、第2のパワー半導体素子16の第3の端子E2を介して第1のパワー半導体素子13の第1の端子G1に電荷をチャージする電流路を備えた。

(もっと読む)

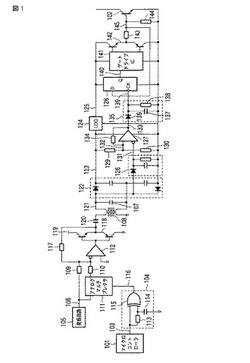

負荷駆動回路

【課題】複数の電源電圧条件に対して電流制限特性が追従し、負荷特性に適した電流制限を行なう負荷駆動回路を提供する。

【解決手段】図1に示す負荷駆動回路は、電源及び負荷に接続された出力MOSトランジスタと、出力MOSトランジスタの出力電圧に応じて、出力MOSトランジスタに流れる出力電流を複数段階の制限電流に制限すると共に、制限電流が切り替わる際の出力電圧を電源電圧の変化に基づいて切り替える電流制限値切り替え回路と、を備える。その結果、段階的に電流制限を行い、過剰な電流制限となることを妨げ、負荷条件の拡大を図る。さらに、電流制限値の切り替えを電源電圧に対応させて行なうため、当初の電源電圧条件とはことなる電源電圧で使用したとしても、電流制限特性が電源電圧の変動に追従し、全体として負荷特性に適した電流制限を行なうことができる。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

誘導性負荷駆動装置

【課題】チャンネル毎に独立した駆動指令信号で誘導性負荷を駆動し、チャンネル数や駆動周波数にかかわらず各チャンネルのオフタイミングを自律的に調整する。

【解決手段】マスク信号生成回路3は、何れかのチャンネルの出力トランジスタTkがオフしたことを検出すると、当該オフした時点から、当該オフしたチャンネルの出力端子Pkの電圧Vkが所定のしきい値電圧Vtk以下に低下する時点まで、他のオンしているチャンネルのマスク信号ManをHレベルにし、当該オフ移行チャンネルおよび他のオフしているチャンネルのマスク信号ManをLレベルのまま保持する。その結果、他のオンしているチャンネルの駆動指令信号SnがLレベルに変化しても、駆動信号DnはHレベルのまま保持され、出力トランジスタTnのオフ移行動作が禁止される。

(もっと読む)

リーク補償された電子スイッチ

【課題】電子スイッチの開放されたスイッチを通したリーク電流は、信号クロストークを引き起こす。

【解決手段】スイッチング用の電子回路は少なくとも4個の電子スイッチ200のセット100を備える。第1サブセット110の少なくとも2個の電子スイッチ210,230は直列接続され、第2サブセット120の少なくとも2個の電子スイッチ220,240は直列接続される。前記第1サブセット110の第1電子スイッチ210に接続される第1バッファ310、及び前記第2サブセット120の第2電子スイッチ220に接続される第2バッファ320を備え、前記第1バッファ310は開状態における前記第1電子スイッチ210を通した電圧降下を最小化し、前記第2バッファ320は開状態における前記第2電子スイッチ220を通した電圧降下を最小化する。また2個のサブセット110,120の間に配され、グランドに接続されたスイッチ410を備える。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

負荷駆動システム

【課題】制御回路ICと駆動回路ICとの間を接続する信号線に印加されるノイズの対策をより適切に行うことができる負荷駆動システムを提供する。

【解決手段】ECU11側に、複数の駆動回路に対してそれぞれ駆動制御信号を出力するタイミングに同期して、それぞれ異なるレベルの電圧を許可判別信号として出力する許可判別信号出力回路13を備える。また、EDU14側に、複数の駆動回路に対して、対応する駆動制御信号がアクティブになると共に、許可判別信号の電圧が対応する駆動回路について定められているレベルになると、駆動制御信号を対応する駆動回路に出力する駆動制御信号出力回路17を備える。

(もっと読む)

ドライバ回路

【課題】回路構成素子数の少ないドライバ回路を提供する。

【解決手段】L1とL2は伝送線路、TRはトランス、TR1とTR2は該トランスの一次側端子、TPは上記トランスの一次側中点タップ、S1とS2は送信回路である。また、Roは伝送線路の終端抵抗である。各々の送信回路は、NPNトランジスタQ1またはQ2、第一の抵抗R1またはR4、第二の抵抗R2またはR5、第三の抵抗R3またはR6からなる。また、T1とT2は、それぞれ、第一と第二の制御入力端子である。さらに、VCCは正電圧源である。そして、上記トランスの一次側中点タップTPは、上記正電源VCCに接続される。

(もっと読む)

ソレノイド駆動装置

【課題】駆動時に発生する熱を低減できるソレノイド駆動装置を提供する。

【解決手段】ソレノイド駆動装置100において、第1リレー20は、第1電源部30とソレノイド40との接続をオンまたはオフする。第2リレー22は、第2電源部32とソレノイド40との接続をオンまたはオフする。統合IC10は、第1リレー20および第2リレー22からのソレノイド40への通電を切り替え、ソレノイド40への通電を切り替える間、第1リレー20および第2リレー22のそれぞれの通電をともに所定時間オン状態にするよう制御する。第1トランジスタ60は、第2電源部32と第1リレー20との接続をオンまたはオフする。第1リレー20または第2リレー22に不具合が生じた場合、統合IC10は、第1トランジスタ60または第2トランジスタ62の一方をオンする。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

過電流保護装置

【課題】IGBT素子の短絡耐量を向上させ得る過電流保護装置を提供する。

【解決手段】過電流保護装置20では、各IGBT11a〜11fにゲート電圧Vgを印可するゲート駆動回路15に対してオフ信号を出力することで当該ゲート電圧Vgの印可を停止可能な保護回路22と、直流電源Eの電源電圧を制御可能な電源電圧制限回路23と、電源電圧を平滑化する平滑コンデンサCに蓄積された電荷を放電可能な放電回路24と、が設けられている。そして、電流検出部21により過電流が検出されると、保護回路22によりゲート電圧Vgの印可が停止され、電源電圧制限回路23により電源電圧が低減され、放電回路24により平滑コンデンサCに蓄積された電荷が放電される。

(もっと読む)

マルチチャネル・パルス幅変調信号生成装置及び方法、並びにこれを具備するLEDシステム

【課題】マルチチャネル・パルス幅変調信号生成装置及び方法、並びにこれを具備するLEDシステムを提供する。

【解決手段】複数の負荷を駆動する技術に係り、具体的にはLEDのようなパルス幅変調方式で駆動される複数の負荷のターンオン・タイミングを分散させることにより、安定動作を実現可能な複数のパルス幅変調信号を生成するマルチチャネル・パルス幅変調信号生成装置及び方法、並びにこれを具備するLEDシステムに関したものであり、該生成方法は、周期及びパルス幅のうち少なくとも一つを設定する段階、及び周期及びパルス幅を有する複数のパルス幅変調信号を出力する段階を含み、該出力する段階は、周期とパルス幅との差に対応する位相差を有する少なくとも1対のパルス幅変調信号を出力する段階を含むことを特徴とし、該方法及び装置は、複数の負荷のターンオン・タイミングを分散させ、安定動作を実現可能な複数のパルス幅変調信号を提供する。

(もっと読む)

電圧駆動型スイッチングデバイスの駆動回路

【課題】ターンオン時のゲート電流を所望の電流値に高精度に設定でき、スイッチング損失の低減が可能な電圧駆動型スイッチングデバイスの駆動回路を得る。

【解決手段】IGBT1のゲート端子に接続され、駆動用パルス信号2のオン/オフゲート制御信号に基づき、IGBT1をターンオン/ターンオフさせるゲート信号を前記ゲート端子に出力するゲート駆動定電流回路が示されている。このゲート駆動定電流回路は、正電源3とGND電位4間に直列に接続された第1の抵抗5と第1のトランジスタ15と第2の抵抗6と制御信号伝達トランジスタ7、および正電源3とIGBT1のゲート端子間に直列に接続されたゲートオン抵抗8と定電流出力トランジスタ9を備え、第1のトランジスタ15のベース端子は第1のトランジスタ15のコレクタ端子と短絡接続されている。

(もっと読む)

電流スイッチ回路およびDA変換器

【課題】差動出力電流のグリッチを打ち消しつつ、電源およびグランドに発生したノイズを打ち消す。

【解決手段】スイッチトランジスタM1、M2は、差動入力電圧Dip、Dimに基づいてスイッチング動作することで入力電流Iinを電流Ii1、Ii2に変換し、雑音電流発生回路1は、入力電流源2を介して流れる雑音電流を模擬したダミー電流Ibを生成し、スイッチトランジスタM3、M4は、差動入力電圧Dip、Dimに基づいてスイッチング動作することでダミー電流Ibを電流Ii3、Ii4に変換し、電流Ii1、Ii2に逆相的に重畳する。

(もっと読む)

スイッチング素子の駆動回路

【課題】スイッチング素子S*#のオン状態への切り替えによってこれを流れる電流が急激に大きくなると、ツェナーダイオード40およびクランプ用スイッチング素子42を備えて構成されるクランプ回路による対処が間に合わなくなるおそれがあること。

【解決手段】スイッチング素子S*#のオン操作指令に伴い、まず制限用電圧VLを端子電圧とする直流電圧源25を電源とし、定電流用スイッチング素子27を用いてスイッチング素子S*#のゲート充電処理を行う。そして、所定時間が経過することで、定常用電圧VH(>VL)を端子電圧とする直流電圧源22を電源とし、定電圧用スイッチング素子23を用いてスイッチング素子S*#のゲート充電処理を行う。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

駆動回路

【課題】電圧駆動型素子のスイッチング特性におけるトレードオフ関係を改善する駆動回路を提供すること。

【解決手段】駆動回路1は、ゲート抵抗R1とそのゲート抵抗R1に対して並列に接続されている分岐回路部23を備えている。分岐回路部23は、分岐ゲート抵抗R3とツェナーダイオードZD1を有するとともに、分岐ゲート抵抗R3とツェナーダイオードZD1が直列に接続されている。ツェナーダイオードZD1のカソードが駆動電源V1の正極端子14側に接続されており、ツェナーダイオードZD1のアノードがトランジスタTr1の制御端子12側に接続されている。

(もっと読む)

スイッチング素子駆動回路

【課題】スイッチング素子駆動回路において、スイッチング素子のスイッチング損失を抑制する。

【解決手段】 ゲート電圧検出回路201は、スイッチング素子11のゲート電圧Vgsを検出し、このゲート電圧がスイッチング素子11の閾値電圧未満に設定された所定電圧未満のとき、Hレベルの昇圧指示信号を出力する。電圧制御回路103は、前記昇圧指示信号がLレベルの間は、制御電源102の所定電圧V1をそのまま出力し、前記昇圧指示信号がHレベルの間は、前記所定電圧V1を昇圧した電圧V2を出力する。駆動信号出力回路104は、PWMパルス出力回路111から出力されるPWMパルスの電圧を電圧制御回路103から出力される電圧に増幅する。従って、駆動信号出力回路104からスイッチング素子11への駆動信号は、前記PWMパルスがHレベルになった時に、先ず昇圧された電圧V2となり、スイッチング素子11のゲート電圧Vgsが所定電圧にまで上昇すると、所定電圧V1となる。

(もっと読む)

201 - 220 / 1,722

[ Back to top ]