Fターム[5J055BX16]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 駆動一般 (1,722)

Fターム[5J055BX16]に分類される特許

141 - 160 / 1,722

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

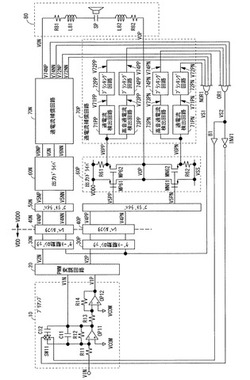

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

半導体スイッチング素子駆動回路

【課題】 高コスト化、サイズ大型化を抑制し、短絡保護回路が制限する電流値がばらついても、過電流保護回路を確実に作動させる半導体スイッチング素子駆動回路を提供する。

【解決手段】半導体スイッチング素子駆動回路は、ゲート端子への電圧の印加により第1端子および第2端子間に主電流を流す半導体スイッチング素子Q1と、主電流の大きさに比例する電流値または電圧値が閾値を超えたとき、主電流が所定時間の間、所定の電流値を超える過電流となったと判断して主電流を低下させる過電流保護回路OPと、主電流が所定時間より短時間で過電流よりさらに大きい過電流となる場合に、ゲート端子に印加するゲート電圧を過電流保護回路による主電流の低下よりも早く低下させる短絡保護回路SPと、短絡保護回路の主電流の低下作動時に閾値を小さくする閾値変更回路TCと、を有する。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

負荷駆動装置

【課題】急激なアンダーシュート波形が生成されることにより発振状態になって不安定な動作を引き起こすことを防止する。

【解決手段】パワー素子4をオンさせる際に、パワー素子4の制御端子41に比較的大きな電流を供給することで制御端子41の電圧を比較的大きな勾配で上昇させつつ、制御端子41の電圧がクランプ電圧に至ってから電圧状態が安定化するまでは、制御端子41への比較的大きな電流の供給を保持する。そして、制御端子41の電圧状態が安定化した後に、制御端子41への電流供給が定電流回路31のみから為されるようにし、比較的小さな電流が制御端子41に供給されるようにする。

(もっと読む)

負荷駆動装置

【課題】よりゲート電圧の傾きのバラツキを小さくすることで、スイッチング損失や電圧サージおよびピーク電流のバラツキを小さくする。

【解決手段】オフ保持デバイス5に対してオフ許可信号が禁止状態から許可状態に切り替わったことが伝わることを制御遅延演算回路6によって遅延時間だけ遅らせるようにする。これにより、遅延時間経過後に、既に定電流の狙い値まで達して安定した値になっている定電流駆動回路30の出力電流をスイッチング素子1のゲート1aに供給されるようにできる。したがって、ゲート電圧の立ち上がり傾きのバラツキを小さくすることができ、スイッチング損失や電圧サージおよびピーク電流のバラツキを小さくすることが可能となる。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

過電流保護電源装置

【課題】直流電源11からスイッチ用のFET12を経て負荷14へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】FETのドレイン・ソース間電圧に比例した電流Iを生成する電流変換回路4と、容量素子を含む一次遅れ回路として構成された過電流検出用電圧発生回路6とを直列接続し、その接続点Sの電圧を過電流検出用電圧VS とする。過電流検出回路5から制御回路3へ過電流検出信号が入力されて来たとき、制御回路3はFET12をオフする。過電流検出用電圧発生回路6の回路定数の設定を工夫することにより、VS を速やかに大になるようにすることが出来、1種類の保護回路で大過電流時にも保護が出来る。

(もっと読む)

スイッチング回路装置及びそれを有する電源装置

【課題】スイッチング時の電流の急激な変化を抑制しオン状態でのオン抵抗を抑制する。

【解決手段】電源回路内の第1のノードと第2のノードとの間に設けられるスイッチング回路装置であって,前記第1または第2のノードにインダクタが接続され,第1のノードと第2のノードとの間に設けられ第1のゲート幅を有する第1のトランジスタと,第1のノードと第2のノードとの間に第1のトランジスタに並列に設けられ第1のゲート幅より大きい第2のゲート幅を有する第2のトランジスタと,電源回路の出力電圧に応じて生成される制御信号に応答して,第1のトランジスタをオン,オフに駆動する第1の駆動信号と,第2のトランジスタをオン,オフに駆動する第2の駆動信号とを,時間的にずらして出力する駆動信号生成回路とを有する。

(もっと読む)

電子制御装置

【課題】電流検出用の抵抗を使用せず、簡易回路で負荷ショートの保護が可能な電子制御装置を得る。

【解決手段】パルス発生源3と第2のスイッチング素子21との間に接続されたコンデンサ23を有するトリガ回路と、負荷4と第1のスイッチング素子11との交点と第2のスイッチング素子21のベース端子との間にダイオード25を介して接続されるラッチ回路を有する制御回路を備え、パルス発生源が駆動信号を出力時は、トリガ回路を介し所定時間第2のスイッチング素子21をオンし、第1のスイッチング素子11もオンさせ、前記交点の電圧で、ラッチ回路を介し第2のスイッチング素子21のオン状態を継続させる。駆動信号の停止時は、第1、第2のスイッチング素子は共にオフとし、負荷ショートが発生した時は、パルス発生源3の駆動信号が出力されている場合でも、交点の電圧で、ラッチ回路を介して第2のスイッチング素子21をオフし、第1のスイッチング素子11もオフする。

(もっと読む)

DC−DCコンバータ

【課題】耐高電圧スイッチ回路を通常のMOSトランジスタを用いて構成するとともに、論理回路を停止する時間を大幅に削減して低電力性能を向上させるために、初期化を高速に行うことができるDC−DCコンバータを提供する

【解決手段】チャージポンプ回路1と、その電源のオン・オフを行う第1のスイッチ用MOSトランジスタ3から構成されるDC−DCコンバータにおいて、チャージポンプ回路1の電源オフ時に、チャージポンプ回路の出力端子の寄生容量に充電された電荷を直列接続された第2および第3のスイッチ用MOSトランジスタ4,5を介して放電する構成である。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に、第1の主電極Dswと第2の主電極Sswの間に配置された制御電極Gswを有するスイッチング素子Tswと、スイッチング素子Tswの第1の主電極Dswにアノード端子が接続された第1の整流素子D1、第1の整流素子D1のカソード端子に第1の主電極DD1が接続され、スイッチング素子Tswの制御電極Gswに第2の主電極SD1が接続された第1の駆動素子TD1、スイッチング素子Tswの制御電極Gswに第1の主電極DD2が接続され、スイッチング素子の第2の主電極Sswに第2の主電極SD2が接続された第2の駆動素子TD2、及び、第1の駆動素子TD1の制御電極GD1と第2の駆動素子TD2の制御電極GD2にそれぞれ入力される制御信号を受信する入力端子IN_H,IN_Lを有する駆動回路10とを備える。

(もっと読む)

スイッチング装置、スイッチングモジュール

【課題】本発明は、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

(もっと読む)

負荷駆動装置

【課題】クランプ回路が未使用状態なのか断線状態なのかを判別する。

【解決手段】温度センサ1hの出力が入力される温度検出端子14a〜14cを利用し、クランプ回路5a〜5cや温度検出回路7a〜7cの一部がパワーモジュール1に接続されないときには温度検出端子14a〜14cの電位に基づいて温度センサ1hが接続されていない断線無効状態を検出する。例えば、温度検出端子14a〜14cのうち温度センサ1hに接続されない端子に断線検出無効化閾値Vth3以上の電圧を印加することで、温度検出端子14a〜14cが温度センサ1hに接続されていないことを検出する。これにより、クランプ回路5a〜5cに接続されるクランプ端子11a〜11cの電位に基づいて断線検出を行う際に、断線状態なのか断線無効状態なのかを温度検出端子14a〜14cの電位に応じて判定できる。

(もっと読む)

半導体スイッチング素子駆動装置

【課題】半導体スイッチング素子の温度変化によるサージ電圧の発生および変動を抑制すると共にスイッチング損失を低下させることができる半導体スイッチング素子駆動装置を提供する。

【解決手段】各切替スイッチ42a、42bが駆動信号に従ってオン/オフすることにより、駆動手段40が半導体スイッチング素子10の制御端子11に駆動電流を供給する。一方、温度検出手段20によって半導体スイッチング素子10の素子温度または半導体スイッチング素子10の動作環境温度を検出する。そして、駆動手段40は、温度検出手段20によって検出された素子温度または動作環境温度に従って制御端子11に印加する駆動電流の大きさを変更する。これにより、半導体スイッチング素子10の温度変化によるサージ電圧の発生および変動が抑制され、スイッチング損失が低下する。

(もっと読む)

半導体スイッチング素子駆動装置

【課題】サージの発生を抑制すると共に半導体スイッチング素子のスイッチング速度を向上しつつ、回路規模を小さくすることができる半導体スイッチング素子駆動装置を提供する。

【解決手段】時間設定手段40から短絡検出区間が終了したことを示す時間設定信号を入力すると、この時間設定信号の入力をトリガとして駆動手段60に対して半導体スイッチング素子10の制御端子11に印加する駆動電流を増加するための電流制御信号を出力する。これにより、サージの発生が予想されるミラー区間後に行われる短絡状態の検出が終了した後は制御端子11に印加される駆動電流iが増加するため、サージの発生を抑制しつつ、スイッチング速度が向上する。また、時間設定信号を利用して制御端子11に流す駆動電流iの電流量を制御しているため、制御端子11の電圧を検出するための構成が不要となり、回路規模が小さくなる。

(もっと読む)

141 - 160 / 1,722

[ Back to top ]