Fターム[5J055BX17]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | ゲート回路(サンプルホールド等) (439)

Fターム[5J055BX17]に分類される特許

101 - 120 / 439

サンプリング回路

【課題】入力されるデジタル信号のパルス幅を拡張させた後、サンプリング動作が行われるようにすることができる半導体装置のサンプリング回路を提供すること。

【解決手段】本発明のサンプリング回路は、データ信号を受信し、クロック信号を基準としてサンプリングする第1のサンプリング部と、前記データ信号を所定時間の分だけ遅延させた信号を受信し、前記クロック信号を基準としてサンプリングする第2のサンプリング部と、前記第1のサンプリング部および第2のサンプリング部の出力信号を結合してサンプリングデータ信号を出力する出力部とを備える。

(もっと読む)

半導体集積回路装置

【課題】アンテナスイッチのスイッチング用トランジスタにSOI MOSFETを用いながら、高調波歪を大幅に低減する。

【解決手段】アンテナスイッチの受信分路スルーMOSFETグループ13を構成するトランジスタ44〜48のドレイン−ゲート間の片方に静電容量素子54〜58を付加することにより、ソース−ゲート間とドレイン−ゲート間の電圧振幅が同じでなくなる。その結果、ソース−ドレイン間寄生容量の電圧依存は、電圧の極性に対して非対称となる。この非対称性は、同様の非対称性を有する信号歪を発生させるので、それを基板容量の電圧依存による2次高調波と同等の振幅と逆の位相を持つように設定することにより、2次高調波歪を打ち消すことができ、2次高調波歪を低減することができる。

(もっと読む)

ホールド回路

【課題】ホールド動作時の出力電圧の変動を抑制することができるホールド回路を提供する。

【解決方法】ホールド回路100は、ホールドコンデンサ140、オペアンプ110、第1pMOS130、バッファアンプ150、電圧調整回路120を備える。オペアンプ110の非反転入力端には入力信号の電圧が印加され、反転入力端にはホールドコンデンサ140の電圧が印加される。ゲートGとドレインDが接続している第1pMOS130は、ソースSからドレインDへ電流を通す整流素子として機能する。整流素子の入力端はオペアンプ出力端に接続しており、出力端はホールドコンデンサ他端に接続している。電圧調整回路120は、オペアンプ出力端と整流素子入力端の間に接続されており、オペアンプ出力端の電圧がバッファアンプ出力端の電圧よりも低い場合に、整流素子入力端の電圧をオペアンプ出力端の電圧よりも高くする。

(もっと読む)

半導体リレーモジュール

【課題】高周波特性を向上させるとともに、発光素子と制御素子を封止する透光性樹脂の形状を所望の形状に保持しやすい半導体リレーモジュールを提供する。

【解決手段】半導体リレーモジュールAは、ソース電極同士が接続されたMOSFET11,12からなり、高周波信号用の信号伝送線路110の途中に設けられた半導体スイッチ1と、入力信号に応じて光信号を発光する発光ダイオード31と、発光ダイオード31からの光信号を受光する受光素子を有し当該受光素子の出力に応じてMOSFET11,12のオン/オフを制御する制御IC32と、制御IC32が備える受光素子および発光ダイオード31を光学的に結合させた状態で樹脂封止する透光性樹脂8を備える。制御IC32は、信号伝送線路110を構成する導体パターン113から分岐させたランド132上に配置され、導体パターン113とランド132との間にはLPF4が挿入される。

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電圧が昇圧規定電圧に達し、その後は小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路100は、制御部10と発振回路20と昇圧部30とを有する。発振回路20は、予め定められた周期のパルス信号を出力する。昇圧部30は、電圧を昇圧するn(n≧1)個の昇圧回路を備え、発振回路20から出力されるパルス信号に応じて電荷量を出力する。制御部10は、昇圧部30から出力される電圧と、予め定められた規定電圧とを比較し、昇圧部30から出力される電圧が規定電圧より大きくなると、昇圧部30からのパルス信号一周期あたりの供給電荷量を減少させる。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】電源電圧を変更することなく、広い温度範囲でリーク電流を抑えて動作する半導体装置を提供する。

【解決手段】しきい値電圧が第1電圧である第1トランジスタを含む高VT部7と、しきい値電圧が第1電圧よりも低い第2電圧である第2トランジスタを含む低VT部8と、温度を測定し、温度が所定の温度より高い高温状態であるか、温度が所定の温度よりも低い低温状態であるかを判定し、高温状態を示す信号又は低温状態を示す信号を出力する温度検知部6と、高温状態を示す信号、又は低温状態を示す信号を受信し、高温状態を示す信号に基づいて高VT部7を動作させ、低温状態を示す信号に基づいて低VT部8を動作させる制御を行う制御部9とを具備する。

(もっと読む)

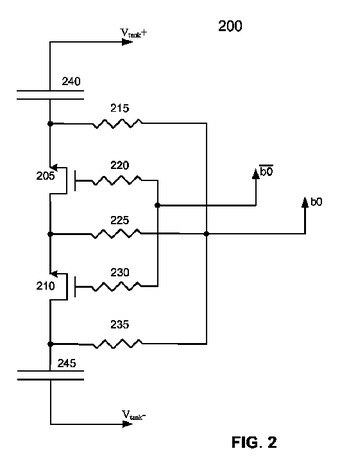

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

入力信号の移動平均を出力する平均化回路

【課題】アナログ入力信号をデジタル化することなく、そのアナログ信号形態のままで移動平均による平均化処理を行わせ、これにより、回路の簡単や消費費電力の低減化をはかりつつ、後段でのアナログ信号処理を行いやすくする。

【解決手段】積分回路を形成する演算増幅器12と、一方の電極端子に入力信号Vinが印加されるとともに、他方の電極端子がスイッチング回路ph1またはph2を介して基準電位または上記演算増幅器の積分入力に接続される第1の入力容量素子C1と、一方の電極端子がスイッチング回路ph3またはph4を介して上記演算増幅器の積分出力または上記演算増幅器の積分入力に接続されるとともに、他方の電極端子が基準電位に接続される第2の入力容量素子C2を有し、スイッチング回路ph1,ph3とph2,ph4は、入力信号Vinの周波数域よりも十分に高い周波数でオン/オフさせられるとともに、一方のオフ区間内に他方がオンされ、かつ他方のオフ区間内に一方がオンされる。

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

電流スイッチ回路及びそれを用いたD/Aコンバータ、半導体集積回路及び通信機器

【課題】電流加算型D/Aコンバータに用いられる電流スイッチ回路において、低電源電圧時にしきい値電圧の低いトランジスタを用いた際に課題となるダイナミックレンジの低下を改善し、出力電圧範囲を大きく取る。

【解決手段】電流スイッチ回路1は、差動スイッチ12を構成する第1及び第2のトランジスタTr121、Tr122を有する。しきい値電圧制御回路5は、その出力端子Vboutから前記差動スイッチ12を構成する2個のトランジスタTr121、Tr122のサブストレート端子に出力するサブストレート電圧を制御して、前記差動スイッチの2個のトランジスタのしきい値電圧を制御する。従って、電流スイッチ回路1の電源電圧を低減させても、特性劣化を生じることなく、差動スイッチ12内の2個のトランジスタのしきい値に依存する電流スイッチ回路1の出力電圧範囲を大きく取ることができる。

(もっと読む)

高周波電源装置

【課題】安定したパルス高周波電力を供給することができる高周波電源装置1を提供する。

【解決手段】高周波電源装置1は、パルス高周波電力の出力電圧を検出して包絡線検波を行い、その検波信号をサンプルホールド部6によりサンプリングし、サンプリング電圧Vsを高周波電力生成部3にフィードバックしてパルス高周波電力Poutの制御を行う。サンプルホールド部6は、サンプルホールド信号のオン期間中、検波信号Paをサンプリング電圧Vsとして出力し、サンプルホールド信号のオフ期間中、サンプルホールド信号がオンからオフへ切り替るタイミングの検波信号Paの電圧レベルをホールドして、サンプリング電圧Vsとして出力する。

(もっと読む)

CV変換回路

【課題】超小型に形成されて容量値および容量変化が非常に微小なセンサ容量素子の容量変化を、高効率かつ高精度に電圧変化に変換させて検出する。

【解決手段】センサ容量素子Csの静電容量を、スイッチドキャパシタ型負帰還回路を有する演算増幅器11によって電圧変換するCV変換回路であって、その負帰還回路は、演算増幅器11の出力端子と反転入力端子間に直列に接続された第1,第2の容量素子C1,C2と、その容量素子C1,C2の中間接続点bに一方の電極端子が接続された第3の容量素子C3と、この容量素子C3の他方の電極端子を演算増幅器11の出力端子または基準電位に接続する切り換えスイッチ回路Sw1,Sw2を有し、このスイッチ回路の接続位置によって等価的な帰還容量値を可変設定する。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

ドループ補正ピークホールド回路

【課題】ピークホールド回路において、ドループを抑制してピーク電圧を長時間保持できるドループ補正ピークホールド回路を提供すること。

【解決手段】ピークホールド回路のホールドコンデンサC1は、一端をダイオードD1のカソードに接続し、他端をドループ補正回路20に接続してある。ドループ補正回路20は、ホールドコンデンサC2の保持電圧を、増幅回路A3において極性を反転してホールドコンデンサC1に印加する。即ちドループ補正回路20は、ホールドコンデンサC1にその保持電圧と逆極性のドループ補正電圧を印加する。ドループ補正電圧の印加によりホールドコンデンサC1のドループを長時間抑制できる。

(もっと読む)

半導体集積回路

【課題】昇圧回路がオフの際にバイパスされる電源電圧の電圧降下を抑圧可能とする。

【解決手段】動作制御スイッチ1がオフとされるに伴い昇圧回路101が動作停止状態となると、エンハンスメント型FET4はオフとなるが、デプレッション型FET3のゲートには、抵抗器5を介して昇圧用電源入力端子11に印加された電源電圧が供給されるため、デプレッション型FET3はオン状態となり、ダイオード等と比較して電圧降下が極小さなデプレッション型FET3を介して昇圧用電源入力端子11に印加された電源電圧にほぼ等しい電圧が出力端子13に得られるものとなっている。

(もっと読む)

特に自動車で使用するための制御回路を作動する方法

第1および第2出力部と、第1および第2切換手段とを備える制御回路の作動方法に関し、負荷を作動するために出力部の間に印加される制御電圧を次にように形成する。切換手段によって第1出力部を第1または第2電位に選択的に接続し、切換手段によって第2出力部を第1または第2電位に選択的に接続することによって形成し、制御電圧が少なくとも短時間少なくともほぼゼロとなる状態を、第1の場合には2つの出力部を2つの切換手段によって同時に前記第1電位に接続することによって誘起し、第2の場合には2つの出力部を2つの切換手段によって同時に第2電位に接続することによって誘起し、制御回路の作動時に、2つの場合を少なくとも1回誘起し、いずれの場合にも、出力部に印加された制御電圧を特徴づける変数または出力部/スイッチに対して直列に配置した少なくとも1つのシャント抵抗器を介して流れる電流を特徴づける変数を検出し、比較を行う。 (もっと読む)

高周波スイッチ及び受信回路

【課題】簡単な構成でセルフミキシング信号の発生を低減する高周波スイッチ及びこれを用いた受信回路を提供する。

【解決手段】ゲート端子が入力端子側に接続され、ドレイン端子が出力端子側に接続され、ソースが接地された電界効果トランジスタと、前記電界効果トランジスタのゲート端子側に接続されるゲートバイアス電圧調整手段とドレイン端子側に接続されるドレインバイアス電圧調整手段の少なくともいずれか一方を備え、前記ゲート端子と入力端子との間及び前記ドレイン端子と出力端子との間の少なくともいずれか一方に整合回路を備え、導通状態における反射特性と前記遮断状態における反射特性とが略等しくなるように、スイッチを構成している。

(もっと読む)

レベルシフト回路及びこれを備えたスイッチ回路

【課題】レベルシフト回路の消費電力削減を図る。

【解決手段】本発明に係るレベルシフト回路は、入力信号のレベルを、第1の電圧と前記第1の電圧より高い第2の電圧との間のレベルに変換するレベルシフト回路であって、入力信号(Vin)に基づいて、その周波数及び振幅のうち少なくとも一方が変化する発振信号を生成するセレクト回路13と、セレクト回路13から出力された発振信号(Vn1)の直流成分を除去して交流成分を出力するフィルタ回路16と、第1の電圧とフィルタ回路16の出力側電圧との間で動作し、発振信号(Vin)の交流成分における周波数及び振幅のうち少なくとも一方の変化に応じて、信号電圧が変化する制御信号(Vn2)を生成するディテクト回路14と、制御信号に基づいて第1の電圧と第2の電圧の間のレベルを有する出力信号を生成する出力回路15と、を有する。

(もっと読む)

スイッチ回路

【課題】シリーズFETおよびシャントFETとして4端子NMOSFETを用いるSPSTスイッチ回路では、シリーズFETがオン状態で、シャントFETがオフ状態のときに、SPSTスイッチ回路はオン状態になる。FETのバックゲートには寄生ダイオードが存在し、入力交流信号電圧が所定の閾値を超えると、寄生ダイオードがオン状態になる。その結果、SPSTスイッチ回路はスイッチ・デバイスとしての線形動作を維持できなくなり、挿入損失特性やゆがみ特性が悪化する場合がある。

【解決手段】FETのバックゲートに、バイアス電圧を印加するためのバイアス電源を設ける。このバイアス電源として、DC−DC変換回路を用いることで、SPSTスイッチ回路をシリコン半導体チップ化することが容易になる。

(もっと読む)

線形サンプリングスイッチ

【課題】 線形サンプリングスイッチ

【手段】 サンプリング回路はpチャネル及びnチャネル電界効果トランジスタ(FET)で構成される。pチャネルFET(42)のソースノードはnチャネルFET(40)のドレインノードに結合され、pチャネルFET(42)のドレインノードはnチャネルFET(40)のソースノードに結合される。サンプリングクロックは各FETのゲートノードに結合される。線形サンプリング回路の第1の側はアナログまたはRF信号源に接続され、そして線形サンプリング回路の向う側は保持キャパシタ(44)に接続される。nチャネルFETはnチャネル幅を有する。pチャネルFETはpチャネル幅を有する。結果としてスイッチのオン抵抗の線形性を増加させるために、pチャネル幅はnチャネル幅よりも大きい。

(もっと読む)

101 - 120 / 439

[ Back to top ]