Fターム[5J055BX17]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | ゲート回路(サンプルホールド等) (439)

Fターム[5J055BX17]に分類される特許

141 - 160 / 439

高周波回路のスイッチング方法及び高周波回路

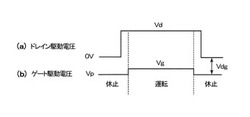

【課題】休止時のゲート−ドレイン間の電圧が小さくなるようにし、また運転/休止の切替え時に低ドレイン電圧領域を通過させないようにする。

【解決手段】高周波回路に含まれる能動素子に対し駆動電圧を与えることにより、この能動素子の運転と休止を切り替える高周波回路及びそのスイッチング方法で、休止状態の能動素子のドレインに、定常運転レベルの電圧Vdを印加し、その後、能動素子のゲートに、定常運転レベルの電圧Vgを印加することにより運転に切り替え、一方、運転状態の能動素子のゲートに、定常運転レベルの電圧Vgに換えてピンチオフ電圧Vpを印加し、その後、能動素子のドレインに印加されている定常運転レベルの電圧Vdを切断することにより、休止に切り替える。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

半導体集積回路及びLSIシステム

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

サブサンプリングミキサ回路及び電子機器

【課題】サンプリング波形のS/Nを改善する。

【解決手段】第1の入力端子250と第1の出力端子260と第1の制御信号Fs1で切り替わる第1のアナログスイッチ210と第1の蓄電器230とを含む第1の回路200と、第1の入力端子250と第2の出力端子360と第2の制御信号Fs2で切り替わる第2のアナログスイッチ310と第2の蓄電器330とを含む第2の回路300と、第1の出力端子260と接続された第3の入力端子410と第2の出力端子360と接続された第4の入力端子420と第3の出力端子430とを含み、第3の制御信号SWにより切り替わるスイッチ回路400と、第1の制御信号Fs1と第2の制御信号Fs2と第3の制御信号SWとを出力する制御回路100と、を含むサブサンプリングミキサ回路1。

(もっと読む)

高周波半導体スイッチ装置

【課題】チャージポンプの出力容量を低減してチップ面積を縮小できる高周波半導体スイッチ装置を提供する。

【解決手段】アンテナ端子ANTと、各高周波端子TX、RXとの間の接続を切り換える回路であって、アンテナ端子ANTと各高周波端子TX、RXとの間にそれぞれ接続されたスルーFETT1、T2を有する高周波スイッチ回路1と、各スルーFETT1、T2のゲートを駆動する駆動回路11、12と、駆動回路11、12の高電位電源端子に正側出力端子CP_out1が接続され、駆動回路11、12の低電位電源端子に負側出力端子CP_out2が接続された正負両極性チャージポンプ回路15と、を備え、各スルーFETT1、T2のゲート容量はそれぞれ概略等しく、正負両極性チャージポンプ回路15の正側出力端子CP_out1と負側出力端子CP_out2との間に容量Cxが設けられている。

(もっと読む)

高周波回路、高周波電力増幅装置、及び半導体装置

【課題】マルチバンド又はマルチモードに適した高周波回路、高周波電力増幅装置、及び半導体装置を提供する。

【解決手段】本発明に係る高周波回路は、高周波信号を増幅する高周波回路であって、高周波信号を増幅して増幅信号を出力する増幅回路と、増幅回路の出力と接続された負荷回路と、複数の伝送線路と、増幅信号の所定パラメータに応じて、複数の伝送線路の中から負荷回路の出力と接続する伝送線路を選択する選択回路と、選択回路で選択された伝送線路毎に、増幅回路から増幅回路の出力側をみたときの負荷インピーダンスを所定の負荷インピーダンスに変換する変換回路と、を備える。

(もっと読む)

サンプリング回路

【課題】サンプリング回路の省電力化を図ること。

【解決手段】アンダーサンプリング方式のサンプリングミキサ回路30において、サンプリングパルス信号である制御信号S1,S2に従って、非サンプリング期間の間、増幅部321の入力端子と接続端子との間が接続されることで増幅部321の増幅動作のON/OFFが制御される。増幅部321の前段の整合回路31は、増幅部321の入力端子と出力端子との間が接続されていないとき、すなわち増幅動作が行われているサンプリング期間では入力インピーダンスを整合させ、増幅部321の入力端子と出力端子との間が接続されているとき、すなわち増幅動作が行われない非サンプリング期間では入力インピーダンスを不整合させる回路素子が選択されている。また、動作制御部323は、制御信号S3,S4に従って、非サンプリング期間の間、増幅部321のトランジスタTr1,Tr2の増幅動作を停止させる。

(もっと読む)

PLL回路

【課題】ノイズの抑圧を効果的に行うことができるPLL回路を提供する。

【解決手段】位相比較器10と、チャージポンプ回路20と、ループフィルタ30と、VCO40と、N分周器50とを備える。チャージポンプ回路20の一実施形態は、アップ信号UP1によりスイッチ22をオンした後、アップ信号UP1を遅延させたアップ信号UP2により再度スイッチ22をオンする。同様に、ダウン信号DN1によりスイッチ23をオンした後、ダウン信号DN1を遅延させたダウン信号DN2により再度スイッチ23をオンする。

(もっと読む)

サンプルホールド集積回路、サンプルホールド回路において漏れを補償する方法、および集積回路で用いられるサンプリング回路

【課題】サンプリングされた値を長時間キャパシタに保持し、かつ蓄積された値に対するスイッチ漏れ電流の影響を実質的に減少させるための方法および装置を提供する。

【解決手段】サンプルホールド回路は、一局面において、第1および第2のスイッチを含む。第1のスイッチは、入力信号を受けて、第1のキャパシタを用いて入力信号をサンプリングするために結合されることができる。第1の漏れ電流は、第1のスイッチの第1および第2の導電性端子の間を流れ、第1の漏れ電荷として第1のキャパシタに蓄えられる。第2の漏れ電流は、第2のスイッチの第1および第2の導電性端子の間を流れ、第2の漏れ電荷として第2のキャパシタに蓄えられる。オフセット回路は、保持されサンプリングされた信号に応答して発生する信号および第1のスイッチを介して蓄えられた電荷からある量を減算することによって、補償されサンプリングされた値を生成し、ある量は、第2のキャパシタの蓄えられた漏れ電荷に応答して発生する。

(もっと読む)

寄生容量性負荷を低減したクロスバー・デバイスおよび再構成可能回路におけるクロスバー・デバイスの使用

【課題】好適なクロスバー・デバイスを提供する。

【解決手段】クロスバー・デバイスは、第1のセットの入力線と第2のセットの出力線とを含む。複数のパス・トランジスタ・チェーンを設け、寄生容量性負荷を減少させた形で入力線を出力線に選択的に結合させる。メモリ素子とデコーダ論理を設けて、選択的結合の制御を容易にする。クロスバー・デバイスの各メモリ素子にVthだけ高い供給電圧が供給されるようにして、対応する出力バッファの入力電圧をVddに維持することにより、複数のクロスバー・デバイスの再構成可能回路ブロックへの低電力応用を改善させることができる。相互に接続したクロスバー・デバイスの全ての出力バッファに制御線を介して制御回路を結合し、これらのクロスバー・デバイスの出力バッファを既知のパワーオン状態にすることにより、複数のクロスバー・デバイスの再構成可能回路ブロックへの適用を改善する。

(もっと読む)

DC−DCコンバータ

【課題】出力短絡保護機能を設ける場合に、短絡電流をバイパスするバイパス回路を外部に設けることなく、内部回路(内部素子)を保護できるDC−DCコンバータの提供。

【解決手段】この発明は、直流電圧を昇圧して出力電圧を生成し、当該出力電圧の生成のために入力端子1と出力端子2との間に複数のMOSトランジスタM1〜M4が直列接続されたDC−DCコンバータである。MOSトランジスタM4は、自己の基板電位制御用のMOSトランジスタM41、M42を有する。DC−DCコンバータの定常動作時にはMOSトランジスタM42がオンし、MOSトランジスタM4の基板端子に出力端子2の電位が印加される。一方、DC−DCコンバータの出力短絡時にはMOSトランジスタM41がオンし、MOSトランジスタM4の基板端子に出力端子2とは反対側の電位が印加される。

(もっと読む)

電流発生回路及び表示装置

【課題】複数の単位電流を生成するための複数の電流トランジスタ備えて表示データの階調に応じた階調電流を生成する電流発生回路において、回路規模を小さくすること。

【解決手段】例えば8ビット(bit)データの場合、バイアス発生回路10の各出力端子から8つのそれぞれ電位レベルの異なる各バイアス電位VN1〜VN8を出力し、このバイアス発生回路10の各出力端子にチャネル幅(W)及びチャネル長(L)が同一に設定された8個の定電流トランジスタQ10〜Q17のゲート電極を接続して各定電流トランジスタQ10〜Q17にデータの各ビットに対応した単位電流を流し、これら電流トランジスタQ10〜Q17を選択的に動作させて、各単位電流を選択して生成した階調電流をディスプレイ5に供給する。

(もっと読む)

サンプルホールド回路

【課題】キャパシタを用いたサンプルホールド回路において、サンプリング時におけるキャパシタの充電状態をホールド状態とするためにオフされるべきスイッチにリーク電流が生じる。

【解決手段】サンプルホールド回路10は、オペアンプ12の反転入力端子IN−に一方端を接続されたキャパシタC1にサンプリング電圧に応じた電荷を蓄積する。その際、C1のIN−側の端子はスイッチ回路14を介して出力端子VOUTに接続し、所定電位に設定する。ホールド状態ではスイッチ回路14はオフされ、それが接続されたC1の端子をフローティング状態とする。スイッチ回路14は、IN−とVOUTとの間に直列に接続され同相でオン・オフされるMOSトランジスタスイッチS11,S12と、それら相互の接続点と接地電位との間に接続されたキャパシタC2とからなる。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】演算増幅器の電源ラインの電位を安定化させる。

【解決手段】サンプルホールド回路は、演算増幅器OP1と、演算増幅器の出力端子と第1の入力端子のノードであるサミングノードNEGとの間に設けられた帰還用スイッチ素子SFと、帰還用スイッチ素子のオン・オフを制御するスイッチ信号生成回路80を含む。スイッチ信号生成回路を構成するN型トランジスタは第1のP型ウェルPW1に、スイッチ信号生成回路を構成するP型トランジスタは第1のN型ウェルNW1に、第1のP型ウェル及び第1のN型ウェルは第1のディープN型ウェルDNW1にそれぞれ形成される。演算増幅器のN型トランジスタは第2のP型ウェルPW2に、演算増幅器のP型トランジスタは第2のN型ウェルNW2に、第2のP型ウェル及び第2のN型ウェルは、第1のディープN型ウェルと分離された第2のディープN型ウェルDNW2にそれぞれ形成される。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】回路の大規模化を抑えながら適正な位相補償を実現する。

【解決手段】演算増幅器OP1と、サンプルホールド回路の入力ノードNIと、接続ノードNSとの間に設けられたサンプリング用スイッチ素子SSと、接続ノードと、演算増幅器の第1の入力端子のノードであるサミングノードNEGとの間に設けられたサンプリング用キャパシタCSと、演算増幅器の出力端子とサミングノードとの間に設けられた帰還用スイッチ素子SFと、接続ノードと、演算増幅器の出力端子との間に設けられたフリップアラウンド用スイッチ素子SAと、サンプリング用キャパシタのサミングノード側の端子NCと演算増幅器の出力端子との間に設けられた位相補償用抵抗素子RPと、を含む。

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電位が昇圧規定電位に達し、小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路1は、制御部10と発振回路20と昇圧部30とを具備する。発振回路20は、予め定められた一定周期のパルス信号を出力する。昇圧部30は、電位を昇圧するn(n≧1)個の昇圧回路を備え、発振回路20から出力されるパルス信号に応じて第1の電荷量を出力する。制御部10は、昇圧部30から出力される電位と、予め定められた規定電位とを比較し、昇圧部30から出力される電位が一旦規定電位より大きくなると、昇圧部30に第1の電荷量より少ない電荷量を出力させる。

(もっと読む)

アナログスイッチ回路、マルチプレクサ回路および集積回路

【課題】マルチプレクサ回路に使用する場合には、入力リーク電流を削減することができるアナログスイッチ回路を提供する。

【解決手段】第1のCMOSスイッチ(PMOSトランジスタPMS11、NMOSトランジスタNMS11)と第2のCMOSスイッチ(PMOSトランジスタPMS12、NMOSトランジスタNMS12)とを直列接続したアナログスイッチに対して中間ノード電位設定回路FNDV1を設ける。中間ノード電位設定回路FNDV1は、第1、第2のCMOSスイッチを非導通とするとき、第1、第2のCMOSスイッチ間の中間ノードNDSW1の電位を複数電位(GND、Vdd、Vdd/2)から選択された電位に設定する。

(もっと読む)

高周波信号用スイッチ回路

【課題】SOI基板上に形成され、オン/オフ特性が高く、高周波信号の歪が少ない高周波信号用スイッチ回路を提供する。

【解決手段】SOI基板上に形成された高周波信号用スイッチ回路1において、高周波入出力端子ANTを高周波端子TXに接続するか高周波端子RXに接続するかを切替えるスイッチ部11と、負電位Vssを生成する負電位発生回路と、スイッチ部11を制御する制御部13とを設ける。制御部13には、正電位Vddと負電位Vssが供給され、スルートランジスタT1のゲート及びシャントトランジスタT3のゲートの一方に正電位Vddを出力し他方に負電位Vssを出力する差動回路16と、スルートランジスタT1及びシャントトランジスタT3のバックゲートに対して、接地電位GND又は負電位Vssを出力するCMOSインバータINV13及びINV14を設ける。

(もっと読む)

サンプル・ホールド回路及びデジタルアナログ変換回路

【課題】電荷分配を行う容量の容量値が小さくても、アンプの入力容量による出力誤差が小さい、高精度出力のサンプル・ホールド回路、シリアルDACの提供。

【解決手段】第1のスイッチ110を介して接続された第1及び第2の容量素子C11,C12と、差動回路と、を備え、前記差動回路は、差動入力対の第1入力が、前記第1の容量素子の一端N11に第2のスイッチ121を介して接続され、第2入力が、前記第2の容量素子の一端N8に接続された差動入力段と、前記差動入力段の出力を入力に受け、出力がサンプル・ホールド回路の出力端子N9に接続されるとともに、第3のスイッチ122を介して、前記差動入力段の前記第1入力に接続される増幅段16と、を備えている。

(もっと読む)

サンプルホールド回路

【課題】アナログ電圧を、アナログスイッチ20を介してコンデンサ11に接続/切り離し、アナログ電圧をコンデンサ11に保持する構成のサンプルホールド回路では、アナログスイッチを構成するMOSFETのゲートの容量成分によってオンオフを制御する制御信号が変化したときに発生する漏れ電流のためにコンデンサに蓄積された電荷が変化し、正確な電圧を保持することができなかったという課題を解決する。

【解決手段】アナログスイッチ20と逆方向に動作するアナログスイッチ30をアナログスイッチ20に並列に接続するようにした。2つのアナログスイッチの漏れ電流の方向が逆なるので、漏れ電流がキャンセルされ、正確な電圧を保持することができる。

(もっと読む)

141 - 160 / 439

[ Back to top ]