Fターム[5J055BX17]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | ゲート回路(サンプルホールド等) (439)

Fターム[5J055BX17]に分類される特許

21 - 40 / 439

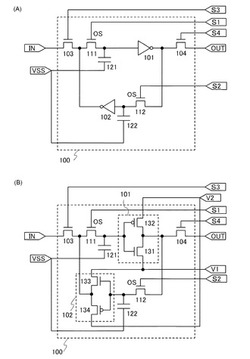

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

双方向スイッチおよびそれを利用した充放電保護装置

【課題】少ないトランジスタ数で双方向スイッチを構成する。

【解決手段】双方向スイッチ装置は,HEMTを有する双方向スイッチと,第1の条件時にHEMTのソースまたはドレインの一方の端子とゲートとの間に閾値電圧未満の第1の電圧を印加してソースまたはドレインの他方の端子から一方の端子への第1の電流パスをオフにし,第2の条件時に他方の端子とゲートとの間に閾値電圧未満の第2の電圧を印加して一方の端子から他方の端子への第2の電流パスをオフにし,第3の条件時にHEMTのソース及びドレインとゲートとの間に閾値電圧より高い第3の電圧を印加して第1,第2の電流パスをオンにする制御回路とを有する。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

過電圧保護回路

【課題】電圧伝達経路における電圧降下が小さい過電圧保護回路を提供する。

【解決手段】入力電圧と第1の電圧とを入力して、昇圧した第2の電圧を、電圧伝達経路110の遮断または導通を制御するスイッチ回路SWのMOSトランジスタPSWのゲートに供給する昇圧回路CPと、MOSトランジスタPSWのゲートに蓄積された電荷を放電する放電回路DCGとを備える。

(もっと読む)

電圧変換回路及び不揮発性半導体記憶装置

【課題】チャージポンプ回路を駆動するクロックバッファ回路に流れる瞬時電流を抑制すること。

【解決手段】

第1のトランジスタ(T11)のドレインを第1のキャパシタ(C11)によって第1の制御信号(DCLK10)に応じて昇圧駆動する第1のバッファと、第1のトランジスタ(T11)のゲートを第2のキャパシタ(C12)によって第2の制御信号(GCLK10)に応じて昇圧駆動する第2のバッファとから構成される電圧変換回路おいて、

第1のバッファは,第1の制御信号(DCLK10)の遷移時の駆動能力が,第2の制御信号(GCLK10)の遷移時の駆動能力よりも低いことを特徴とする電圧変換回路。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

無線通信装置及び高周波スイッチ回路

【課題】回路規模が小さく、かつ消費電力の小さい無線通信装置及び高周波スイッチ回路を提供する。

【解決手段】無線通信装置100は、共用アンテナ101と、整合回路110、120と、高周波スイッチ回路130と、充電電力受電回路140と、応答器150と、から構成される。高周波スイッチ回路130は、電界効果トランジスタ131、132と、検波回路と、を備える。電界効果トランジスタ131、132のソース端子は共通接続される。検波回路は共通接続点に接続され、電界効果トランジスタ131のドレイン端子から出力された高周波信号を検波し、共通接続点の電位を基準とした検波電圧を電界効果トランジスタ131、132のゲート端子に印加する。電界効果トランジスタ131、132のドレイン端子間のインピーダンスは検波電圧に従って変化する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

アナログスイッチ回路

【課題】高位電源の電位より高い又は低位電源の電位より低い伝送信号を、MOSトランジスタを用いたアナログスイッチにより好適に阻止可能なアナログスイッチ回路を提供する。

【解決手段】第1のアナログスイッチ11と、第1のアナログスイッチ11の制御端子11cに至る制御信号経路21上に設けられた第2のアナログスイッチ12と、伝送信号の電位が所定の高電位レベルより高い場合又は伝送信号の電位が所定の低電位レベルより低い場合に第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡するよう構成された第3のアナログスイッチ13と、を備え、第2のアナログスイッチ12は、少なくとも第3のアナログスイッチ13が第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡する場合に、所定のレベルの電位が印加されてオフするようMOSトランジスタを用いて構成される。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

リーク補償された電子スイッチ

【課題】電子スイッチの開放されたスイッチを通したリーク電流は、信号クロストークを引き起こす。

【解決手段】スイッチング用の電子回路は少なくとも4個の電子スイッチ200のセット100を備える。第1サブセット110の少なくとも2個の電子スイッチ210,230は直列接続され、第2サブセット120の少なくとも2個の電子スイッチ220,240は直列接続される。前記第1サブセット110の第1電子スイッチ210に接続される第1バッファ310、及び前記第2サブセット120の第2電子スイッチ220に接続される第2バッファ320を備え、前記第1バッファ310は開状態における前記第1電子スイッチ210を通した電圧降下を最小化し、前記第2バッファ320は開状態における前記第2電子スイッチ220を通した電圧降下を最小化する。また2個のサブセット110,120の間に配され、グランドに接続されたスイッチ410を備える。

(もっと読む)

スイッチング回路および試験方法

【課題】半導体スイッチングデバイスが完全な機能を維持していることを保証するために、サービス中にそれらを試験する方法を提供する。

【解決手段】負荷および電圧源2に接続するためのスイッチング回路1であって、負荷への電力をスイッチオンおよびスイッチオフするための1つまたは複数のスイッチングデバイス6、7、...、nと、負荷を短絡し、それにより負荷を電圧源から隔離するためのプルダウンデバイス4と、一度に複数のスイッチングデバイスのうちの少なくとも1つを起動するために、電圧源が負荷から隔離されている間に動作させることができるコントローラ3とを備え、起動された前記スイッチングデバイスまたは個々のスイッチングデバイスを通って電流が流れ、この電流を測定して、起動された前記スイッチングデバイスまたは個々のスイッチングデバイスが適切に動作しているかどうかを試験することができるスイッチング回路1が開示される。

(もっと読む)

サンプルホールド回路

【課題】S/N比を向上させたサンプルホールド回路を提供すること。

【解決手段】入力電圧を入力する入力端子と、入力電圧に基づいたサンプリング電圧をホールドする複数の容量と、入力端子と記複数の容量との間に夫々接続された複数の入力スイッチと、複数の容量のホールド電圧を出力する出力端子と、を備え、複数の容量は、複数の入力スイッチによって異なるタイミングで入力電圧をサンプリングし、複数の容量のホールド電圧の平均化処理を行って出力端子に出力する、構成とした。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、高パワーの高周波信号に対する耐圧を維持しながら小型化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、絶縁膜の上の半導体層に設けられたFETを含むスイッチ回路を有する半導体装置であって、前記FETのソース領域とドレイン領域との間に、前記ソース領域から前記ドレイン領域に向かう方向に並んで設けられた第1のゲート電極および第2のゲート電極と、前記第1のゲート電極と前記第2のゲート電極との間の中間領域に電気的に接続された制御端子と、を備える。前記FETは、前記第1のゲート電極および前記第2のゲート電極に供給されるゲート電圧によりON/OFF制御され、前記FETがON状態にある時、前記制御端子をアース電位とし、前記FETがOFF状態にある時、前記制御端子を正電位または負電位とする。

(もっと読む)

高周波スイッチ

【課題】高周波信号の伝達経路における高調波特性を良好に維持しつつ、回路規模が縮小された高周波スイッチを提供する。

【解決手段】1つの送信ポート10と、1つの受信ポート20と、共通ポート30と、送信側シリーズスイッチ40と、送信側シャントスイッチ50と、受信側シリーズスイッチ60と、受信側シャントスイッチ70とを有する。送信ポートは、送信信号を入力し、受信ポートは、受信信号を出力し、共通ポートは、送信信号を送信するか、または受信信号を受信する。送信側シリーズスイッチは、送信ポートと共通ポートとの間に接続され、送信側シャントスイッチは、送信ポートとグランドとの間に接続され、受信側シリーズスイッチは、受信ポートと共通ポートとの間に接続され、夫々のスイッチはボディコンタクト型FETである。受信側シャントスイッチは、受信ポートとグランドとの間に接続され、フローティングボディ型FETである。

(もっと読む)

21 - 40 / 439

[ Back to top ]