Fターム[5J055BX24]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 時限スイッチ、タイマ (69) | 時定数型タイマ、CR時定数タイマ (25)

Fターム[5J055BX24]の下位に属するFターム

パルス制御型タイマ (7)

Fターム[5J055BX24]に分類される特許

1 - 18 / 18

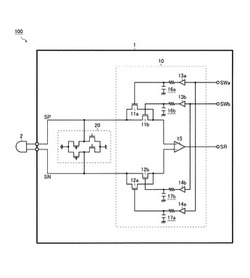

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

周波数監視回路

【課題】より適切に安定した周波数監視を行うことが可能な周波数監視回路を提供する。

【解決手段】ウォッチドッグタイマ回路16は、キャパシタCの充放電を行う充放電部161と、充電電圧VCを基準電圧Va〜Vcと比較して比較信号Sa〜Scを生成する比較部162と、クロック信号CLKの周波数監視結果に応じたリセット信号S2を出力するリセット出力部163と、クロック信号CLKと比較信号Sa〜Scに基づいて充放電部161とリセット出力部163を制御する制御部164と、を有し、比較部162は、基準電圧Va〜Vcとして、上限電圧Vaと下限電圧Vbのほかに、中間電圧Vcを備えており、制御部162は、充電電圧VCと上限電圧Va及び下限電圧Vbとの比較結果のほか、クロック信号CLKのパルスエッジ到来時における充電電圧VCと中間電圧Vcとの比較結果に基づいて、リセット信号S2の論理レベルを決定する。

(もっと読む)

タイマー回路

【課題】容量素子を利用したタイマー回路において、容量素子が短絡状態になったことを検出することができるタイマー回路を提供する。

【解決手段】容量素子の充電又は放電が開始されてから、容量素子Cの電位と、グランドGDNの電位より高く電源VDDの電位より低い基準電圧VREF_Hの電位とを比較して、容量素子Cの電位が基準電圧VREF_Hの電位に到達した場合に、予め定められたタイムアップ信号を出力するコンパレータCMP1と、容量素子Cの電位が、グランドGNDの電位より高く基準電圧VREF_Hの電位より低い基準電圧VREF_Sの電位より高くなるように制御する制御部と、容量素子Cの電位と基準電圧VREF_Sの電位とを比較して、容量素子Cの電位が基準電圧VREF_Sの電位より低くなった場合に、前記容量素子の短絡状態が検出された旨を示す短絡検出信号を出力するコンパレータCMP2と、を備える。

(もっと読む)

信号生成回路

【課題】回路に設けた容量をソフトスタート機能と共用可能でき、タイマ時間の設定の自由度が高くて精度の良いタイマ機能を実現可能な信号生成回路を提供する。

【解決手段】電流供給回路11から供給する電流Issを、回路に設けた共用する容量(Css)12に供給するとともに、差動増幅器21の比較入力としてクランプ回路20に加える。クランプ回路20は、容量(Css)12の電流供給回路11側端子電圧Vssとソフトスタート完了指示電圧Vc10を比較することにより、端子電圧Vssがソフトスタート完了電圧Vc1を上回った場合に、容量(Css)12に供給される電流Issを全て引き込むようしてクランプ機能を働かせる。クランプ回路20がクランプ作動状態に入る少し前に、差動増幅器21の出力Vo1が単相増幅器31のしきい値電圧Vtaを過ぎると、電流Issの切り替え(電流値Iss1から電流値Iss2への切り替え)が行われる。

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

高周波回路のスイッチング方法及び高周波回路

【課題】休止時のゲート−ドレイン間の電圧が小さくなるようにし、また運転/休止の切替え時に低ドレイン電圧領域を通過させないようにする。

【解決手段】高周波回路に含まれる能動素子に対し駆動電圧を与えることにより、この能動素子の運転と休止を切り替える高周波回路及びそのスイッチング方法で、休止状態の能動素子のドレインに、定常運転レベルの電圧Vdを印加し、その後、能動素子のゲートに、定常運転レベルの電圧Vgを印加することにより運転に切り替え、一方、運転状態の能動素子のゲートに、定常運転レベルの電圧Vgに換えてピンチオフ電圧Vpを印加し、その後、能動素子のドレインに印加されている定常運転レベルの電圧Vdを切断することにより、休止に切り替える。

(もっと読む)

半導体集積回路

【課題】負荷短絡状態を検出することで、負荷短絡に起因する焼損を回避する。

【解決手段】半導体集積回路20は、負荷24に接続され、かつ負荷24を介して電源Vccを受ける端子T3と、電源Vssを受ける端子T4と、電源Vccを用いて、電源Vregを生成するレギュレータ30と、電源Vregが供給されるセンサ21からの検知信号に基づいて、電源Vccを降下電圧Vdes以下に設定するシャント回路32と、シャント回路32によるシャント動作時に、負荷24が短絡したか否かを判定し、かつ負荷24が短絡したと判定した場合に負荷24が短絡したことを示す出力信号STPを出力する保護回路33とを含む。

(もっと読む)

半導体装置

【課題】時定数回路を備える半導体装置の回路面積を縮小する。

【解決手段】制御端子P1は、外部抵抗R10が接続されるとともに、時定数キャパシタC10が接続される。制御部10は、制御電圧V1をしきい値電圧Vth3と比較し、比較結果に応じて本半導体装置100の機能を切り替える。充放電回路14は、制御端子P1に接続される時定数キャパシタC10を充電または放電する。半導体装置100は、充放電回路14による充電または放電に応じて変化する制御端子P1の電圧を、時定数電圧V2として利用する。

(もっと読む)

タイマー回路

【課題】小さなコンデンサ容量で精度良く長時間設定のできるタイマー回路を実現する。

【解決手段】本発明のタイマー回路は、周期的にオン/オフを繰り返すスイッチ制御信号Voscに基づいて断続的に一定値の電流Iref2を生成し出力する定電流源11と、一端が定電流源11の出力に接続され、他端がVssに接続され、定電流源11からの出力電流Iref2の電荷を蓄積するコンデンサC2と、コンデンサC2の両端の電圧Vc2を入力回路しきい値と比較するインバータINV1を有する。

(もっと読む)

半導体集積回路装置

【課題】電源電圧などのばらつきがあっても、パワーゲーティング実行の際、消費電力を抑制するために、その開始タイミングを従来よりも精度よく決定可能な半導体集積回路装置を提供する。

【解決手段】パワーゲーティングのための回路が設けられ、動作状態および低リーク状態の間を移行可能な被制御回路と、低リーク状態への変化の際に消費される電力に対応する電荷を蓄積可能な容量部、外部から受信する制御信号が低リーク状態への移行を指示するものであると容量部に電流を供給する電流源、電流源から供給される電流により容量部の電位が基準電位に達したときをパワーゲーティングの開始タイミングとして決定する比較器、および制御信号により比較器を電源と接続する電流遮断用スイッチを含むモニタ回路と、比較器の出力に基づいて前記被制御回路の状態を制御する制御回路とを有する。

(もっと読む)

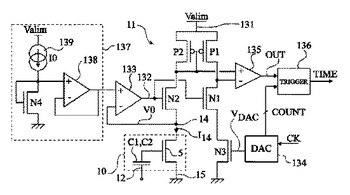

時間測定のための電荷保持要素を読み取る回路

【解決手段】本発明は、その誘電体がリークを示す少なくとも1つの容量性素子(C1,C2) と、残留電荷を読み取るための絶縁された制御ターミナル(5) を含むトランジスタとを備えたタイプの時間測定のための電荷保持電子要素(10)を読み取るための方法及び回路に関し、前記読み取り回路は、第1タイプの少なくとも1つのトランジスタ(P1,P2) と、第2タイプの1つのトランジスタ(N3,5)とを夫々含む、2つの供給ターミナル間の2つの平行な分岐を備えており、前記分岐の一方の第2タイプのトランジスタは、読み取られるべき前記要素のトランジスタから構成されており、前記分岐の他方の第2タイプのトランジスタは、該トランジスタの制御ターミナルでステップ信号(VDAC)を受けており、第1タイプのトランジスタの夫々のドレインは、比較器(135) の夫々の入力に接続されており、比較器の出力(OUT) が、電荷保持要素における残留電圧の表示を与える。  (もっと読む)

(もっと読む)

放電順序制御回路

【課題】パワーオフ時の誤動作を防止可能な放電順序制御回路を提供する。

【解決手段】外部電源VDDにより生成される複数の内部電源VAA,VINTの放電順序を制御する放電順序制御回路であって、外部電源VDDの電位から供給された電荷を蓄積するプール回路100と、最終段のインバータINV20のみをRC遅延を発生させるインバータとしたインバータ列INV21,INV22,INV20を含み、外部電源VDDを立ち下げたときに生成される放電信号を、プール回路100に蓄積された電荷を用いて遅延させる第1の遅延回路(VINT回路)120と、第1の遅延回路120の最終段のインバータINV20の出力ノードN22にゲートが直接接続され、複数の内部電源VAA,VINTのうち一の内部電源VINTにドレインが接続され、接地電位VSSにソースが接続された放電トランジスタQ23とを備える。

(もっと読む)

音声デバイスをパワーアップおよびパワーダウンする間の過渡応答を制御するための回路およびシステム

【課題】負荷(506)にかかる電圧をランピングするための回路及びシステムを提供する。

【解決手段】ランプ上昇波形を発生するためにコンデンサ(501)に充電する充電回路(500)を含む。回路(511)は、選択的に、ランプ上昇モードの間に、負荷(506)から第一ドライバ(510)を切り離し、そして通常動作モードの間に、負荷(506)と第一ドライバ(510)を結合する。ランプ上昇ドライバ(507a)は、充電回路(500)により発生したランプ上昇波形に応答して、負荷(506)にかかる電圧をランプ上昇するためにランプ上昇モードの間に、負荷(506)と選択的に結合する。放電回路(503d,514a,b)は、パワーダウン波形を発生するためにコンデンサ(501)を放電する。回路(511)は、出力負荷(506)に介する電圧のランプ下降の間に、出力負荷(506)から第一ドライバ(501)を選択的に切り離す。

(もっと読む)

ウオッチドッグタイマ回路

【課題】動作周波数の向上と安定化を図ることができるWDT回路を提供する。

【解決手段】入力バッファ2は入力するクロックを正相クロックと逆相クロックに変換し、ピークホールド回路11は正相クロックを遅延させる。可変容量素子3はその遅延量を定める。NAND回路4は逆相クロックとピークホールド回路の出力との否定論理積演算を行い、平均値検出回路9はNAND回路の出力の平均値を検出する。制御回路10は検出された平均値が低下するにつれて可変容量素子の静電容量値を大きくするように制御する。2段のT−フリップフロップ6,7は、クロックと略同じ周波数のクロックを出力するタイマー発振器5からのクロックを入力としたトグル動作を行いNAND回路の出力でリセットされる。

(もっと読む)

デッドタイム制御回路

【課題】 各温度で最適なデッドタイムを得ることができる温度特性調整機能を有し、又は、回路が大型化しコスト的に不利になることが無く、又は、デッドタイムの高精度な制御が可能なデッドタイム制御回路を提供する。

【解決手段】 基準電圧発生回路1と、オペアンプ2、トランジスタ11と抵抗3からなる電圧−電流変換部10と、カレントミラーと、遅延回路8及びAND回路9とを具備するデッドタイム制御回路において、負の温度特性を有する基準電圧発生回路1の出力電圧を電圧−電流変換部10によって電流変換し、その電流をカレントミラーによって伝達し、遅延回路8を構成する少なくとも1つのインバータに流れる電流を制御している。

(もっと読む)

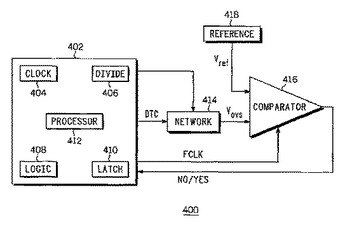

デジタル時定数トラッキング技術及び装置

プロセス、電圧及び温度の変動に起因して回路網(414)の時定数偏差を調整して雑音を無くす方法及び装置を提供する。当該装置(400)は、デジタル時定数が回路網(414)の公称時定数に対して相関されるクロック基準手段(404)を備える。相関されたデジタル時定数は、回路網(414)に印加され、そして出力充電/放電波形スイングが、所定の基準電圧と比較される。当該充電/放電波形スイングが基準電圧と一致しない場合、オフセット信号を発生する。オフセット信号が、制御回路(402)に印加され、当該制御回路(402)は、対応の同調信号を発生する。同調信号は、回路網(414)に印加されて、一致が達成されるまで内部部品を増分的又は減分的に調整する。当該装置(400)は、内蔵型で自己試験型のデジタル時定数トラッキング回路として構成されることでき、且つICチップ上に回路網(414)と一緒に統合化されることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】スイッチング素子を強制的に遮断する際、誘導負荷に発生する過電圧を簡単な回路構成で抑制する技術を提供する。

【解決手段】IGBT1(スイッチング素子)のゲートにゲート放電抵抗部101を接続する。タイマー回路7の出力がゲート放電抵抗部101及びゲート駆動回路9の入力に接続されている。タイマー回路7は、IGBT1をオン状態に駆動するオン信号の入力が所定時間以上継続すると、Hレベルの信号をゲート放電抵抗部101及びゲート駆動回路9に出力する。ゲート駆動回路9は、タイマー回路7からの信号に基づいてIGBT1をオフ状態に駆動する。ゲート放電抵抗部101は、抵抗値を抵抗4の抵抗値から抵抗4と抵抗5の合成抵抗で与えられる抵抗値に変更する。

(もっと読む)

タイマー回路

【課題】小さい回路構成で長い時間の信号を発生することが可能なタイマー回路を提供する。

【解決手段】半導体集積回路に用いられるタイマー回路1において、入力端Aおよび出力端Bの間に接続されたコンデンサ21とコンデンサ21および出力端Bにコレクタが接続されたカレントミラー回路4の出力側トランジスタ11とを設けたタイマー部2と、カレントミラー回路の入力側トランジスタ12と入力側トランジスタ12のコレクタに接続された時間調整用の定電流源であるバイアス回路用カレントミラー回路5とを設けた時間調整部3とを備えたことを特徴とする。

(もっと読む)

1 - 18 / 18

[ Back to top ]