Fターム[5J055EZ32]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211) | 論理素子(INVは除く) (1,593) | メモリ、記憶装置、RAM (572) | 双安定回路、FF (349) | RSFF (79)

Fターム[5J055EZ32]に分類される特許

1 - 20 / 79

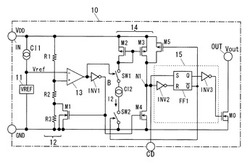

低電圧検出回路

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

半導体集積回路及びそれを備えた駆動装置

【課題】絶縁素子を介した信号伝達に誤動作を生じさせ得る異常を検出して制御対象に停止信号をすることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、外部から供給される送信データVINに応じた送信信号を生成し出力する送信回路Tx1と、受信信号に基づいて送信データVINを再生する受信回路Rx1と、送信回路Tx1と受信回路Rx1とを絶縁するとともに、送信信号を受信信号として伝達する絶縁素子ISO1と、絶縁素子ISO1を介した信号伝達に誤動作を生じさせ得る異常を検出する異常検出部DT1と、異常検出部DT1により異常が検出された場合には、外部から送信回路Tx1に供給される送信データVINに関わらず停止信号を出力する制御部CT1と、を備える。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】ハーフブリッジ回路のメインスイッチング素子が同時オンになることを確実に防止する。

【解決手段】ローサイド側の入力信号を遅延させてローサイド側遅延信号として出力する遅延回路20と、ハイサイド側の入力信号からハイサイド側セット出力信号と予備リセット信号とを生成して出力するパルス発生回路12と、ローサイド側の入力信号がアクティブになってからローサイド側遅延信号がアクティブになるまでの期間、又は予備リセット信号がアクティブである期間にハイサイド側リセット出力信号をアクティブにするリセット信号生成回路30と、を備えるハーフブリッジドライバとする。

(もっと読む)

半導体スイッチング素子駆動回路

【課題】 高コスト化、サイズ大型化を抑制し、短絡保護回路が制限する電流値がばらついても、過電流保護回路を確実に作動させる半導体スイッチング素子駆動回路を提供する。

【解決手段】半導体スイッチング素子駆動回路は、ゲート端子への電圧の印加により第1端子および第2端子間に主電流を流す半導体スイッチング素子Q1と、主電流の大きさに比例する電流値または電圧値が閾値を超えたとき、主電流が所定時間の間、所定の電流値を超える過電流となったと判断して主電流を低下させる過電流保護回路OPと、主電流が所定時間より短時間で過電流よりさらに大きい過電流となる場合に、ゲート端子に印加するゲート電圧を過電流保護回路による主電流の低下よりも早く低下させる短絡保護回路SPと、短絡保護回路の主電流の低下作動時に閾値を小さくする閾値変更回路TCと、を有する。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合に発生する誤信号を確実に除去する半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、スイッチング素子7の導通状態を変化させる場合に第1、第2のレベルシフト素子21、24のオン/オフ状態を必ず同一状態にするためのフリップフロップ52と、マスク信号S11が確実にセット信号S9、リセット信号S10を覆うようにするための第1、2、3の遅延回路44、45、46を有する。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】並列接続された複数の入力回路のうち使用する入力回路を切り替える際に生じる出力ノードの信号ノイズ(ハザード)を防止する。

【解決手段】それぞれが、入力信号INが供給される一つの入力ノードN10に接続し、出力信号OUTを供給する一つの内部出力ノードN11に接続し、互いに電気的特性が異なる第1及び第2の入力回路100A,100Bと、切り替え信号SELを生成し、切り替え信号SELによって、入力回路100A,100Bを制御する入力制御回路300とを備える。入力制御回路300は、入力回路100A,100Bのいずれか一方を活性から非活性へ、いずれか他方を非活性から活性へ切り替えるとき、入力回路100A,100Bが同時に活性状態となる時間を含むように制御する。これにより、入力回路100A,100Bの切り替えに伴う信号ノイズ(ハザード)の発生が防止される。

(もっと読む)

ゲート駆動回路及びゲート駆動方法

【課題】トランジスタの駆動電力の損失を防ぎ且つスイッチング時間の高速化を図る。

【解決手段】接合型トランジスタ2の駆動に必要な基準駆動能力レベル電圧からなる基準波形Sg′及び駆動能力のより高い高駆動能力レベル電圧からなる重畳パルスSpを生成し、重畳パルスSpのパルス幅を、接合型トランジスタ2のスイッチング時間に、若しくはドレイン電位VDの遷移収束タイミングを表す閾値により設定する。基準波形Sg′と重畳パルスSpとを重畳しこれを、接合型トランジスタ2のゲート駆動信号Sgとする。ゲート駆動信号Sgは、接合型トランジスタ2の遷移終了とみなすことの可能なタイミングで基準駆動能力レベル電圧に切り換わることになるため、遷移終了後も高駆動能力レベル電圧で駆動されることにより、接合型トランジスタ2に形成されるダイオードに順方向電流が流れることに伴う電力損失の発生を回避することができる。

(もっと読む)

ドライブ制御回路、制御装置、スイッチング電源装置、および、制御方法

【課題】入力電圧の急変や負荷短絡時等における共振外れにより、中間電位VSが急変した場合にも、ハイサイドドライブ信号SDHとローサイドドライブ信号SDLに応じて、所定の動作をすることが可能なドライブ制御回路を提供する。

【解決手段】ドライブ制御回路101は、ハイサイドスイッチ素子Q1とローサイドスイッチ素子Q2との間の中間端子Xに接続された共振回路の状態を検出することにより得られた状態検出信号Desに応じて、第1のMOSトランジスタM1の他端と第2の電位線9との間の抵抗値を下げる抵抗制御回路2を備える。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】dv/dt過渡信号が印加され且つ入力信号が入力されないとき第1抵抗R1を含むセット側負荷抵抗R1,R9,MP1のオン抵抗及び第2抵抗R2を含むリセット側負荷抵抗R2,R10,MP2のオン抵抗を第1抵抗及び第2抵抗よりも小さくし、トランジスタMN3がオンである場合にセット信号を生成し且つセット側負荷抵抗をリセット側負荷抵抗よりも大きくし、トランジスタMN4がオンである場合にリセット信号を生成し且つリセット側負荷抵抗をセット側負荷抵抗よりも大きくする制御部MN1,MN2,MP1,MP2,R1,R2,R9,R10、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】トランジスタMN3とトランジスタMN4とをオン/オフさせるパルス発生回路10、第1抵抗R1の両端に第3抵抗R9と非線形特性を有し且つ一定以上のdv/dt過渡信号が印加された場合にオンするダイオードD3〜D6とが接続された直列回路、第2抵抗R2の両端に第3抵抗と同じ抵抗値を有する第4抵抗R10とダイオードとが接続された直列回路、MN3がオンである場合にセット信号、MN4がオンである場合にリセット信号を生成し、MN3のドレインにおける電位とMN4のドレインにおける電位との間において電圧差が生じていない場合にはいずれの信号も生成しない制御部、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

ランプ波形生成装置および方法

【課題】本発明は、ランプ波形生成装置および方法に関する。

【解決手段】ランプ波形生成装置は、入力信号を用いて基準波形を生成し、負荷の電圧と基準波形の電圧を比較して第1端子が負荷に連結していて第2端子が電源に連結しているスイッチをオンオフさせる駆動制御信号を生成する。このような駆動制御信号に応じてスイッチのオンオフが反復しながらランプ波形が生成される。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合であっても誤信号が発生することのない半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、レベルシフト回路2の第1の負荷抵抗28、28に発生するオン側、オフ側の第1のレベルシフト済み信号S4、S5のうち少なくとものいずれか一方に信号が発生したときに、第2の負荷抵抗30、29に同時に発生する第2のレベルシフト済み信号S6、S7によって制御され、他方の出力が発生しないようにレベルシフトの出力を抑制する短絡手段31、32を有する。

(もっと読む)

1 - 20 / 79

[ Back to top ]