Fターム[5J055EZ68]の内容

Fターム[5J055EZ68]の下位に属するFターム

液晶 (28)

CRT

Fターム[5J055EZ68]に分類される特許

1 - 20 / 74

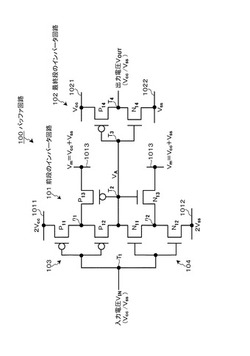

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体装置

【課題】しきい値電圧のばらつきの影響を低減する。

【解決手段】トランジスタのゲート・ソース間に設けられた容量素子に電荷を充電し、その後容量素子に充電された電荷を放電することで該トランジスタのしきい値電圧を取得し、その後負荷に電流を流す半導体装置において、容量素子の一方の端子の電位は、ソース線の電位より大きく設定し、ソース線の電位は電源線の電位及び負荷のカソード側の電位よりも小さい電位に設定する。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

インジケータ駆動回路

【課題】電源電圧の変動によるインジケータの光源のちらつきを抑制するインジケータ駆動回路を提供する。

【解決手段】インジケータ駆動回路1は、2つのnpnトランジスタQ2,Q6からなるカレントミラー回路200と、カレントミラー回路200の制御側のトランジスタQ2に制御電流を供給する電流源であるpMOSトランジスタQ3,Q4と、被制御側のpMOSトランジスタQ6に流れる電流により駆動され、インジケータのLED30をオンオフさせるpMOSトランジスタQ5を備える。電流源100からカレントミラー回路200へ流す制御電流は、外部からの制御信号によりnMOSトランジスタQ1を介して切り換えられる。電流源100を構成する2つのトランジスタQ3,Q4をカスコード接続で構成することで、カレントミラー回路200に流れる電流に対する電源VCCの変動の影響を小さくする。

(もっと読む)

半導体チップおよびそれを用いた画像表示装置

【課題】画像表示装置の昇圧回路の高効率化を図ることが可能な半導体チップと、それを用いた画像表示装置を提供する。

【解決手段】この携帯電話機では、昇圧回路8のトランジスタ12の前段にバッファ14を設け、バッファ14の入力ノードの寄生容量値をトランジスタ12のゲートの寄生容量値よりも小さく設定し、トランジスタ12およびバッファ14を1つの半導体チップ21に搭載する。したがって、トランジスタ12のゲートにおけるPWM信号φPのレベル変化の鈍りを抑制することができ、昇圧回路の高効率化を図ることができる。

(もっと読む)

負荷駆動装置、画像形成装置、負荷駆動方法およびプログラム

【課題】共振を利用し、容量性負荷の両端に逆位相の電圧パルスを印加可能として消費電力を低減する。

【解決手段】外部容量53と、コイルL1〜L3と、負荷容量52と外部容量53とコイルL1とを接続して第3電極から外部容量53に電荷を放電し、外部容量53への放電完了後に負荷容量51と負荷容量52とコイルL3とを接続して端子1−Aから端子2−Aに電荷を放電し、端子2−Aへの放電完了後に負荷容量51と外部容量53とコイルL1とを接続して外部容量53から端子1−Bに電荷を放電することにより、逆位相のパルス電圧を印加するSW駆動部と、を備える。

(もっと読む)

バス幅変換回路、情報入出力装置および電子機器

【課題】光学式のタッチセンサの検査を簡易に行うことの可能なセンサ画素検査用のバス幅変換回路、ならびにそれを備えた情報入出力装置および電子機器を提供する。

【解決手段】バス幅変換回路11cは、複数の受光セルCRを有する入力パネル11に設けられており、受光セルCRの受光信号を出力するN本のセンサ信号線SSigXと、M本(2<M<N)の検査用出力線SoutXとの間に接続されている。バス幅変換回路11cは、N本のセンサ信号線SSigXから入力されるパラレル信号を、M本またはM本よりも少ない数のパラレル信号として、複数の検査用出力線SoutXに出力する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

容量性負荷の駆動装置、及びその駆動装置を搭載するプラズマディスプレイ装置

【課題】容量性負荷である表示パネルを高い効率で駆動するため、表示パネルに急峻な電圧を印加しながらスイッチング損失やリンギングを抑制することが可能な容量性負荷駆動装置を提供すること。

【解決手段】容量性負荷駆動装置は、負荷容量(Cp)を有する表示パネル(20)と、表示パネルに電力を供給する電力供給源(In)と、表示パネルに電力供給源からの電力の供給/遮断を行うスイッチング部(Q1X,Q2X,Q1Y,Q2Y)と、飽和可能な磁心を持つ可飽和インダクタ(LsX)とを有し、表示パネルに電力を供給するとき、表示パネルと、電力供給源と、スイッチング部と、可飽和インダクタとを、電気的に接続状態とするよう構成されている。

(もっと読む)

インバータ回路および表示装置

【課題】より少ない素子数で、さらなる高速化を実現することの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備える。インバータ回路20は、並列関係にあるトランジスタTr21およびトランジスタTr22と、これらのトランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21を有する。閾値補正回路21は、トランジスタTr21のゲートに対して、トランジスタTr21の閾値電圧Vth1(図示せず)またはトランジスタTr21の閾値電圧Vth1に対応する電圧をオフセットとして設定する。閾値補正回路21は、さらに、トランジスタTr22のゲートに対して、トランジスタTr22の閾値電圧Vth2(図示せず)またはトランジスタTr22の閾値電圧Vth2に対応する電圧をオフセットとして設定する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、トランジスタTr2のソースと低電圧線LLとの間、トランジスタTr5のゲートと低電圧線LLとの間、さらにトランジスタTr2のゲートと低電圧線LLとの間に、入力電圧Vinと低電圧線LLの電圧VLとの電位差に応じてオンオフ動作するトランジスタTr1,Tr3,Tr4が設けられている。トランジスタTr5のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr5のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr2のソースに接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3がオフしたときに、Vdd2が充電された容量素子C1によって、トランジスタTr2のゲートがVSS+Vth2以上の電圧にチャージされ、トランジスタTr2がオンする。

(もっと読む)

半導体装置

【課題】EL画素や信号線などの負荷に電流を供給するトランジスタにおいて、バラツキの影響を受けずに正確な電流を供給できる半導体装置を提供する。

【解決手段】増幅回路を使ったフィードバック回路を用いて、電流源回路から電流Idataをトランジスタに入力して、トランジスタが電流Idataを流すのに必要なゲート・ソース間電圧(ソース電位)を設定する構成とすることにより、フィードバック回路で、トランジスタのドレイン電位が所定の電位になるように動作するように制御し、電流Idataを流すのに必要なゲート電圧が設定されたトランジスタを用いて正確な電流を負荷(EL画素や信号線)に供給し、さらにドレイン電位を制御してキンク効果の影響を低減する。

(もっと読む)

半導体回路、インバータ回路および半導体装置

【課題】簡便な回路構成で過電圧から素子を保護する。

【解決手段】高電圧で抵抗値を制御可能なN1において、ドレイン端子は、抵抗R6を介して出力素子NO5のゲート端子(制御端子)、ソース端子は、NO5のエミッタ端子、そして、ゲート端子は、NO5の出力端子であるコレクタ端子に接続される。入力端子がHiレベルの場合、NO5はオフし、この状態で別に設けられた高圧回路の高電位側にNO5の出力端子を接続し、低電位側にVDD4のマイナス電極を接続すると、NO5のコレクタ−エミッタ間には所望の高電圧が印加される。入力端子をLoレベルに切替えると、PD2はオン、NO5の出力端子には未だ高電圧が印加されているので、N1もオンの状態となり、NO5の電流駆動能力は低い状態ではあるが、オン状態となる。

(もっと読む)

1 - 20 / 74

[ Back to top ]