Fターム[5J055FX17]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号はデジタル値であるもの (1,286)

Fターム[5J055FX17]の下位に属するFターム

2値(Yes、NO)であるもの (795)

Fターム[5J055FX17]に分類される特許

161 - 180 / 491

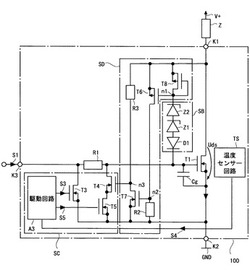

半導体装置

【課題】従来の半導体装置は、負荷のインダクタンス成分等による出力トランジスタの電位差変動を制御できないという問題があった。

【解決手段】本発明にかかる半導体装置は、ゲートに印加される制御電圧に応じて負荷への電源供給が制御される出力トランジスタT1と、T1のゲート−ドレイン間に接続され、T1のソース−ドレイン間の電位差に応じて導通状態が制御される電圧制御回路SBと、SBの導通状態に基づいて電圧制御検出信号を出力する電圧制御検出回路SDと、T1のゲートとソースとの間に接続され、電圧制御検出信号に応じてオンオフが制御されるトランジスタT4と、T4に直列に接続され、T1の温度状況に応じてオンオフが制御されるトランジスタT5と、T4及びT5に並列に接続されたトランジスタT3と、を備える。このような回路構成により、T1の電位差変動を制御することが可能である。

(もっと読む)

レベルシフト回路

【課題】外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態を第1コンデンサC1を介してセットするセットレベル回路20aと、第2電圧レベルの論理状態を第2コンデンサC2を介してリセットするリセットレベル回路20bと、セットレベル回路のセット信号とリセットレベル回路のリセット信号とによりローサイドスイッチQ1に直列に接続されたハイサイドスイッチQ2をオン/オフ駆動する駆動回路24と、第1コンデンサ及び第2コンデンサに流れる電流の内の少なくともいずれか一方を検出する電流検出回路15,16,を備える。

(もっと読む)

半導体装置

【課題】メインスイッチング素子のスイッチングに伴う誤差量を制御することによって、より高精度で信頼性の高い動作が可能な半導体装置の提供を図る。

【解決手段】第1ノードに接続された第1電極S1、第2ノードに接続された第2電極D1、および、該第1および第2電極間の接続を制御する第1制御電極G1を有する少なくとも1つのメインスイッチング素子1と、前記第2ノードに接続される第3電極S2および第4電極D2、並びに、第2制御電極G2を有し、前記メインスイッチング素子1がオンからオフに切り替わるときに生じる電荷をキャンセルする第1キャンセル用素子2と、前記第1キャンセル用素子2の基板電圧VBG2を制御する第1制御部と、を有するように構成する。

(もっと読む)

電流出力回路

【課題】簡易な構成で、消費電力の増加を抑制することができる電流出力回路を提供する。

【解決手段】負荷抵抗Rlの一端と接続し、スイッチングトランジスタQ1のオン/オフ動作に応じて電源電圧を負荷抵抗Rlに供給するスイッチング電源6と、負荷抵抗Rlの他端とコレクタが接続し、エミッタを出力センス抵抗R2を介して接地した電流出力トランジスタQ2とを備え、コンパレータU1が、電流出力トランジスタQ2のコレクタと負荷抵抗Rl間の電圧と、三角波発生器5で発生した三角波信号の電圧とを比較し、両電圧の大小比較に応じたオン/オン比率でスイッチングトランジスタQ1をオン/オフ制御することにより、負荷抵抗Rlに供給される電源電圧を制御する。

(もっと読む)

パワーオンリセット回路

【課題】リセットタイミングのバラツキを低減するとともに、通常動作時の消費電力を低減し、且つ回路面積を小さくする低電流小型のパワーオンリセット回路を提供する。

【解決手段】電源電圧を分圧する複数のトランジスタからなる分圧回路と、分圧回路で分圧された電圧に基づいて電源電圧が所定値以上か否かを検出する回路とからなる電圧検出回路と、電圧検出回路の出力信号が入力するインバータと、インバータの入力と接地との間に接続されたトランジスタと、を備えるパワーオンリセット回路である。

(もっと読む)

改良クロック・ゲーティング・セルを用いるシステム、及び方法

【解決手段】クロック・ゲーティング・セルは、入力イネーブル・ロジック及び出力ロジック回路と接続しているラッチを備え、ラッチは、出力ロジック回路の入力ノードでプル・アップ及び/またはプル・ダウン回路、及びクロック・ゲーティングセルが有効である場合、プル・アップ及び/またはプル・ダウン回路によって、出力ロジック回路入力ノードの早期充電または早期放電を防止する回路を備えている。 (もっと読む)

ドライバ回路およびDC−DCコンバータ

【課題】デッドタイムを設けることなく貫通電流を抑制することができるとともに、貫通電流を抑制しつつ高周波化を図ることができるドライバ回路およびDC/DCコンバータを提供する。

【解決手段】電源端子と接地端子との間に直列形態に接続され、デッドタイムのない相補的な一対の制御信号によってオン、オフ駆動される第1のスイッチング素子(SW1)と第2のスイッチング素子(SW2)を備えるドライバ回路において、少なくとも前記第1のスイッチング素子の制御端子に、オン状態での制御電圧を制限するリミッタ回路(LMT1)を接続するようにした。

(もっと読む)

電気負荷駆動回路、電気負荷駆動方法

【課題】容量成分を有する電気負荷を高い電力効率で正確に駆動する。

【解決手段】所定の電圧範囲内で電圧値の漸増と漸減とを繰り返す目標電圧波形を出力し、目標電圧波形の電圧値に応じて複数の電源部を切り替えながら、電気負荷に出力する出力電圧波形を生成する。また、出力電圧波形が目標電圧波形と一致するように負帰還制御する。出力電圧波形が電気負荷の印加電圧に一致すると出力電圧波形を電気負荷に供給し、目標電圧に達すると出力電圧波形と電気負荷とを切断する。こうすれば、電気負荷の容量成分に蓄えられた電力を回収しながら、電気負荷を駆動することができる。また電源を切り替えているために、回路側での電力損失も抑制できる。加えて、目標電圧波形に従って負帰還制御を行っているため、容量成分を有する電気負荷を、適切にしかも効率よく駆動することが可能となる。

(もっと読む)

高周波半導体スイッチ装置

【課題】各FETの端子間にかかる電圧を抑えつつ、高周波特性の優れた高周波半導体スイッチ装置を提供する。

【解決手段】高周波スイッチ部1に制御信号を供給する駆動回路は、第1のレベルシフト回路11と第2のレベルシフト回路12とを有し、これらはSOI構造の半導体装置に設けられ、第1のレベルシフト回路11のクロスカップルPMOSP11、P12に、ゲートに第1のバイアス電位Vb1(>0)が与えられるカスコード接続PMOSP13、P14を接続し、これらの接続ノードを第2のレベルシフト回路12の入力とし、第2のレベルシフト回路12にPMOSP23、P24およびNMOSN21、N22のカスコード接続段を設け、PMOSP23、P24のゲートには第1のバイアス電位Vb1が、NMOSN21、N22のゲートには第2のバイアス電位Vb2(>Vb1)が与えられる。

(もっと読む)

温度補償回路及び電流源回路

【課題】 簡単な構成で電流源回路を温度補償することができる温度補償回路及び電流源回路を提供する。

【解決手段】 温度補償回路1は、第1トランジスタM1と同チャネル型のMOSFETにて構成した第2トランジスタM2を設けて構成してあり、ゲート電圧生成手段たる第2トランジスタM2のソースは前記第1トランジスタM1のゲートに接続してある。また、温度補償回路1にはスイッチング素子として動作させる第3トランジスタM3が設けてあり、第3トランジスタM3のドレインと第2トランジスタM2のソースとを直列接続してある。

(もっと読む)

地絡保護を備えるハイサイドドライバ

【課題】ハイサイドドライバ用の費用効率の良い保護回路であって、必要コンポーネント数を最小限化し、ソフトウェア介入を必要としない保護回路の提供。

【解決手段】ハイサイドドライバ用保護回路は、第1の入力および第2の入力を受信し、該入力の各々を分析し、該入力の分析に応じて出力を伝送するように構成される排他的ORゲートであって、第1の入力はハイサイドドライバの電力出力を表し、第2の入力は前記ハイサイドドライバの作動のための制御信号を表す、排他的ORゲートと、排他的ORゲートの出力に応答してハイサイドドライバの電気出力を制御するよう構成されるスイッチングデバイスとを含む。

(もっと読む)

接合型電界効果トランジスタの駆動装置および駆動方法

【課題】簡単な構成によって、一時的な過電流による接合型電界効果トランジスタの発熱を抑制するとともに、接合型電界効果トランジスタの過熱状態を検知することができる接合型電界効果トランジスタの駆動装置および駆動方法を提供する。

【解決手段】電流検知部90でモニタする電流が閾値電流を超えた場合、接合型電界効果トランジスタ(JFET)32をターンオンするときのゲート電圧をPN接合のビルトイン電圧より大きくする。これにより、JFET32のオン抵抗を低減させてJFET32の発熱を抑制する。さらに、オン状態のJFET32に流れるゲート電流IGの温度依存性を利用することによって、JFET32の温度の値を簡単に求めることができる。

(もっと読む)

半導体メモリ素子のパワーアップ回路

【課題】パワードロップによるパワーアップ信号の無用なリセットを防止し、メモリの内部ロジックの安定した初期化に必要なマージンを確保するパワーアップ回路を提供する。

【解決手段】電源電圧のレベル変化に応じて線形的に変化する電源電圧レベルフォロワ部200と、前記電源電圧の下降時のパワーアップ信号の遷移レベルに対応する第1臨界レベルへの変化を感知するための第1電源電圧感知部210Aと、前記電源電圧の上昇時のパワーアップ信号の遷移レベルに対応し、第1臨界レベルより相対的に高い電圧レベルを有する第2臨界レベルへの変化を感知するための第2電源電圧感知部210Bと、前記電源電圧の下降時に前記第1電源電圧感知部から出力された第1感知信号に応答して、その出力信号を遷移させ、前記電源電圧の上昇時に第2電源電圧感知部から出力された第2感知信号に応答して、その出力信号を遷移させるためのトリガ部220とを備える。

(もっと読む)

スイッチング制御回路及びスイッチング電源装置

【課題】スイッチング電源装置の入力リップルを特に操作することなくPWM基本周波数を変動させる。

【解決手段】スイッチング素子(201)は、スイッチング電源装置における変圧器(13)への一次電流の供給を制御する。増幅回路(202)は、変圧器(13)の補助巻線の出力リップルを増幅する。ゆらぎ生成回路(203)は、増幅回路(202)の出力に基づいてゆらぎ信号を生成する。基本信号発生回路(204)は、周波数がゆらぎ信号に応じて変動するPWM基本信号を生成する。制御回路(210)は、PWM基本信号を受けたとき、スイッチング素子(201)をオン制御し、スイッチング電源装置の出力帰還に基づくオフ信号を受けたとき、スイッチング素子(201)をオフ制御する。

(もっと読む)

高周波回路、高周波電力増幅装置、及び半導体装置

【課題】マルチバンド又はマルチモードに適した高周波回路、高周波電力増幅装置、及び半導体装置を提供する。

【解決手段】本発明に係る高周波回路は、高周波信号を増幅する高周波回路であって、高周波信号を増幅して増幅信号を出力する増幅回路と、増幅回路の出力と接続された負荷回路と、複数の伝送線路と、増幅信号の所定パラメータに応じて、複数の伝送線路の中から負荷回路の出力と接続する伝送線路を選択する選択回路と、選択回路で選択された伝送線路毎に、増幅回路から増幅回路の出力側をみたときの負荷インピーダンスを所定の負荷インピーダンスに変換する変換回路と、を備える。

(もっと読む)

スイッチング制御回路

【課題】ハーフブリッジ回路を構成する2つのスイッチング素子を共にオンさせるような2つのパルス信号が入力された場合であっても、2つのスイッチング素子が同時にオンすることを確実に防止すること。

【解決手段】第1パルス信号と第2パルス信号に基づいて、第1出力端子(DRV1)4からP型MOSFET(MOS1)10に第1駆動信号が出力され、第1パルス信号と第2パルス信号に基づいて、第2出力端子(DRV2)5から第2スイッチング素子であるN型MOSFET(MOS2)11に第2駆動信号が出力されるように構成され、保護回路20によりP型MOSFET(MOS1)10及びN型MOSFET(MOS2)11のうちの少なくとも一方がオフされるようにした。

(もっと読む)

電気回路のスイッチング装置

【課題】逆方向電流を阻止する機能を有するIGFETの逆方向耐圧の向上が要求されている。

【解決手段】スイッチング装置(10)は、逆方向電流を阻止するショットキダイオードD3を内蔵する主IGFET(11)と、保護スイッチ手段(12)と、保護スイッチ制御手段(13)とを有する。保護スイッチ手段(12)は主IGFET(11)のドレイン電極Dとゲート電極Gとの間に接続されている。保護スイッチ制御手段(13)は、主IGFET(11)に逆方向電圧が印加された時に保護スイッチ手段(12)をオンにする。これにより、主IGFET(11)が逆方向電圧から保護される。

(もっと読む)

高周波半導体スイッチ装置

【課題】チャージポンプの出力容量を低減してチップ面積を縮小できる高周波半導体スイッチ装置を提供する。

【解決手段】アンテナ端子ANTと、各高周波端子TX、RXとの間の接続を切り換える回路であって、アンテナ端子ANTと各高周波端子TX、RXとの間にそれぞれ接続されたスルーFETT1、T2を有する高周波スイッチ回路1と、各スルーFETT1、T2のゲートを駆動する駆動回路11、12と、駆動回路11、12の高電位電源端子に正側出力端子CP_out1が接続され、駆動回路11、12の低電位電源端子に負側出力端子CP_out2が接続された正負両極性チャージポンプ回路15と、を備え、各スルーFETT1、T2のゲート容量はそれぞれ概略等しく、正負両極性チャージポンプ回路15の正側出力端子CP_out1と負側出力端子CP_out2との間に容量Cxが設けられている。

(もっと読む)

サンプリング回路

【課題】サンプリング回路の省電力化を図ること。

【解決手段】アンダーサンプリング方式のサンプリングミキサ回路30において、サンプリングパルス信号である制御信号S1,S2に従って、非サンプリング期間の間、増幅部321の入力端子と接続端子との間が接続されることで増幅部321の増幅動作のON/OFFが制御される。増幅部321の前段の整合回路31は、増幅部321の入力端子と出力端子との間が接続されていないとき、すなわち増幅動作が行われているサンプリング期間では入力インピーダンスを整合させ、増幅部321の入力端子と出力端子との間が接続されているとき、すなわち増幅動作が行われない非サンプリング期間では入力インピーダンスを不整合させる回路素子が選択されている。また、動作制御部323は、制御信号S3,S4に従って、非サンプリング期間の間、増幅部321のトランジスタTr1,Tr2の増幅動作を停止させる。

(もっと読む)

スイッチ入力回路

【課題】安価なマイコンを用いて複数のスイッチのON/OFFの状態を検出する。

【解決手段】スイッチ入力回路1は、マイコン2に設けられるアナログ入力ポートに接続されるスイッチ入力回路であって、アクチュエータの状態に応じてON/OFFが切り替わるスイッチSW1及びスイッチSW2を含み、当該スイッチSW1及びスイッチSW2のON/OFFの組み合わせに応じて、抵抗値が変化するスイッチ回路10と、一端が基準電圧Vccに接続され、且つ、他端がスイッチ回路10に接続される抵抗R20とを備える。

(もっと読む)

161 - 180 / 491

[ Back to top ]