Fターム[5J055FX17]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号はデジタル値であるもの (1,286)

Fターム[5J055FX17]の下位に属するFターム

2値(Yes、NO)であるもの (795)

Fターム[5J055FX17]に分類される特許

81 - 100 / 491

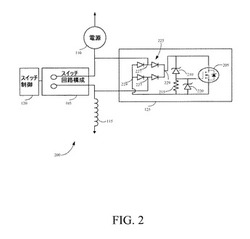

スイッチ両端の電圧を制限するためのシステム、方法、および装置

【課題】電圧クランプ回路構成を用いてスイッチ両端の電圧を制限するためのシステム、方法、および装置を提供する。

【解決手段】電圧クランプ回路構成125は、入力227および出力229を備えた整流器回路225であって、入力227は動作回路構成に渡って並列に連絡する整流器回路225と、整流器回路225の出力229と並列に連絡する電子能動スイッチング素子205と、電子能動スイッチング素子205と並列に連絡する少なくとも1つのツェナー・ダイオード210と、を備えていても良い。電子能動スイッチング素子205およびツェナー・ダイオード210に渡る電圧が所定の値を満たすかまたは超えた場合には、電流が電子能動スイッチング素子205を通って流れて、動作回路構成に渡る電圧を電圧クランプ回路構成125の電圧制限内に制限する。

(もっと読む)

ドライブ信号生成回路、制御装置、スイッチング電源装置、および、制御方法

【課題】発振信号にノイズが発生してデッドタイムパルスが短くなる場合でも、ハイサイドドライブ信号およびローサイドドライブ信号を切り替えて出力することが可能なドライブ信号生成回路を提供する。

【解決手段】ドライブ信号生成回路1は、第1のパルス信号を出力するデッドタイムパルス生成回路1aと、第2のパルス信号Aを出力するデッドタイム調整回路1bと、第3のパルス信号Bを出力する補償パルス生成回路1cと、第2のパルス信号Aと第3のパルス信号Bとの論理和を演算し、この演算結果に応じた第4のパルス信号Zを出力するOR回路1dと、第4のパルス信号Zに応じて、ハイサイドドライブ信号SHおよびローサイドドライブ信号SLを出力する論理回路1eと、を備える。

(もっと読む)

ドライブ制御回路、制御装置、スイッチング電源装置、および、制御方法

【課題】入力電圧の急変や負荷短絡時等における共振外れにより、中間電位VSが急変した場合にも、ハイサイドドライブ信号SDHとローサイドドライブ信号SDLに応じて、所定の動作をすることが可能なドライブ制御回路を提供する。

【解決手段】ドライブ制御回路101は、ハイサイドスイッチ素子Q1とローサイドスイッチ素子Q2との間の中間端子Xに接続された共振回路の状態を検出することにより得られた状態検出信号Desに応じて、第1のMOSトランジスタM1の他端と第2の電位線9との間の抵抗値を下げる抵抗制御回路2を備える。

(もっと読む)

半導体装置

【課題】ダイオード内蔵IGBTを備えた半導体装置において、ダイオード素子とIGBT素子のゲート信号との干渉を回避してダイオードの順方向損失増加を防止する。

【解決手段】メイン用のダイオード素子22aに流れる電流を電流検出用のダイオードセンス素子22bおよびセンス抵抗30にて検出する。他方、フィードバック回路部40にてセンス抵抗30の両端の電位差Vsがモニタされると共に、当該電位差Vsに基づいてダイオード素子22aに電流が流れているか否かが判定される。そして、ダイオード素子22aに電流が流れていると判定された場合、フィードバック回路部40からIGBT素子21aの駆動を停止させる停止信号がAND回路10に入力され、AND回路10にてIGBT素子21aの駆動が停止される。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

半導体スイッチ回路

【課題】一つの切替信号によってスイッチ動作を制御可能とする。

【解決手段】デプレッション型電界効果トランジスタ201とエンハンスメント型電界効果トランジスタ301が直列接続されて設けられ、デプレッション型電界効果トランジスタ201のゲートが第1のゲート抵抗器を介して接地される一方、エンハンスメント型電界効果トランジスタ301のゲートには、第2のゲート抵抗器を介して外部から切替信号が印加可能とされ、前記切替信号の電圧レベルを変化させることで、デプレッション型電界効果トランジスタ201とエンハンスメント型電界効果トランジスタ301の導通、非導通を相補的に切替可能にし、第1乃至第3の高周波入出力端子101〜103における高周波信号の入出力を制御可能としてなるものである。

(もっと読む)

無線通信端末装置

【課題】細かな時間調整を行うことで、CPUセービングの復帰時間を短縮する無線通信端末装置及びそのセービング復帰制御方式を提供する。

【解決手段】CPU10は外部デバイス30aにセービング要求を通知し(S100)、外部デバイス30aは、割り込み出力待ち設定レジスタ31に割り込み出力待ち時間を設定する(S200)。CPU10は、クロック安定時間設定レジスタ11にクロック安定時間を設定し(S300)、CPUセービングに移行する。外部デバイス30aが起動要求信号を入力し(S400)、外部クロック水晶発振子40に「オン」信号を出力し(S500)、外部クロック水晶発振子40は外部クロックをCPU10に出力する(S600)。外部デバイス30aは、割り込み出力待ち時間の経過後にCPU10に割り込み通知を出力する(S700)。CPU10は、クロック安定時間が経過した後に動作を再開する。

(もっと読む)

負荷容量の駆動回路

【課題】2相クロックによる負荷容量の駆動において、負荷容量間の電荷の再利用を行うと共に、出力クロックの高速化を容易にする。

【解決手段】第1クロック信号とその逆位相の第2クロック信号とに対してそれぞれ遅延した第1及び第2遅延クロック信号が生成される。インバータ回路は第1クロック信号と第1遅延クロック信号とが逆位相である逆転期間において第1クロック信号と逆位相の第1電位を第1出力ノードに生成し且つ第2クロック信号と逆位相の第2電位を第2出力ノードに生成し、第1クロック信号と第1遅延クロック信号とが同位相である一致期間において第1出力ノードと第2出力ノードとをハイインピーダンスとする。スイッチ回路は、逆転期間において第1出力ノードと第2出力ノードとを接続するオン状態とする。第1出力ノードと第2出力ノードとは、駆動対象回路の負荷容量に接続される。

(もっと読む)

位相制御装置

【課題】位相制御装置において、トランジスタに与えるゲート駆動電圧を、簡単な構成を用いて全波整流により生成する。

【解決手段】スイッチング手段3は、ソースが交流電源1の一端と、ドレインが負荷2の一端と接続される第1トランジスタ31と、ソースが交流電源1の他端と、ドレインが負荷2の他端と接続される第2トランジスタ32とを含む。定電圧生成手段7のダイオードブリッジ71の一方の入力端子は、交流電源1と第1トランジスタ31の接続点に接続され、ダイオードブリッジ71の他方の入力端子は、交流電源1と第2トランジスタ32の接続点に接続される。定電圧生成手段7の出力端子間には、抵抗72とツェナーダイオード74及びコンデンサ73の並列回路とが直列に接続される。トランジスタ31,32の制御端子の電位は、この並列回路と抵抗72の接点の電位と、ダイオードブリッジ71の負側の出力端子の電位との間で切り換わる。

(もっと読む)

ミリメートル波減衰器及びシャントスイッチング回路

【課題】ミリメートル波周波数において有効な切替え可能減衰器を提供する。

【解決手段】入力減衰器22は、直列結合されているRF_IN+端子、第1のノード、伝送線路TL3、直流遮断キャパシタCbl3、第2のノード、第3のノード、及び出力端子を有する第1の入力回路215を有する。第1のノードは、直列結合されているキャパシタCm3及び第1のシリコンゲルマニウムヘテロ接合バイポーラトランジスタQ9を介して選択的に接地へ結合される。第2のノードは、キャパシタCm1を介して接地へ結合されている。第3のノードは、直列結合されている直流遮断キャパシタCbl1、抵抗Ratt1及び第2のシリコンゲルマニウムヘテロ接合バイポーラトランジスタQ7を介して選択的に接地へ結合される。入力減衰器22は、更に、第1の入力回路215と並列に、第1の入力回路215と同じ構造を有する第2の入力回路216を有する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

パワーモジュール

【課題】過電流保護の判定を高精度に行うパワーモジュールの提供を目的とする。

【解決手段】本発明のパワーモジュールは、主電極及びセンス電極を有する半導体デバイス1と、一端が半導体デバイス1のセンス電極Sに接続され、半導体デバイス1の主電流に応じたセンス電流を電圧変換するセンス抵抗Rsと、センス抵抗Rsの他端を制御グランドに接続する第1配線4と、主電極を主端子Eに接続する第2配線5と、第2配線5の主電極側を第1配線4のセンス抵抗Rs側に接続する第1電流経路6と、第1配線4の制御グランド側を第2配線5の主端子E側に接続する第2電流経路7と、を備える。

(もっと読む)

スイッチングトランジスタの制御回路およびそれを用いた電力変換装置

【課題】消費電力を抑制しつつ、ハイサイドトランジスタの誤動作を防止可能な制御回路を提供する。

【解決手段】制御回路12はハイサイドトランジスタM1を制御する。負電圧回路20は、動作状態と停止状態が切りかえ可能であって、動作状態においてハイサイドトランジスタM1の低電位側端子(ソース)より低いローレベル駆動電圧V4を発生し、停止状態において消費電流が低下する。ハイサイド駆動回路14は、ハイサイドトランジスタM1のオン、オフを制御する制御信号G1を受け、制御信号G1がハイサイドトランジスタM1のオフを指示するとき、ハイサイドトランジスタM1の制御端子(ゲート)に、ローレベル駆動電圧V4に応じた駆動電圧VG1を印加する。制御装置8は、負電圧回路20の動作状態と停止状態を切りかえる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、トランジスタTr2のソースと低電圧線LLとの間、トランジスタTr5のゲートと低電圧線LLとの間、さらにトランジスタTr2のゲートと低電圧線LLとの間に、入力電圧Vinと低電圧線LLの電圧VLとの電位差に応じてオンオフ動作するトランジスタTr1,Tr3,Tr4が設けられている。トランジスタTr5のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr5のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

インバータ回路および表示装置

【課題】耐圧を上げることなく、消費電力を低減することの可能なインバータ回路およびそれを備えた表示装置を提供する。

【解決手段】7Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr7のゲートに接続されている。トランジスタTr7のソースには、トランジスタTr2のゲートが接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3,Tr6がオフしたときに、Vddが充電された容量素子C1によって、トランジスタTr7のゲートがVSS+Vth7以上の電圧にチャージされ、トランジスタTr7がオンし、さらにトランジスタTr2がオンする。

(もっと読む)

高周波スイッチ回路

【課題】少なくとも25GHz帯の高周波帯で高性能な特性が得られる高周波スイッチ回路を提供する。

【解決手段】第3整合回路112及び第4整合回路122は、マイクロストリップライン等の分布定数回路で構成されており、特性インピーダンスがZ0で線路長が1/4波長となるように形成されている。第3整合回路112と第1スイッチ113、及び第4整合回路122と第2スイッチ123をそれぞれ組み合わせることで、送信側高周波スイッチ110及び受信側高周波スイッチ120を、ショートまたはオープンの状態に切り替えることができる。送信側高周波スイッチ110または受信側高周波スイッチ120がショート状態になるとそのスイッチが閉となり、オープン状態になると開となる。

(もっと読む)

電気負荷の電流制御装置

【課題】常温環境のみで初期校正を行ない、実用温度環境においても正確な電流制御を行なう。

【解決手段】所定の温度特性を有する電流検出抵抗126の側近位置に温度センサ171を配置して、校正環境と実用環境における抵抗値を推定すると共に、目標負荷電流に対応した校正環境における実測負荷電流を制御特性データとして記憶し、目標負荷電流に対応した補正目標電流を算出し、電流検出抵抗の変動比率に基づく換算目標電流を電流制御の目標電流として制御する。温度センサ171では完全には検知できない電流検出抵抗126の発熱による抵抗変動分は、制御特性データの中で補正され、制御特性の線形性が改善される。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

半導体基板および半導体装置

【課題】トレンチゲート型などの微細MOSFETにおいて、MOSFETの動作電流とダイオード電流を検出することができる半導体基板を提供する。

【解決手段】半導体基板において、半導体基板1は、主電流領域2と主電流領域2に流れる主電流より小さい電流が流れる電流センス領域3を有し、主電流領域2は、主面にソース電極8が配置され、ソース電極8はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、電流センス領域3は、主面にMOSFET電流検出用電極10およびダイオード電流検出用電極11が配置され、MOSFET電流検出用電極10はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、ダイオード電流検出用電極11はp型半導体領域(ボディ)6に接触する。

(もっと読む)

センサ用出力ICおよびセンサ装置

【課題】センサ装置の回路規模および製造コストを従来よりも抑制しつつ、負荷短絡保護機能を実現する。

【解決手段】センサ用出力IC10は、センサからの検出信号に基づき、出力端子間をオン・オフするための出力用トランジスタ11を備える。センサ用出力IC10は、センサ用出力IC10内の温度が所定値以上になると、出力用トランジスタ11をオフ状態に維持する温度制限回路13と、出力用トランジスタ11のベース電位VBを所定値以下に制限する電圧制限回路15とを備えている。

(もっと読む)

81 - 100 / 491

[ Back to top ]