Fターム[5J055FX38]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393) | 比較器(デジタル、アナログ) (291)

Fターム[5J055FX38]に分類される特許

1 - 20 / 291

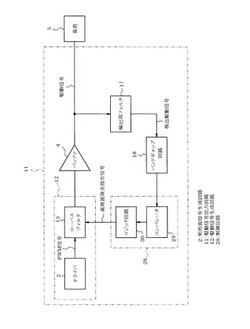

負荷駆動装置

発振回路、およびDC−DCコンバータ

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

低電圧検出回路

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

モード選択回路

【課題】設定に用いる端子数を減らすことができ、且つ回路規模の小型化を図りうるモード選択回路を提供する。

【解決手段】モード選択回路1には、通電経路5の電流状態に応じた定電流を複数の電流比較経路7に流す定電流生成回路9が設けられている。更に、複数の電流比較経路7に対してそれぞれ比較電流を流す定電流源40が設けられ、定電流源40によって複数の電流比較経路7に流される比較電流が互いに異なる電流値となるように構成されている。更に、電流比較部20は、それら複数の各比較電流と前記定電流とを比較したときの比較結果をモード判定部30に出力しており、モード判定部30はこのような比較結果を得ることで通電経路5の状態に応じたモードに設定している。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

ドライブ回路

【課題】ベース電流による電力損失を低減するドライブ回路を提供する。

【解決手段】BJT21のベース端子にベース電流を供給するドライブ回路1は、BJT21のベース電流を生成するベース回路部30と、制御端子に供給される制御電圧に基づき、ベース電流を生成するための駆動電圧をベース回路部30に供給するドライブ部10と、BJT21のベース端子とBJT21のエミッタ端子との間に発生する第1のベース−エミッタ間電圧Vbeを検出し、検出した第1のベース−エミッタ間電圧Vbeに応じたベース電流をBJT21に供給するように制御電圧を制御して、ドライブ部10に供給するベース電流制御部50とを備える。

(もっと読む)

リセット回路

【課題】減電検出を利用して確実にリセットを掛ける。

【解決手段】整流電圧V+をレギュレータ24にてレギュレートした定電圧3.3Vを駆動電圧とされるマイコン30のリセット端子に接続される端子2と抵抗R1を介して定電圧3.3Vを入力される端子4とを備え、端子4の入力電圧が第1閾値を下回るとマイコン30にリセット信号を出力するリセットIC12と、抵抗R2を介して端子4にコレクタを接続され、エミッタをグランドに接続され、スイッチングトランス21の出力が所定レベルを下回るとオンするように構成されたトランジスタQ1と、を備え、トランジスタQ1がオンすると端子4に第1閾値を下回る電圧を入力する。

(もっと読む)

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

1 - 20 / 291

[ Back to top ]