Fターム[5J056AA40]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 整合 (285)

Fターム[5J056AA40]に分類される特許

61 - 80 / 285

インピーダンス調整回路

【課題】伝送経路の入力バッファ端のインピーダンスの最適化を実現可能なインピーダンス調整回路を提供すること。

【解決手段】本発明に係るインピーダンス調整回路100は、入力信号がVREFA6を超えたことを検出する第1の入力バッファ4と、入力信号がVREFA6より高いVREFA7を超えたことを検出する第2の入力バッファ5と、第1の入力バッファ4の出力に基づく計数を行うカウンタ回路A10と、第2の入力バッファ5の出力に基づく計数を行うカウンタ回路B11と、カウンタ回路A10のカウンタによる計数結果とカウンタ回路B11による計数結果とに基づいて、伝送路の終端に設けられる終端抵抗3のインピーダンスを制御する終端抵抗制御回路19と、を備える。

(もっと読む)

高周波回路の設計方法、高周波回路

【課題】少数の部品で高周波回路の安定性を向上させる。

【解決手段】電子回路と、該電子回路に並列に接続されたスタブと、該電子回路に並列に接続された抵抗と、を有する高周波回路において、該抵抗を分布定数回路である等価回路に置き換え、該高周波回路で用いられる第1の周波数で前記高周波回路のインピーダンスマッチングがとれており、且つ前記高周波回路が安定すべき第2の周波数で前記高周波回路が安定するように、前記スタブのインピーダンス値と、前記等価回路の抵抗値とを設定する。

(もっと読む)

半導体装置と信号伝送システムと信号伝送方法

【課題】レシーバの終端抵抗値やドライバのオン抵抗の決定の最適化を図り、且つ、該決定の工数を削減する半導体装置、システム、方法の提供。

【解決手段】、伝送信号のDC電圧レベルとAC電圧の振幅の一端のレベルを一致させるように、レシーバの終端抵抗値(RTT)やドライバのオン抵抗Ronを調整する。

(もっと読む)

ターミネーション回路及びそれを備えるインピーダンス整合装置

【課題】回路面積を増加させることなく、多様なターミネーションインピーダンス値を提供するターミネーション回路及びこれを備えるインピーダンス整合装置を提供すること。

【解決手段】本発明に係るインピーダンス整合装置は、インピーダンス値を較正するためのインピーダンス調整コードを生成するキャリブレーション回路310と、インピーダンス値設定情報に応じて前記インピーダンス調整コードを変更し、変更された前記インピーダンス調整コードを出力するコード変更部320と、変更された前記インピーダンス調整コードに応じて決定されるインピーダンス値でインタフェースノードをターミネーションするターミネーションインピーダンス部330、340と、を備える。

(もっと読む)

終端抵抗調整回路

【課題】入力差動信号のコモン電圧が変化しても、終端抵抗を一定に保持でき、かつ、簡易な回路構成の終端抵抗調整回路。

【解決手段】抵抗値を調整可能な第1の終端抵抗回路と、第1の終端抵抗回路と並列に接続され、抵抗値を調整可能な第2の終端抵抗回路と、第1及び第2の終端抵抗回路の抵抗値を調整するための調整用抵抗回路と、調整用抵抗回路により定まる第1の電圧と、外部に接続された基準抵抗により定まる第2の電圧とが入力され、両電圧が等しくなるように動作するとともに、第1及び第2の終端抵抗回路に対し抵抗調整信号を出力する第1の増幅回路と、第1の終端抵抗回路が接続された第1の端子と、第2の終端抵抗回路が接続された第2の端子と、第1及び第2の端子に与えられる差動信号のコモン電圧に基づく電圧と、第1又は第2の電圧とが入力され、両電圧が等しくなるように動作する第2の増幅回路と、を備える終端抵抗調整回路。

(もっと読む)

車載通信装置

【課題】ネットワークの幹線や支線を含むワイヤハーネスの構成や配線の取り回しに関する自由度が高く、装置全体のコストの上昇を抑制可能な車載通信装置を提供する。

【解決手段】3以上の通信ノード及びこれらの間を接続する通信線路を備える車載通信装置であって一端に第1の通信ノード21が接続され他端に第2の通信ノード24が接続される幹線31と、第1の通信ノードに接続された第1の幹線終端抵抗51と、第2の通信ノードの位置に接続された第2の幹線終端抵抗52と、線路の長さが幹線31よりも短く規制され前記幹線の線路の中間部に一端が接続された支線35と、支線35の他端と接続され入力インピーダンスが第1の幹線終端抵抗51及び第2の幹線終端抵抗52よりも十分に大きい信号中継部30とを設けた。

(もっと読む)

ドライバ・コンパレータ回路およびそれを用いた試験装置

【課題】双方向伝送において送信信号をキャンセルする。

【解決手段】第1抵抗R1は、その第1端子に第1電圧VH’が印加され、その第2端子が入出力端子P1と接続される。第2抵抗R2は、その第1端子に第1電圧VH’が印加される。テイル電流源12は、所定のテイル電流Ia’を生成する。電流スイッチ10は、第2デバイス102に送信すべきデータPATを受け、その値に応じて第1抵抗R1の第2端子と第2抵抗R2の第2端子の一方を選択し、テイル電流源12と結合する。分圧回路DIV1は、第1抵抗R1の第2端子と第2抵抗R2の第2端子の間に順に直列に設けられた第3抵抗R3および第4抵抗R4を含む。負荷バランサLB1は、その第1端子に第2電圧VLBが印加され、その第2端子が第2抵抗R2の第2端子と接続された第5抵抗R5を含む。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】インピーダンス整合のためのコストを増大させずに高周波クロック信号の伝送効率を高める。

【解決手段】一実施形態に係るクロック供給装置は、クロック信号を生成するクロックジェネレータ21に接続される第1伝送線路T1と、このクロックジェネレータ21の出力インピーダンスとは異なる入力インピーダンスを持つクロック供給先12Aに接続される第2伝送線路T2と、第1および第2伝送線路T1,T2を容量結合するキャパシタCP1と、第1伝送線路T1上でクロック信号の反射を抑制するプルアップ抵抗RP1と、分圧で得られる電位をクロック信号の基準電位として第2伝送線路T2に印加する一対の分圧抵抗RP3,RP2とを備える。一対の分圧抵抗RP3,RP2は第2伝送線路T2上のインピーダンスをクロック供給先12Aの入力インピーダンスに整合させる抵抗比に設定される。

(もっと読む)

高周波スイッチ及び受信回路

【課題】簡単な構成でセルフミキシング信号の発生を低減する高周波スイッチ及びこれを用いた受信回路を提供する。

【解決手段】ゲート端子が入力端子側に接続され、ドレイン端子が出力端子側に接続され、ソースが接地された電界効果トランジスタと、前記電界効果トランジスタのゲート端子側に接続されるゲートバイアス電圧調整手段とドレイン端子側に接続されるドレインバイアス電圧調整手段の少なくともいずれか一方を備え、前記ゲート端子と入力端子との間及び前記ドレイン端子と出力端子との間の少なくともいずれか一方に整合回路を備え、導通状態における反射特性と前記遮断状態における反射特性とが略等しくなるように、スイッチを構成している。

(もっと読む)

出力回路及び表示装置の駆動回路

【課題】出力回路の出力部の電圧降下を抑制すると共に、出力回路の入力部へ帰還される出力信号の位相の遅れを抑制することができる。

【解決手段】入力信号が入力されたオペアンプ30の出力端子(OUT)から出力されたデータ信号の交流成分は、コンデンサ34を介して負帰還されてオペアンプ30の反転入力端子へ入力される。また、オペアンプ30の出力端子(OUT)から出力されたデータ信号の直流成分は、第2の保護抵抗36によって電圧降下し、入力信号と同電位の出力信号となって出力パッド28を介して対応するデータ線20へ入力されると共に、第1の保護抵抗32を介してオペアンプ30の反転入力端子へ入力される。

(もっと読む)

受信回路

【課題】差動信号の反射を低減するインピーダンス補償回路を有する受信回路を提供する。

【解決手段】終端処理された第1,第2の信号線が接続される受信回路において,第1,第2の信号が入力される信号入力回路と,第1,第2の入力端子への差動信号供給を検出する差動信号検出部とを有し,差動信号検出部は,第1の信号よりも第2の信号の電位が高い場合であって,第1と第2の信号が第1の電位差を有する場合に,第1の入力端子に第1の電流を流入し,第1と第2の信号が第1の電位差よりも小さい第2の電位差を有する場合に,第1の入力端子に第1の電流よりも小さい第2の電流を流入し,さらに,第1の信号よりも第2の信号の電位が高い場合であって,第1の電位差の場合に,第1の入力端子に第3の電流を流入し,第2の電位差の場合に,第1の入力端子に第3の電流よりも大きい第4の電流を流入するインピーダンス補償回路を有する。

(もっと読む)

LVDSドライバ、LVDS回路、LVDS回路の抵抗値調整方法および電流値調整方法

【課題】基板上での回路部品のレイアウトが相違しても差動信号の適正な伝達が可能なLVDSドライバ、LVDS回路、LVDS回路の抵抗値調整方法およびLVDS回路の電流値調整方法を得ること。

【解決手段】LVDSドライバ21とLVDSレシーバ22を接続する第1の信号線21eと、第2の信号線21fの間に送信側抵抗値設定手段21gを配置して、この抵抗値をスイッチ手段のオン・オフによって適正な値に設定し、レイアウトの相違に対処できる。電流源21aの流す電流値を同様に抵抗で調整することで電流消費の低減も可能になる。

(もっと読む)

通信システム、及びノード

【課題】差動信号の伝送路として、幹線と、該幹線からそれぞれ分岐する複数の支線とを有し、その各支線にノードが接続された通信システムにおいて、通信に必要な信号振幅を確保しつつ反射を抑制する。

【解決手段】ノード内のトランシーバ15は、回路55と抵抗56とからなる回路50を備える。回路55は、直列接続されたダイオード51,53と、同じく直列接続されたダイオード52,54とが並列に接続されたものである。バス10の電位が回路55の順方向電圧降下分以下であれば回路55に電流は流れず、バス10から見たインピーダンスは高く維持され、受信バッファ42に安定した信号を入れることができる。一方、バス10の電位が回路55の順方向電圧降下分を超えたことで回路55に電流が流れると、バス10から見たインピーダンスは抵抗56のインピーダンスとなり、インピーダンスマッチングで反射を抑制できる。

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

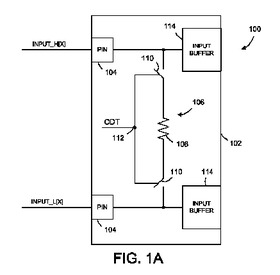

差動式オンライン終端

メモリデバイス及びシステムには、信号線に対するオンチップ終端が組み込まれている。メモリデバイスは、集積回路チップを備える。該集積回路チップは、1対の入力信号を提供する1対の入力信号ピンと、該入力信号ピンの対間に結合されるオンチップ終端回路とを備える。該オンチップ終端回路は、前記1対の入力信号を差動式に終端する。  (もっと読む)

(もっと読む)

半導体装置

【課題】出力バッファのインピーダンス調整を行う半導体装置を提供する。

【解決手段】制御回路1は、外部からの読み出しまたは書き込みコマンドに応じてDQイネーブル信号を発生する。コマンドラッチ回路2Aは、外部からのコマンド信号(ZQコマンド)に応じて、ZQEnable信号を発生する。ZQ調整回路3は、ZQEnable信号が入力されると、内部に設けられたレプリカ回路のインピーダンス調整を始める。ZQ調整回路3は、DQイネーブル信号が入力される期間中は、インピーダンス調整結果であるドライバコードのDQ回路4への出力を禁止する。

(もっと読む)

半導体装置

【課題】高い精度のインピーダンス調整回路を有する半導体装置を提供する。

【解決手段】可変抵抗回路と外部抵抗素子との分圧電圧と、基準電圧とを比較する差動増幅回路にオフセット調整回路を設ける。オフセット調整回路は、第1と第2オセット調整信号によりそれぞれオン/オフ制御されて上記差動増幅回路の第1と第2負荷抵抗に流れる電流を形成し、それぞれ並列形態にされた複数からなる第2と第3MOSFET群を有する。上記差動増幅回路の両入力に基準電圧を供給した状態にし、上記第2と第3MOSFET群に供給される第1オフセット調整信号による電流を変化させて上記差動増幅回路及びデジタル変換段を通した出力信号が変化した時点での第1オフセット調整信号又は上記第2オフセット調整信号をオフセット調整設定信号とする。

(もっと読む)

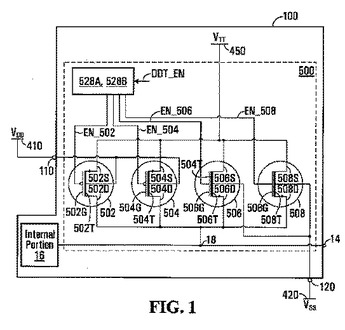

オンダイ終端のための終端回路

内部部分に接続されている端子を有する半導体デバイスにおいて、そのデバイスの端子用のオンダイ終端を提供するための終端回路。この終端回路は、端子と電源の間に接続された、少なくとも1つのNMOSトランジスタおよび少なくとも1つのPMOSトランジスタを含む複数のトランジスタと、NMOSトランジスタのそれぞれのゲートを対応するNMOSゲート電圧でドライブし、PMOSトランジスタのそれぞれのゲートを対応するPMOSゲート電圧でドライブするための制御回路であって、オンダイ終端が有効である場合にトランジスタを動作のオーム領域におくようにNMOSゲート電圧およびPMOSゲート電圧を制御するように構成されている、制御回路とを含む。電源は、上記NMOSゲート電圧のそれぞれより小さく、上記PMOSゲート電圧のそれぞれより大きい電圧を供給する。  (もっと読む)

(もっと読む)

半導体装置及びそのスルーレート制御方法

【課題】インピーダンス不整合を生じさせることなく、シンボル間干渉によるデータウィンドウの悪化を防止し、安定した高速動作を実現する。

【解決手段】半導体装置は、シリアルデータのデータ間論理比較を行って比較結果を生成する比較手段と、前記シリアルデータに基づいて生成される出力信号のスルーレートを、前記比較結果に基づいて制御するスルーレート制御手段と、を有している。

(もっと読む)

ドライバストレングス調整回路、半導体集積回路、及びドライバストレングスの調整方法

【課題】本発明は、高速にドライバストレングスの調整を行うことが出来、また一度ドライバストレングスの調整を行なった後も、温度や電圧といった外部要因に基づいたドライバストレングスの再調整が可能となるドライバストレングス調整回路、半導体集積回路、及びドライバストレングスの調整方法を提供することを課題とする。

【解決手段】コード情報を、電圧、温度、プロセスばらつきと対応づけてテーブルに記憶する。変化する温度/電圧、及びプロセスばらつき情報を用いてテーブルを参照してコード情報を求めドライバストレングスの調整を行う。

(もっと読む)

61 - 80 / 285

[ Back to top ]