Fターム[5J056AA40]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 整合 (285)

Fターム[5J056AA40]に分類される特許

121 - 140 / 285

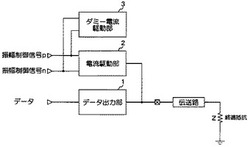

出力装置、多値出力装置、及び半導体集積装置

【課題】ディエンファシス時と非ディエンファシス時の消費電流を一定にすることで、電源変動も一定となり、その結果ジッタの低減を可能にする出力装置を提供する。

【解決手段】入力されたデータを振幅制御して出力するデータ出力部1と、第1及び第2の振幅制御信号に基づいて伝送路に電流を重畳出力して伝送信号の振幅を制御する電流駆動部2と、第1及び第2の振幅制御信号に基づいて電流駆動部2との合計消費電流値が略一定となるように消費電流を制御するダミー電流駆動部3と、を備えて構成されている。

(もっと読む)

半導体装置、およびドライバ制御方法

【課題】半導体装置内のドライバ部(データ伝送路を駆動するドライバ部)において、線形なI−V特性をもつドライバ部を提供する。

【解決手段】本発明の半導体装置では、ドライバ2のプルアップ側において、抵抗素子が直列に挿入されたPchトランジスタP1、P2、P3を用意し、Pchトランジスタ側のON抵抗と抵抗素子の抵抗値とを選択可能に構成する。また、ドライバ2のプルダウン側においても、抵抗素子が直列に挿入されたNchトランジスタN1、N2、N3を用意し、Nchトランジスタ側のON抵抗と抵抗素子の抵抗値とを選択可能に構成する。そして、これらを任意に組み合わせる事で、線形なI−V特性をもつドライバ2を実現する。

(もっと読む)

半導体システム

【課題】

装置稼動中における高速伝送路の信号品質劣化を精度の良く予兆し、障害発生を回避する。

【解決手段】

装置稼動中の温度変化によるバッファのインピーダンス変動に追随して、最適なインピーダンス調整値を出力する調整値制御論理の出力調整値と、既に設定されているインピーダンス調整値を照合し、その照合結果を予兆報告として利用して、関係するバッファが含まれる線路の使用を制御することで、当該線路の障害発生を回避する。

(もっと読む)

半導体回路およびそれを用いた計算機ならびに通信装置

【課題】製品適用への必須条件である温度変化などの環境変化時の抵抗調整を自動で行うことができる技術を提供する。

【解決手段】半導体回路において、非線形の抵抗特性を持つ回路と同一の特性を持つインピーダンス調整回路40は、基準抵抗との動作点をフィードバック制御で自動的に求める動作点算出回路50と、この動作点算出回路50で求めた動作点でのインピーダンスを算出するインピーダンス算出回路60とを有する。さらに、インピーダンス算出回路60で算出されたインピーダンスが所定範囲内に入っているか否かを判断するインピーダンス判定回路を有する。これらの動作点算出回路50、インピーダンス算出回路60およびインピーダンス判定回路は、それぞれHigh側インピーダンス調整用とLow側インピーダンス調整用とを有する。

(もっと読む)

インタフェース回路及び送受信システム

【課題】伝送線路が規格を満たさない場合においても、伝送波形の規格を満足させることが可能なインタフェース回路及び送受信システムを提供する。

【解決手段】フレキシブル配線板のように、インピーダンスの大きな伝送線路がある場合、制御部14は信号送信時に、終端抵抗を信号受信時よりも大きくなるようにする(たとえば、抵抗R1<R2の場合、抵抗R2を選択する)。これにより、初期電圧が大きくなり、伝送波形の規格を満たすことが可能になる。

(もっと読む)

差動信号出力装置

【課題】電源電圧の変動によって伝送信号に生じるジッタを抑制することができる差動信号出力装置を提供すること。

【解決手段】伝送データを差動信号として出力する差動信号出力装置において、伝送データを表す信号を増幅し、増幅した信号から差動信号を生成する第1差動信号生成回路4と、伝送データの基準クロックに同期し、伝送データが遷移しないビットにおいてのみ遷移するダミーデータを生成するダミーデータ生成回路3と、ダミーデータを表す信号を増幅し、増幅した信号から差動信号を生成する第2差動信号生成回路5と、を備える。

(もっと読む)

差動送信回路、差動受信回路、信号伝送回路および信号伝送システム

【課題】消費電流を削減することができ、回路設計が簡単な信号伝送回路を実現することができる。

【解決手段】差動送信回路ブロック110は、アイドル状態のときに所定の論理信号に固定された差動出力信号を差動受信回路ブロックに出力すると共に、終端抵抗118aと118bを信号伝送路から切り離す。差動受信回路ブロック130において、差動比較回路131は、差動送信回路ブロック110からの差動出力信号の符号により決まる論理を出力し、動作状態検出回路136は、差動比較回路131が所定の論理を連続して出力する時間が所定時間に達したことを検出することによりアイドル状態の検出を行い、アイドル状態を検出した際に、終端抵抗134aと134bを受信側の信号伝送回路から切り離すようにスイッチ132aと132bを制御する。

(もっと読む)

インピーダンス調整回路

【課題】 DIMMに実装されているSDRAMのOCDインピーダンス測定・調整が短時間で実行でき、設計が容易なインピーダンス調整回路を提供する。

【解決手段】 調整コードに対応してインピーダンスが可変の出力ドライバを有する、複数のメモリチップD0〜D7をランク選択信号とデータマスク信号の組合せにより選択して、インピーダンスの測定及び調整を行うインピーダンス調整回路において、異なるランクのメモリチップD0〜D7にランク選択信号をそれぞれ出力する複数のランク選択回路31,32と、ランクごとにメモリチップを選択するデータマスク信号をそれぞれ出力する複数のデータマスク選択回路41〜48とを備えたことを特徴とする。

(もっと読む)

キャリブレーション回路及びこれを備える半導体装置、並びに、メモリモジュール

【課題】キャリブレーション端子に現れる電圧をより高速に安定させる。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ110と、レプリカバッファ110に並列接続されたプリエンファシス回路171と、レプリカバッファ110及びプリエンファシス回路171のインピーダンスを変化させるアップダウンカウンタ140とを備える。レプリカ制御回路110aはインピーダンスコードDRZQPに基づいてレプリカバッファ110を導通させ、プリエンファシス制御回路171aはレプリカバッファ110の導通期間の初期においてプリエンファシス回路171を導通させる。これにより、例えば複数個の半導体装置に対して外部抵抗を共有している場合であっても、キャリブレーション端子ZQに現れる電圧をより高速に安定させることができる。

(もっと読む)

半導体集積回路装置

【課題】簡単な構成のインピーダンス調整回路を備えた半導体集積回路装置を提供する。

【解決手段】第1インピーダンスコードにより出力インピーダンスが可変にされてなる複数組の出力回路と外部端子に接続された第1抵抗素子に対応して上記第1インピーダンスコードを生成する第1インピーダンス制御回路と有する。上記第1インピーダンス制御回路は、上記第1インピーダンスコードをシリアルデータに変換して送出するエンコーダを有する。上記複数組の出力回路のそれぞれは、上記シリアルデータを受けて上記第1インピーダンスコードを再生するデコーダを有する。

(もっと読む)

キャリブレーション回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】外部クロックの周波数が高い場合であっても、正しくキャリブレーション動作を実行する。

【解決手段】レプリカバッファ110,120と、レプリカバッファ110,120のインピーダンスコードDRZQP,DRZQNを変化させるアップダウンカウンタ140と、インピーダンスコードをそれぞれ保持するラッチ回路141,142と、レプリカバッファ110,120のインピーダンス調整完了に応答してラッチ回路141,142を活性化させる終了判定回路161と、キャリブレーションコマンドZQCSの発行から所定の期間が経過したことに応答して、強制的にラッチ回路141,142を活性化させる32tCKサイクルカウンタ162とを備える。これにより、1回のキャリブレーション期間で調整が完了しなかった場合であっても、次回のキャリブレーション動作を続きから実行することができる。

(もっと読む)

少なくとも1個の差動ラインを駆動する回路装置及び方法

データ伝送、特にデジタルのデータ伝送を目的として、少なくとも1個の第1の出力接続(Out+)及び少なくとも1個の第2の出力接続(Out−)に接続可能であり、少なくとも1個の電圧源(SQ)、特にドライバ出力段によって供給可能な、少なくとも1個の差動ラインを駆動する回路装置(S;S’;S”;S''')であり、互いに左右対称に配置され、電圧源(SQ)を少なくとも1個の基準電位(GND)、特に接地電位、グラウンド電位又はゼロ電位に接続する、少なくとも2個の経路(P1、P2)を備える回路装置において、また少なくとも1個のそのような回路装置(S;S’;S”;S''')を用いる少なくとも1個の差動ラインを駆動する方法において、スイッチング時の出力インピーダンス(ZOut1、ZOut2)の増加を避け、これにより高信号品質を提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】複数の出力バッファ回路を備える際に、チップレイアウトサイズ、消費電力、LSIのピン数の増加を低減する。

【解決手段】電圧発生回路A3は、出力バッファ回路B1〜B3のそれぞれに対応する基準電圧を発生する。比較回路CP1は、基準電圧とダミーバッファ回路A2の出力電圧とを比較する。カウンタH2は、比較回路CP1における比較結果が一致するまでクロック信号CLKをカウントする。ダミーバッファ回路A2は、カウンタH2のカウント値に基づいて出力バッファ回路B1〜B3のそれぞれに対応する出力インピーダンスを調整する。調整値保持部E11〜E14は、それぞれに対応する基準電圧を元に得られる比較回路CP1の比較結果の一致時におけるカウント値を保持する。出力バッファ回路B1〜B3は、それぞれ保持されたカウント値に基づいてそれぞれ出力インピーダンスを調整する。

(もっと読む)

抵抗調整回路及び半導体集積回路

【課題】本発明は、LSI内部の抵抗値を外部の抵抗素子に基づいて規定範囲内に自動調整することを特徴とする。

【解決手段】半導体集積回路に接続された抵抗素子Rextの抵抗値に応じた値の基準電圧Vrefを発生する基準電圧発生回路10と、制御コード信号Code_OUT[N:0]に応じて抵抗値が調整されるレプリカ抵抗回路12を有し、このレプリカ抵抗回路の抵抗値に応じた値の比較用電圧Vaを発生する比較用電圧発生回路12と、レプリカ抵抗回路と同様に構成され、制御コード信号に応じて抵抗値が調整される本体抵抗回路14と、基準電圧及び比較用電圧をそれぞれの電圧値に応じた周波数を有する信号に変換し、さらに両信号を積分して積分データを生成し、かつ両積分データの差に基づいて前記制御信号を発生する抵抗制御回路11とを半導体集積回路に内蔵したことを特徴とする。

(もっと読む)

入力/出力バッファの動作インピーダンス制御

オフチップ駆動(OCD)及びオンダイ終端(ODT)を実行するシステム及び方法を提供する。該両機能を実施するために、トランジスタを有する共通のプルアップ回路網及びトランジスタを有する共通のプルダウン回路網が用いられる。駆動モードでは、プルアップ回路網は、「オン」出力が生成されるべきとき、較正された駆動インピーダンスを生成するようにされ、プルダウン回路網は、「オフ」出力が生成されるべきとき、較正された駆動インピーダンスを生成するようにされる。終端モードでは、プルアップ回路網及びプルダウン回路網は、較正されたプルアップ抵抗及びプルダウン抵抗をそれぞれ生成し、一緒に分割終端を形成するようにされる。  (もっと読む)

(もっと読む)

LVDSレシーバ

【課題】外部抵抗を用いずに、伝送路のインピーダンスによる信号品質の劣化を最小限に抑えるようにする。

【解決手段】2つの差動入力端子を有し、2つの差動入力端子間に与えられたアナログ差動電圧信号に応じたロジック信号を出力する差動レシーバ部140を設ける。また、2つの差動入力端子間にトランジスタで形成され、LVDSレシーバの外部からオンオフ制御可能な複数個のスイッチを含んだスイッチ部150を設ける。そして、差動レシーバ部140の2つの差動入力端子には、アナログ差動電流信号がスイッチ部150の各スイッチのオン抵抗により電流−電圧変換されたアナログ差動電圧信号を与える。

(もっと読む)

スタック型差動信号送信回路

【課題】チャンネル当たりの電力散逸が減少されており、回路の複雑性が低く、内在的な帯域幅の制限が無く、データ又はクロックのエンコーディング無しで動作可能であり、信号受信器に関しての付加的な条件を課すことなしに動作可能であり、且つEMI及びその他のノイズ源に対しての高いロバストの耐久性を有する差動I/Oインタフェースを有する差動信号送信回路を実現する。

【解決手段】チャンネル間において信号電流を再使用することにより電力散逸を最小化させるために電源電極間においてスタック型関係で複数の差動信号送信回路が結合されている差動信号送信回路。

(もっと読む)

差動伝送回路

【課題】ノイズによる悪影響を回避し、ノイズ耐性が高く良好なアイパターンを伝送できるようにした差動伝送回路を提供する。

【解決手段】送信回路10の送端トランジスタQ11,Q12のエミッタと、受信回路20の終端抵抗R21,R22の片端が接続された入力バッファ21の2個の入力端子との間に、2本の線路31,32で構成される差動伝送線路30を接続して構成した差動伝送回路において、終端抵抗R21,R22の各他端を、共通に、電流源I21を介して電圧端子VG22に接続すると共に、抵抗R23とキャパシタC21の直列回路を介して電圧端子VG23に接続した。

(もっと読む)

回路ブロック間送受信回路を持つ半導体装置

【課題】 半導体基板上のブロック間配線の伝送において、配線抵抗のばらつきによる電流信号の変動を抑えて、安定な信号伝送を実現するブロック間送受信回路を提供する。

【解決手段】 受信回路は相補な電流信号を受ける1対の第1ないし第2の受信端子のそれぞれに接続された第1および第2の定電流源手段と、ソースが一方の第1の受信端子と第1の定電流源手段に、ドレインが第1の出力端子と第1の抵抗手段を介して第1の電源に接続された第1のNMOSトランジスタと、ソースがもう一方の第2の受信端子と第2の定電流源手段に、ドレインが第2の出力端子と第2の抵抗手段を介して第1の電源に接続された第2のNMOSトランジスタとを備え、第2のNMOSトランジスタのゲート電圧を第1の出力端子の電圧信号と同相な電圧信号で、第1のNMOSトランジスタのゲート電圧を第2の出力端子の電圧信号と同相な電圧信号で制御することを特徴としている。

(もっと読む)

出力インピーダンス調節回路を備えた半導体装置及び出力インピーダンスの試験方法

【課題】多様な状況下で変動する出力インピーダンスを簡単な手順で高精度に試験することができる出力インピーダンス調節回路を備えた半導体装置を提供する。

【解決手段】半導体装置の出力インピーダンス調節回路は、並列接続された複数のトランジスタを含む出力回路部15の出力インピーダンスを自動調節するため、出力回路部15と同一の構成の回路部分を含むレプリカ回路部11と、レプリカ回路部11の出力インピーダンスと基準抵抗との大小の比較結果を内部カウンタ制御信号ISp、ISnとして出力する比較部12と、外部カウンタ制御信号ESp、ESnと内部カウンタ制御信号ISp、ISnを選択的に切り替えてカウント動作を行って調節コードCp、Cnを出力するカウンタ制御部13を備え、調節コードCp、Cnが出力回路部15及びレプリカ回路部11に供給され、複数のトランジスタが調節コードCp、Cnに基づき導通制御される。

(もっと読む)

121 - 140 / 285

[ Back to top ]