Fターム[5J056AA40]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 整合 (285)

Fターム[5J056AA40]に分類される特許

161 - 180 / 285

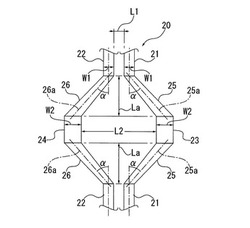

配線基板と画像形成装置

【課題】ドライバ手段が表面実装型の場合であってもドライバ手段の出力を測定することのできる配線基板と画像形成装置とを提供することにある。

【解決手段】絶縁基板上に形成された第1,第2信号線路21,22からなる伝送線路20を備え、絶縁基板上に実装されるドライバ手段から逆位相の2相の信号を第1,第2信号線路21,22を介してレシーバ手段に伝送する配線基板であって、第1,第2信号線路21,22の途中に、前記ドライバ手段の動作を測定するための第1,第2測定パッド部23,24を形成し、この第1,第2測定パッド部23,24は、第1,第2信号線路21,22間の間隔より大きく離間され且つ第1,第2信号線路21,22の線幅より大きい線幅を有し、第1,第2測定パッド部23,24と第1,第2信号線路21,22とを第1,第2接続線路25,26で接続し、第1,第2測定パッド部23,24のインピーダンスと、第1,第2信号線路21,22のインピーダンスとをほぼ同一に設定した。

(もっと読む)

動的伝送路の終端

【課題】ガンニングトランシーバーロジック(GTL)は、信号電波の反射を避けるために、信号路の各端に対称的かつ並列に終端抵抗を用いる。

【解決手段】システムは、伝送路から受信した低レベル信号の検出と、検出された低レベル信号に応答する、終端回路の伝送路からの切断を含んでよい。いくつかの側面においては、次に、ストローブ信号の遷移を検出し、検出した遷移に応答して終端回路を伝送路へと接続する。

(もっと読む)

ドライバ回路

【課題】 従来のドライバ回路では、CML回路の出力振幅や中点電圧等の出力電圧を制御することが困難であった。さらに、従来のドライバ回路では、CML回路における出力電圧のハイレベルが電源電圧からドロップしていた。

【解決手段】 ドライバ回路は、差動入力信号の振幅を変換して差動出力信号を出力する振幅変換部と、前記差動出力信号の振幅を設定する振幅設定部と、前記差動出力信号の振幅の中心値を設定するコモン電圧設定部とを有する。

(もっと読む)

段階的オンダイターミネーションを備えた集積回路

段階的オンダイターミネーションを有する集積回路装置である。この集積回路装置には、データ信号を受信する入力部、ならびに第1および第2の終端回路が含まれる。第1の終端回路には、第1の負荷素子と、第1の負荷素子をデータ信号入力部に切り替え可能に結合する第1のスイッチ素子と、が含まれる。第2の終端回路には、第2の負荷素子と、第2の負荷素子をデータ信号入力部に切り替え可能に結合する第2のスイッチ素子と、が含まれる。  (もっと読む)

(もっと読む)

半導体装置の出力回路及びこれを備える半導体装置

【課題】ODTインピーダンスを動的に変更可能な出力回路において、同期回路とデータピンとの間の回路段数を抑制する。

【解決手段】ODT制御信号ODTaを生成するカウンタ回路152,153,162,163と、ODT機能を有する複数のドライバ回路111〜11nと、カウンタ回路からドライバ回路へ伝達される信号を内部クロックDLLに同期させる同期回路180と、ODT制御信号ODTaに基づいて複数のODT選択信号ODTb,ODTcのいずれか一つを活性化させる第1の選択回路170と、活性化されたODT選択信号に基づいて複数のドライバ回路のうち使用するドライバ回路を選択する第2の選択回路180とを備える。第1の選択回路170はカウンタ回路と同期回路との間に配置され、第2の選択回路180は同期回路とドライバ回路との間に配置されている。

(もっと読む)

半導体装置の出力回路調整方法

【課題】単位バッファを並列に使用することにより出力インピーダンスの切り替えが可能な出力回路のインピーダンス精度を高める。

【解決手段】電源端子VDDQと出力端子DQとの間にそれぞれ接続されたトランジスタ111P〜11nP及び抵抗R1〜Rnと、電源端子VSSQと出力端子DQとの間にそれぞれ接続されたトランジスタ111N〜11nN及び抵抗R1〜Rnをそれぞれ有する単位バッファ111〜11nを備える。単位バッファ111〜11nに含まれるトランジスタのオン抵抗値は互いに実質的に同一であり、単位バッファ111〜11nに含まれる抵抗R1〜Rnの抵抗値は互いに異なる。抵抗R1〜Rnの抵抗値の違いにより、電源抵抗に起因するインピーダンスのずれを相殺することが可能となる。

(もっと読む)

信号伝送回路、CMOS半導体デバイス、及び回路基板

【課題】大規模集積回路内に形成される長い信号線路或いは接続される被駆動回路の数が多数存在する等により形成される静電容量の容量値が大きい信号線路の信号伝送特性を改善する。

【解決手段】駆動回路及び被駆動回路の電源電圧の中点電圧を出力し、出力インピーダンスが低い付加回路を信号線路に接続し、信号線路の電位を電源電圧の中点電圧に維持すると共に、駆動回路から出力される駆動信号を中点電圧(被駆動回路の閾値電圧)を中心に小振幅で励振させ、この小振幅に制限された駆動信号により被駆動回路を駆動させる。

(もっと読む)

基準信号供給装置

【課題】パッケージ内部のクロストークによる基準信号への影響を無くすようにした基準信号供給装置を提供する。

【解決手段】ICパッケージ1と基準信号発生部3との間を、ICパッケージ1の特性インピーダンスに比して低い特性インピーダンスの伝送線路2により接続してICパッケージ1から基準信号発生部3側を見た場合に、見かけ上の電気長が無限大になるようにし、かつICパッケージ1で発生したクロストークによる信号をICパッケージ1内に送り返すようにして、ICパッケージ1内でクロストークによる信号の相殺ループを形成するようにし、また伝送線路2を通過した高周波成分つまり交流成分の信号を伝送線路2と直列に接続した抵抗Rにて吸収するようにしている。

(もっと読む)

キャリブレーション回路

【課題】外部クロックの周波数が高い場合であっても、十分なキャリブレーション動作を実行可能なキャリブレーション回路を提供する。

【解決手段】出力バッファを構成するプルアップ回路と実質的に同じ回路構成を有する第1のレプリカバッファ110と、出力バッファを構成するプルダウンと実質的に同じ回路構成を有する第2のレプリカバッファ120とを備える。第1のキャリブレーションコマンドZQCSが発行されると、制御信号ACT1,ACT2の一方を活性化させることにより、第1及び第2のレプリカバッファ110,120に対するキャリブレーション動作を片方だけ行う。第2のキャリブレーションコマンドZQCLが発行されると、制御信号ACT1,ACT2の両方を活性化させることにより、第1及び第2のレプリカバッファ110,120に対するキャリブレーション動作を両方とも行う。

(もっと読む)

ドライバ回路、ドライバ装置ならびにそれらを用いた電子機器

【課題】出力インピーダンスと、遷移時間を高い自由度で調節する。

【解決手段】ドライバ回路100は、信号伝送ライン5にハイレベルまたはローレベルの出力電圧Voutを印加する。ハイサイドドライバ回路14は、電源ラインLvddとハイサイドトランジスタMHのゲートの間に設けられた第1トランジスタM1と、接地GNDとハイサイドトランジスタMHのゲートの間に直列に設けられた第2トランジスタM2および第1抵抗R1と、を含む。ローサイドドライバ回路16は、電源ラインLvddとローサイドトランジスタMLのゲートの間に直列に設けられた第3トランジスタM3および第2抵抗R2と、接地GNDとローサイドトランジスタMLのゲートの間に設けられた第4トランジスタM4と、を含む。

(もっと読む)

メモリシステムの能動終端抵抗の制御装置及び方法

【課題】メモリモジュールに装着されたDRAMの動作モードにかかわらずDRAMの能動終端抵抗のオン/オフを制御できる能動終端抵抗の制御装置及び方法を提供する。

【解決手段】本発明に係るメモリ回路に装着されたバッファ回路は、信号入力端と、信号入力端に接続された入力端を有する同期入力バッファと、信号入力端に接続された入力端を有する非同期入力バッファと、メモリ回路の動作モードによって同期入力バッファの出力信号または非同期入力バッファの出力信号を選択的に出力するスイッチング回路とを具備する。本発明に係る能動終端抵抗を制御するための装置及び方法は、遅延同期ループまたは位相同期ループの動作モードにかかわらず終端抵抗のオン/オフを制御できるため、データバブルを最小化させることができる。

(もっと読む)

データ入出力ドライバのインピーダンスを調整可能な半導体装置

【課題】制限された時間内にPVTの変動による入力抵抗の変化に対応する終端抵抗を早く設定して供給することのできる半導体メモリ素子のインピーダンス調整回路を提供すること。

【解決手段】このため、本発明は、ZQ抵抗値に対応するノーマル目標範囲を提供し、微小駆動信号に応答して微小目標範囲を出力する基準範囲供給手段と、複数の制御コードに対応する出力抵抗値を供給する終端抵抗値供給手段と、前記出力抵抗値が前記ノーマル目標範囲内に位置するように前記複数の制御コードを生成し、前記微小駆動信号に応答して前記複数のコード信号を調整し、前記出力抵抗値が前記微小目標範囲内に位置するように制御するコード生成手段と、前記出力抵抗値が前記ノーマル目標範囲内に位置するか否かを検出し、前記微小駆動信号を生成するノーマルシフト検出手段とを備える半導体装置を提供する。

(もっと読む)

半導体装置、及びインピーダンス制御方法

【課題】回路面積が縮小されたインピーダンス制御装置を提供できる。

【解決手段】本発明による半導体装置は、制御対象回路10に含まれる第1のトランジスタP1に対応して形成される第1のレプリカトランジスタP2と、第1のトランジスタP1に第1の基板バイアス電圧Vb1を供給し、制御対象回路10におけるインピーダンスを制御する第1の基板バイアス制御回路20とを具備する。第1の基板バイアス電圧Vb1は、第1のレプリカトランジスタP2を介して第1の基板バイアス制御回路20に帰還され、制御対象回路10の出力インピーダンスを制御する。

(もっと読む)

半導体送受信装置システム、メモリカードおよびメモリカードホスト機器

【課題】インピーダンス調整、ドライブ能力調整の柔軟性があり、かつ高速な信号伝送が可能な半導体送受信装置システムを小面積にて得ること。

【解決手段】双方向に信号の送受信を行なう半導体送受信装置システムであって、1つのマスター半導体送受信装置と少なくとも1つのスレーブ半導体送受信装置で構成され、前記マスター半導体送受信装置、前記スレーブ半導体送受信装置ともに信号の送受信を行なうための送信回路と受信回路と、伝送線路とのインピーダンスの整合を図る終端回路を具備し、前記マスター半導体送受信装置のみに信号駆動用の電流源を持たせる構成とした。

(もっと読む)

超低電力アナログ補償回路

本発明は、集積回路内におけるプロセス、電圧及び温度(PVT)の変化のうちの少なくとも一つの変化を補償する補償回路に関する。この補償回路は、低電圧の基準電流源を用いてPVT変化に対して一定である基準電流(Iref)をオンチップ低基準電圧源(VDD)から直接発生させ、PVT変化に従って変化する検出電流(Iz)を、単一のダイオード接続トランジスタ(M10)の両端間に印加された2つの低基準電圧源間の電圧差に対応する低電圧源(VDDE−VDD)から電流コンベアに基づくセンス回路により発生させる。次に、両電流(Iref,Iz)を電流モードアナログ−ディジタル変換器内で比較し、複数のディジタルビットを出力させる。これらのディジタルビットはその後I/Oバッファ内のPVT変化を補償するために使用できる。  (もっと読む)

(もっと読む)

半導体装置

【課題】電源電圧変動に影響されない抵抗特性を持つ抵抗素子及び電源電圧変動に影響されないで所望の出力インピーダンス特性を持つ信号出力回路を備えた半導体装置を提供する。

【解決手段】回路の接地電位点に対応した基準電圧に基づいた定電流を形成する。電源電圧端子に一端が接続された第1抵抗素子に上記定電流を流す。上記第1抵抗素子で形成された電圧を第1差動増幅回路に供給し、その出力電圧を上記電源電圧端子にソースが接続された第1導電型の第1MOSFETのゲートに供給する。この第1MOSFETのドレイン電圧を上記第1差動増幅回路の他方の入力に帰還させる。上記第1MOSFETのドレインと回路の接地電位点との間に第1電流源を設ける。上記電源電圧端子にソースが接続され、上記第1MOSFETとゲートが共通に接続された第1導電型の第2MOSFETと抵抗素子として用いる。

(もっと読む)

デジタル処理装置のクロック分配回路

【課題】多数の半導体デバイスで構成されるデジタル処理装置のクロック分配を矩形波にて行う場合、クロック伝送路間での不整合による反射ノイズ、高周波成分等のスプリアスの輻射が問題となる。

【解決手段】クロック発生源11は一定周波数の正弦波発振信号をクロック信号として発生し、分配回路12で複数の出力端子にそれぞれ分岐して取り出す。インピーダンス変換回路131〜13Nはクロック信号をそれぞれエミッタフォロア形のトランジスタ増幅回路でインピーダンス変換して伝送路側に出力する。波形変換回路151〜15Nは伝送されてくるクロック信号をそれぞれ波形変換してクロック伝送先回路161〜16Nに出力する。

(もっと読む)

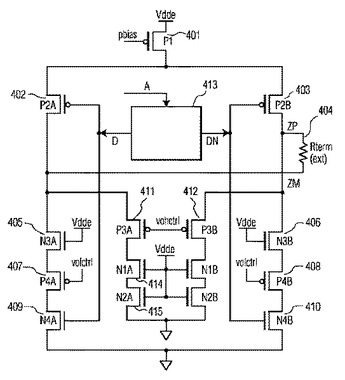

出力インピーダンスを整合した低電圧で低消費電力の差動ドライバ

本発明は、差動データ入力端と、前記差動データ入力端に依存する電流をステアリングするための電流源に結合した複数のスイッチと、少なくとも複数のスイッチのうちの2つと結合している第1の差動出力端および出力インピーダンスを制御するための第2の差動出力端と、前記第1の差動出力端および前記第2の差動出力端に結合される第1のソースフォロワおよび第2のソースフォロワとを具える、差動信号を駆動するためのシステムおよび方法を提供する。このアーキテクチャは、前記ドライバから反射したコモンモード雑音が差動信号になることを防止し、1.62V以下までのLVDSおよびサブLVDS規格の要件を満足する。またこのアーキテクチャは、Gbpsレンジで動作することが可能であり、極めて低い消費電力で高速差動ドライバとなる。  (もっと読む)

(もっと読む)

終端抵抗調整方法、半導体集積回路及び半導体装置

【課題】本発明は、終端抵抗調整方法、半導体集積回路及び半導体装置に関し、半導体装置内の終端抵抗を最適な抵抗値に設定するためのキャリブレーションを正確に行うことを目的とする。

【解決手段】第1のノードと電源電圧及び接地電圧の一方との間に接続された電流源回路と、第1のノードと電源電圧及び接地電圧の他方との間に並列接続可能に設けられた複数の第1の抵抗を備えたモニタ用抵抗部と、第2のノードと前記他方との間に並列接続可能に設けられた複数の第2の抵抗を備えた終端抵抗部と、第1のノードの電圧と基準電圧とを比較して比較結果を出力する比較回路と、キャリブレーションを行う時には、比較結果に基づいてモニタ用抵抗部の第1の抵抗を選択的に並列接続する制御部と、第2のノードに接続された外部端子とを備え、終端抵抗部の抵抗値を制御する時には、制御部は比較結果に基づいて終端抵抗部の第2の抵抗をモニタ用抵抗部の第1の抵抗と同様の構成に選択的に並列接続するように構成する。

(もっと読む)

出力バッファ回路と差動出力バッファ回路並びに伝送方法

【課題】プリエンファシス機能を有する出力バッファ回路の出力インピーダンスを、調整可能なプリエンファシス量とプリエンファシスタップ数、及び動作タイミングに依らず一定で、伝送線路の特性インピーダンスと整合して出力バッファの出力端子で再反射することなく、高速動作可能な出力バッファ回路を提供する。

【解決手段】インバータ1〜3と、一定の時間遅延させる遅延回路1〜3と、バッファ1〜3とを備え、伝送径路に論理信号を送信し、伝送径路の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路で、プリエンファシス量を可変とし、バッファのオン抵抗Rsを一定とする。バッファの前段にセクレタ回路1〜3を有し、インバータは、セレクタ論理によりバッファに入力する信号を選択可能で、データ信号を反転し、セレクタ論理のセレクト信号により、プリエンファシス量とプリエンファシスタップ数を調整する。

(もっと読む)

161 - 180 / 285

[ Back to top ]