Fターム[5J056AA40]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 整合 (285)

Fターム[5J056AA40]に分類される特許

81 - 100 / 285

インピーダンス調整回路

【課題】回路規模が大きい。

【解決手段】本発明は、外付け抵抗器が接続される外部端子と、前記外部端子と第1の電源端子間に並列に接続され、第1の制御信号に応じてインピーダンスを調整することで前記外部端子の電圧を変化させる第1導電型の第1のトランジスタアレイと、前記外部端子と第2の電源端子間に並列に接続され、第2の制御信号に応じてインピーダンスを調整することで前記外部端子の電圧を変化させる第2導電型の第2のトランジスタアレイと、前記外部端子の電圧と基準電圧を比較した結果に応じて、前記第1の制御信号を設定し、前記第1の制御信号の設定する期間と異なる期間に前記第2の制御信号を設定する制御回路と、を有するインピーダンス調整回路である。

(もっと読む)

半導体装置

【課題】出力バッファのインピーダンス調整期間を測定できる半導体装置を提供する。

【解決手段】コマンドラッチ回路2Aは、外部からのコマンド信号(ZQコマンド)に応じて、ZQEnable信号を発生する。ZQ調整回路3は、ZQEnable信号が入力されると、内部に設けられたレプリカ回路のインピーダンス調整を行い、この結果をドライバコードとしてDQ回路4へ出力する。コマンドラッチ回路2Aは、テストモード信号が入力されると、DQ回路4を介してZQEnable信号に同期したDQ信号を半導体装置100の外部へ出力させる。

(もっと読む)

出力回路、及びそれを用いた車載用通信システム

【課題】回路面積が小さく、製造バラツキによる出力特性の劣化を修正できる出力回路を提供することにある。

【解決手段】本発明による出力回路は、差動入力信号DIに応じた差動出力信号BP、BNを出力端子対31、32から出力するメインバッファ回路1と、制御信号CSに応じて出力端子対31、32のインピーダンスを調整するトリミング回路2とを具備する。トリミング回路2は、第1電源VDDと出力端子対31、32との間に、メインバッファ回路1内の第1トランジスタ対MP1、MP2及び第1抵抗対R1、R2に対して並列に接続された少なくとも1つの第2トランジスタ対MP11、MP21を備える。

(もっと読む)

I/Oセルの出力回路

【課題】終端抵抗若しくはダンピング抵抗として機能する抵抗を備えた出力バッファ回路の出力特性と面積効率を向上させる。

【解決手段】出力トランジスタT11,T12の出力ノードを配線L1〜L5及び抵抗R11,R12を介してパッド11に接続した出力回路において、抵抗R11,R12の両側に出力トランジスタを形成する複数の領域12,13を相対向するようにレイアウトし、領域12,13の外側にパッド11をレイアウトした。

(もっと読む)

電磁干渉の測定および制御のための方法および電子システム

【課題】電気的にアクティブな被変調終端を用いて共振金属下部構造が放射する電磁ノイズを制御するための方法およびシステムを提供する。

【解決手段】電気的にアクティブな被変調終端を実施することによって、電子デバイスの平均EMR放射を低減することができる。例えば、インピーダンスを2つの金属下部構造間で1つ以上の終端位置において連続的に変動させることで、EMRの各成分の振幅に同様の変動を生じさせることができる。1つの手法によれば、EMRを測定する時間間隔未満の周期で電気インピーダンスを周期的に変動させることの結果として、平均測定EMRを低減させる。

(もっと読む)

半導体回路、半導体回路の出力バッファ波形調整方法

【課題】調整回路を変更することなく出力バッファの波形の調整幅を広くすることができる半導体回路および、調整回路を変更することなく出力バッファのインピーダンス調整幅を拡大することができる半導体回路の出力インピーダンス調整方法並びに、調整回路を変更することなく出力バッファのスルーレート調整幅を拡大することができる半導体回路のスルーレート調整方法を提供する。

【解決手段】出力バッファ2のバッファ回路の並列数を調整する出力インピーダンス調整回路3の後段にNch出力バッファオフセット設定回路8とPch出力バッファオフセット設定回路9とを設けて、出力インピーダンス調整回路3が調整した並列数にNch出力バッファオフセット設定回路8とPch出力バッファオフセット設定回路9でオフセット値を加算する。

(もっと読む)

終端抵抗装置、半導体装置、及び終端抵抗の制御方法

【課題】終端抵抗を設定する際に伝送路に発生するノイズを低減することができる。

【解決手段】

本発明に係る終端抵抗装置の一態様は、互いに等しい抵抗値を有し、伝送路1001に接続可能に設けられた複数の第1終端抵抗素子12N、Pを有する可変終端抵抗部10と、可変終端抵抗部10にサーモメータコードからなる第1制御信号NDRV、PDRVを出力することで、伝送路1001に接続する第1終端抵抗素子12N、Pを選択する終端抵抗制御部11と、を備えたことを特徴とする。

(もっと読む)

配線板の接地構造

【課題】 通信用の配線板からの不要電磁波放射を低減できる構造を得る。

【解決手段】 第1の接地面11と、この第1の接地面11と同一面上において絶縁された第2の接地面12とを設けてなる回路基板1と、回路基板1に実装され第1の接地面11に接続するとともに、通信用端子を設けてなる演算手段2と、回路基板1に実装され第2の接地面12に接続するリアクタンス素子3と、演算手段2の通信用端子と接続され通信信号を送受信する第1の配線41と、リアクタンス素子3を介して第2の接地面12と接続される第2の配線42とを設けてなる可撓性のフレキシブルプリント配線板(配線板4)と、を備えてなる。

(もっと読む)

伝送回路、CMOS半導体デバイス、及び設計方法

【課題】クロック信号の遅延量を低減する。

【解決手段】予め定められた最小パルス時間以上のパルス時間を有する差動信号を伝送する伝送回路であって、2本の伝送線の電位差として、差動信号を送出する駆動部102aと、2本の伝送線の電位差により差動信号を受け取ることにより、差動信号に基づいて動作する被駆動部102bと、2本の伝送線を電気的に接続する接続抵抗104とを備える。また、接続MOSトランジスタは、被駆動部の受信端の近傍に設けられてよい。

(もっと読む)

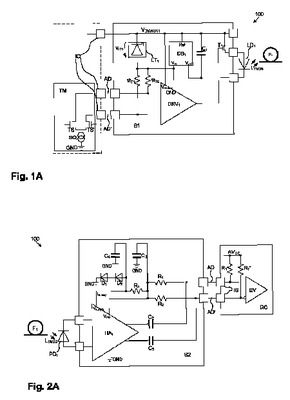

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

内蔵型低電圧差動信号インターフェース付の高速ディジタル・ガルヴァニック・アイソレータ

【課題】 様々な種類の高速ディジタル・ガルヴァニック・アイソレータ及びそれに対応する集積化低電圧差動信号(「LVDS」)インターフェースを提供する。

【解決手段】 幾つかの実施形態によれば、ファントム電力が、ガルヴァニック・アイソレータの一方の側にアイソレータの他方の側から、2つの側を相互接続するシールドが付いたツイストペア・ケーブルを介して与えられるため、電力を別の電源を通して、又はアイソレータの両側に向けられて 接続された別個の物理的な配線によって、ガルヴァニック・アイソレータの両側に与える必要性が取り除かれる。そのようなファントム電源の構成により、コストが削減され、電力消費が低下され、またノイズ・レベルが低い高速シリアルデータ通信が必要な装置の中で利用できる工学設計の選択肢の数が増加される。

(もっと読む)

終端回路

【課題】 1個の終端抵抗を用いて、伝送路の不整合を起こすことなく、上位デバイスと下位デバイスを1:2接続することを可能とする終端回路を実現する。

【解決手段】 所定の特性インピーダンスを有する第1デバイスの出力より第1リードを介して接続される、前記特性インピーダンスと同値の終端抵抗と、前記特性インピーダンスと同値の特性インピーダンスを有する第2デバイス及び第3デバイスの各入力と前記終端抵抗間を接続する、等長の第2リード及び第3リードと、を備える。

(もっと読む)

信号伝送システム評価装置、信号伝送システム評価プログラム、信号伝送システム設計方法

【課題】信号伝送システムにおけるコネクタクロストークの算出を高速化する信号伝送システム評価装置、信号伝送システム評価プログラム、信号伝送システム設計方法を提供する。

【解決手段】第1伝送路に対する第2伝送路の位置関係により分類される種別と、第2伝送路から第1伝送路へ与えられるクロストークの大きさの比率であるクロストーク率とを、第2伝送路のピン毎に取得するパラメータ取得部と、種別及びクロストーク率に基づいて、種別毎のクロストークの占有率を算出する占有率算出部と、占有率に基づいて第2伝送路における雑音源出力を算出する雑音源出力算出部と、占有率に基づいて第1伝送路損失を及び第2伝送路損失を算出する損失算出部と、雑音源出力と第1伝送路損失及び第2伝送路損失とに基づいて、第1伝送路の受信雑音量を算出する受信雑音算出部とを備えた。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】チップ面積の大幅な増大をもたらすことなく、出力バッファのスルーレートを自動的に調整する。

【解決手段】インピーダンス調整信号ZQP,ZQNに基づいてインピーダンスを調整可能な出力バッファ100と、インピーダンス調整信号ZQP,ZQNに基づいて出力バッファ100のスルーレートを調整するスルーレート制御回路400とを備える。スルーレート制御回路400は、インピーダンス調整信号ZQP,ZQNが相対的に低いインピーダンスを指定している場合にはスルーレートを相対的に高く設定し、インピーダンス調整信号がZQP,ZQN相対的に高いインピーダンスを指定している場合にはスルーレートを相対的に低く設定する。これにより、スルーレートを測定するための専用回路が不要となる。

(もっと読む)

出力回路

【課題】より精度よく外部インピーダンスとの整合をとることができる半導体集積回路の出力回路を提供する。

【解決手段】出力回路は、トランジスタN00〜N7を含むトランジスタ回路が出力端子3に複数段並列に接続されてなり、各トランジスタ回路に含まれるトランジスタのゲートへの入力信号G0〜G7により出力インピーダンスの調整が可能な出力回路であって、複数段のトランジスタ回路に含まれる、少なくとも2段のトランジスタ回路のインピーダンスを互いに異ならせる。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】インピーダンスコードを更新して出力インピーダンスの調整を行う際、インピーダンスコードの更新に影響されない安定した出力を得ることが可能な出力バッファ回路及び半導体装置を提供すること。

【解決手段】pチャネルMOSFET及びnチャネルMOSFETを備える複数のドライバ回路が並列に接続されたバッファ部を備え、ドライバ回路の動作数により出力インピーダンスを調整するためのインピーダンスコードが供給される出力バッファ回路において、ドライバ回路のドライブ状態を示す状態情報信号に応じて、システムクロックに同期して、pチャネルMOSFET及びnチャネルMOSFETに対してインピーダンスコードを更新するコード更新制御回路を備える構成とする。

(もっと読む)

ディジタル回路システム

【課題】電磁気学に忠実でありながら設計が容易で電磁適合性に優れ、高い性能を有するディジタル回路システムを提供する。

【解決手段】 損失線路部品42および低インピーダンス損失線路部品52は印刷配線基板47に搭載され、損失線路部品42の信号端子43、46はビア51によって信号配線49に直列に挿入され、低インピーダンス損失線路部品52の電源端子53,56はビア51によって電源配線50に直列に挿入されている。損失線路部品42および低インピーダンス損失線路部品52のグランド端子44,45,54,55は、ビア51によってグランドプレーン49に並列に接続されている。また、損失線路部品42および低インピーダンス損失線路部品52は、印刷配線基板47上のMPU39の近傍に搭載され最短の長さの配線で接続される。これにより、電磁干渉が少なく高い性能を有するディジタル回路システムが実現できる。

(もっと読む)

ターミネーション抵抗回路

【課題】回路の面積を増大させることなく、高い分解能及び広い抵抗値の範囲を有するターミネーション抵抗回路を提供すること。

【解決手段】本発明に係るターミネーション抵抗回路は、キャリブレーションコードが所定値を有すると、論理値が、前記キャリブレーションコードが前記所定値と異なる値を有する場合の論理値から変化する制御信号を生成する制御信号生成部と、前記キャリブレーションコードに応答してそれぞれオン/オフされる、相互に並列接続された複数の並列抵抗と、前記制御信号に応答してターミネーション抵抗回路全体の抵抗値を変更する抵抗値変更手段とを備える。

(もっと読む)

容量結合クロストークの相殺

本開示は、容量結合回路を使用することによりインダクタンスに支配されたクロストークを相殺する方法を提示する。本開示はまた、各ビクティム信号に各アグレッサ信号の微係数を加算し、これにより所与の受信機がそうでなければ見るクロストークを打ち消すように、結合用に使用される容量値を校正、選択、およびプログラムする方法を提示する。多線バスの関連では、クロスカップリング回路が、特定の送受信機ペア毎に校正され使用された値でもって、「最近傍」の各ペア間で使用されてよい。例えば差動シグナリングシステムでの使用のために、最近傍でない線間で誘起されるクロストークに対処する実施形態もまた提示される。 (もっと読む)

電子機器、及び電子機器における切換制御方法

【課題】複数種のどの周波数でも最適化された状態で信号を伝送することを可能した電子機器、及び電子機器における切換制御方法を提供する。

【解決手段】本願は、複数の電子部品と、前記電子部品に接続され信号が伝送される伝送線路と、前記伝送線路においてインピーダンスマッチングを行うためのマッチング回路と、前記伝送線路のインピーダンスが、何れかの前記電子部品に入力される信号の周波数に応じた値になるように、前記マッチング回路の回路構成を切り換える制御を行う切換制御手段と、を備える。

(もっと読む)

81 - 100 / 285

[ Back to top ]