Fターム[5J056CC03]の内容

Fターム[5J056CC03]の下位に属するFターム

基準電位(定電位)発生回路 (414)

Fターム[5J056CC03]に分類される特許

81 - 100 / 301

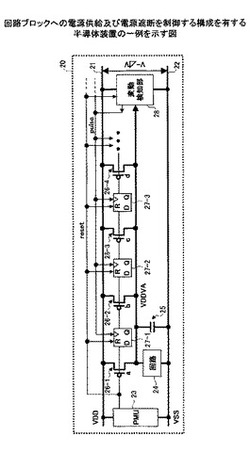

半導体装置及び半導体装置の電源制御方法

【課題】1つの回路ブロックに対して設けた複数の電源スイッチを順次オンさせていく構成において、スイッチオンのタイミングを適切に制御可能な半導体装置を提供する。

【解決手段】半導体装置は、内部回路と、内部回路へ電流を供給する複数の並列な経路にそれぞれ設けられ、導通状態又は非導通状態に制御される複数の電源スイッチと、内部回路への電源を遮断する指示又は電源を供給する指示を行なう命令部と、内部回路に電源スイッチを介して供給される電流が定常状態であるか否かを検知して検知結果を出力する変動検知部と、命令部の電源供給指示に応答して、複数の電源スイッチを順次導通状態にして内部回路への電流供給量を増やしていく際に、複数の電源スイッチを導通させるタイミングを検知結果に応じて制御する論理回路とを含む。

(もっと読む)

半導体集積回路装置

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

【解決手段】電源遮断時のデータ保持のための電源線は一般の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。そのために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。[効果]セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

(もっと読む)

半導体装置

【課題】デカップリング容量セルを用いて電源配線の電圧変動を抑制し、かつ、電源配線の電源共振を防ぐ半導体装置を提供する。

【解決手段】半導体チップ100に複数配置されたデカップリング容量セルを、トランジスタ素子及び容量素子の直列回路で構成する。制御回路CTRCにおいては、半導体チップ100を動作させる基準クロック又はそこから生成される高周波数のクロックが入力され、そのクロックに同期した制御信号CTRLを生成し、デカップリング容量セルの電源配線VDDへの容量素子の接続/非接続を行う。

(もっと読む)

半導体集積回路

【課題】論理ゲートを構成するトランジスタの特性劣化を抑制する。

【解決手段】半導体集積回路70には、マルチプレクサ1、信号発生回路2、制御回路3、m個のインバータINV1乃至m列、n個の2入力NOR回路NOR1乃至n、縦続接続されるn個の2シフトレジスタSR1乃至nが設けられる。制御回路3は、クロック信号が供給される通常動作ときにディセーブル状態の制御信号Sctを生成し、クロック信号が供給されない通常動作以外のときにイネーブル状態の制御信号Sctを生成する。マルチプレクサ1は、クロック信号Sclkと信号発生器2から出力される低周波信号Ssgが入力され、制御信号Sctがディセーブル状態の時インバータINV1乃至m列にクロック信号Sclkを供給し、制御信号Sctがイネーブル状態の時インバータINV1乃至m列に低周波信号Ssgを供給する。

(もっと読む)

半導体集積回路

【課題】電源線のレイアウト面積を広げることなく、コア回路とバイアス供給回路との間

の電圧降下を抑え、かつ、コア回路間の高速信号ノードを短縮できるようにする。

【解決手段】Si基板11にトランジスタQ及び抵抗素子Rを有して高電位側の電源線と

低電位側の配線D1とバイアス供給用の配線D2とに接続されてトランジスタ動作をする

コア回路1と、Si基板11に設けられてコア回路1にバイアスを供給するバイアス供給

回路とを備え、コア回路1の中の定電流源用のトランジスタQに、その一端が接続された

抵抗素子Rの他端がバイアス供給用の配線D2に接続され、この配線D2が接続された抵

抗素子Rの他端がコンタクトホール35を介してバイアス供給用の配線D2よりも上層の

低電位側の配線D1に接続されるものである。

(もっと読む)

半導体集積回路装置

【課題】電源電圧を制御する回路ブロックを流用する場合に貫通電流を防止するインターフェースの再設計の手間を緩和する。

【解決手段】第1チップ(CHP1)は、第1及び第2ノード、電源電圧が供給される第1回路ブロック、第3と第2ノード間にソース・ドレイン経路を有する第1MOSトランジスタ、そのオン/オフを制御する第1制御回路、及び電源電圧と共に第1回路ブロックの出力が入力される第1変換回路を備える。第2チップ(CHP2)は、第4及び第5ノード、電源電圧と共に第1変換回路の出力が入力される第2変換回路を備える。第1制御回路は、第1MOSトランジスタがオンの場合、第1状態の第1制御信号を第1変換回路に出力し、第1変換回路は第1回路ブロックの信号を第2変換回路に出力する。第1MOSトランジスタがオフの場合、第2状態の第1制御信号を第1変換回路に出力し、第1変換回路はその出力を第1又は第2ノードの電位に制御する。

(もっと読む)

半導体集積回路

【課題】常時電源オン回路領域の電源が先に遮断されても電源オフ回路領域に悪影響を及ぼすことを防止する半導体集積回路を提供する。

【解決手段】第1電源から電力供給される回路領域である電源オンドメインと、第2電源から電力供給される回路領域である電源オフドメインとを同一チップ上に備え、電源オンドメインは、第1電源がオンかつ第2電源がオフであるときに電源オフドメインと電源オンドメインとの間で入出力される信号を遮断する第1信号遮断部と、第2信号遮断部の遮断を有効または無効にする旨を示す第1制御信号を出力する遮断制御部とを備え、電源オフドメインは、遮断制御部からの遮断を有効にする旨を示す第1制御信号に基づき、電源オンドメインと電源オフドメインとの間で入力される信号を遮断する第2信号遮断部を備え、前記遮断制御部は、第1電源からの電源供給の停止を検出したとき、遮断を有効にする旨を示す第1制御信号を出力する。

(もっと読む)

スイッチング制御回路

【課題】同時スイッチングノイズを低減するスイッチング制御回路を提供する。

【解決手段】本発明のスイッチング制御回路は、入力端子1、出力端子2及びスイッチング素子を有する出力回路10と、出力回路10のスイッチング素子の制御端子に接続され、出力回路10の出力信号が変化する期間において、入力信号を制御する第1の回路20と、第1の回路20の制御端子に接続され、出力回路10の出力信号が変化する期間において、第1の回路20に流れる電流を制御する制御信号を生成する第2の回路30と、を備えている。

(もっと読む)

半導体集積装置

【課題】複数の電源スイッチを個別に制御する制御回路を設けることなく、電源遮断領域の電源を復帰させる際、電源電圧の降下を可及的に低減する。

【解決手段】電源線VDDに接続された複数のパワーグループPG1〜PGnを有する、パワードメインPDと、

一端が仮想接地線VVSSを介して各パワーグループPG1〜PGnに接続され、他端が接地線VSSに接続され、制御端子に入力される共通の制御信号ENBによりオン/オフ制御される、複数の電源スイッチSW1〜SWnと、

複数の電源スイッチSW1〜SWnごとに設けられた、制御信号ENBを遅延させる複数の遅延素子C1〜Cnと、

を備える半導体集積回路であって、各遅延素子C1〜Cnの遅延量を少なくとも2種類にすることで、各パワーグループを流れるラッシュカレントのピークを時間的に分散させる。

(もっと読む)

複合電子回路アセンブリ

複合電子回路アセンブリは、パッケージ内で重ね合わされた2つのMOS又はCMOS回路ダイ(100、200)を備える。回路アセンブリの異なるモジュールは、前記モジュールのデジタル、アナログ又はハイブリッドの特性に基づいて2つのダイに分散配置される。そのような分散配置により、回路アセンブリのデジタルモジュールを一方のダイに集め且つアナログ又はハイブリッドモジュールを他方のダイに集めることができる。従って、回路アセンブリの生産コスト、開発時間及び消費電気エネルギーが縮小されてもよい。 (もっと読む)

集積半導体回路

【課題】ダミーゲートアレイのPN貫通電流による短絡現象により、本来の集積半導体回路構成の不良率に不良率が上乗せされるので、本来の集積半導体回路構成の不良率より高い不良率となっていまい、本来の回路の収率より集積半導体回路全体の収率が下がっていたので、本来の回路が正常であれば、ダミーゲートアレイに不良があってもそのダミーゲートアレイさえ使わなければ正常動作する集積半導体回路を提供する。

【解決手段】メタル層で配線がなされるとともにダミーゲートアレイを有する集積半導体回路において、ダミーゲートアレイの電源回路にスイッチング素子を設けたことを特徴とする集積半導体回路を提供する。

(もっと読む)

半導体集積回路装置

【課題】低コスト化が可能な電源遮断スイッチを有する半導体集積回路装置を提供する。

【解決手段】半導体基板10上に形成された回路ブロック11及び回路ブロック13と、選択的に電源供給及び電源非供給を切り替える電源遮断スイッチ16の一端が回路ブロック11、12のブロック電源線21と接続され、電源遮断スイッチ16の他端が個々に区別された電源パッド26に接続された複数の独立電源配線17と、少なくとも回路ブロック13を囲んで配置された少なくとも一部が環状をなす内部共通電源線25を有し、内部共通電源線25を経由した一端が回路ブロック13と接続され、内部共通電源線25を経由した他端が電源パッド26に接続された共通電源配線18とを備える。

(もっと読む)

ラッチ装置及びラッチ方法

【課題】本発明は、ラッチと電源電圧の急激な変動が同時に発生しても、ラッチ結果が不安定になることを防止する、ラッチ装置の提供を目的とする。

【解決手段】電源配線に接続された整流素子と、前記整流素子の順方向側に接続されたキャパシタと、前記キャパシタのキャパシタ電圧で動作し、第1のラッチ信号に従って、入力データをラッチする第1のラッチ回路と、前記第1のラッチ信号よりも遅延した第2のラッチ信号をローパスフィルタに通すことにより生成された第3のラッチ信号を出力するフィルタ回路と、前記電源配線の電源電圧の低下が検出されることにより前記第2のラッチ信号を無効化する無効化回路と、前記キャパシタ電圧で動作し、前記第3のラッチ信号に従って、前記第1のラッチ回路の出力データをラッチする第2のラッチ回路とを備える、ラッチ装置。

(もっと読む)

半導体装置

【課題】オフリーク電流の温度特性が互いに異なる複数の回路ブロックに対して電源制御を行うことにより、消費電力を低減する。

【解決手段】オフリーク電流が第1の温度特性を有するトランジスタによって構成された第1のXデコーダ12と、オフリーク電流が第2の温度特性を有するトランジスタによって構成されたプリデコーダ13及び周辺回路14と、スタンバイ時において温度が第1のしきい値を超えている場合、Xデコーダ12を非活性化させる電源制御回路16と、スタンバイ時において温度が第2のしきい値を超えている場合、プリデコーダ13及び周辺回路14を非活性化させる電源制御回路17とを備える。本発明によれば、複数の回路ブロックに対する電源制御の有無を、互いに異なる温度を基準として判断していることから、各回路ブロックに対して最適な電源制御を行うことが可能となる。

(もっと読む)

半導体集積回路装置

【課題】電源スイッチによる電源遮断技術とDVFSによる低消費電力化技術とを共存可能にし、効率的な消費電力の低減を実現する。

【解決手段】電源VDDが供給される電源スイッチ部7、該電源スイッチ部7による電源遮断が行われる回路ブロック2、およびレベルシフタ13と、電源VDD2が供給される電源スイッチ部8、該電源スイッチ部8による電源遮断が行われる回路ブロック3、およびレベルシフタ14とは、異なるDEEP−NWELL領域19,20にそれぞれ形成されており、これにより、DEEP−NWELLを介しての異なる電源間でのショートを防止する。

(もっと読む)

信号レベル変換回路

【課題】電源電圧の制限を受けずに入出力に信号を加えることを可能にする。

【解決手段】双方向タイプの信号レベル変換回路50には、第1のレベルシフタLS1、第2のレベルシフタLS2、第3のレベルシフタLS3、第nのレベルシフタLSn、入出力端子PIO1、入出力端子PIO2、入出力端子PIO3、及び入出力端子PIOnが設けられる。第1のレベルシフタLS1の共通電源系部11b、第2のレベルシフタLS2の共通電源系部12b、第3のレベルシフタLS3の共通電源系部13b、及び第nのレベルシフタLSnの共通電源系部1nbは、信号レベル変換回路50の内部側にそれぞれ設けられ、高電位電源VCCXが供給される。高電位電源VCCXの電圧は、入力端子側のレベルシフタの第1の電源系部11a、第2の電源系部12a、第3の電源系部13a、及び第nの電源系部1naに供給される高電位側電源電圧よりも低く設定される。

(もっと読む)

半導体集積回路

【課題】半導体集積回路そのもののパフォーマンスを維持しつつその消費電流を低く抑えることができるようにする。

【解決手段】クロック伝達系回路11への電源電圧の供給経路をなす高電位側電源線21は電圧源VDD_Cの正極と接続され、非クロック伝達系回路12への電源電圧の供給経路をなす高電位側電源線22は電圧源VDDの正極と接続され、クロック伝達系回路11および非クロック伝達系回路12への電源電圧の供給経路をなす低電位側電源線25は電圧源VDD_Cおよび電圧源VDDの負極と共通接続される。また、高電位側電源幹線21を介してクロック伝達系回路11に供給する電源電圧を、高電位側電源幹線22を介して非クロック伝達系回路12へ供給する電源電圧よりも低くする。

(もっと読む)

半導体集積回路装置

【課題】従来のパワースイッチと比較して、高速動作を行う活性状態と、内部論理状態は保持しているが低リーク状態である非活性状態を実現し、その二つの状態間の遷移を高速かつ低雑音かつ低電力を実現する。

【解決手段】第1の外部電源電圧(VDD)を与える第1電源線と第2の外部電源電圧(VSS)を与える第2電源線間に、複数の回路からなる内部回路ブロックと電源電圧を制御するパワー制御回路を具備し、制御回路は出力MOSFET(MPP)を具備し、出力MOSFETはゲートとソースが等電圧であっても一定のオフ電流が流れるものであって、出力MOSFET(MPP)の閾値電圧は、内部回路MOSFETのそれよりも小さい。

(もっと読む)

半導体装置

【課題】スタンバイ時の電流消費をより低減する。

【解決手段】機能回路13a、13bと、電源電位Vxを機能回路に供給するか否かを制御するPMOSトランジスタMP1、MP2と、電源電位GNDを機能回路に供給するか否かを制御するNMOSトランジスタMN1、MN2と、第3の電源電位が供給される外部端子VDD2と、第3の電源電位よりも高い電位レベルの第4の電源電位が供給される外部端子VDD1と、PMOSトランジスタMP1、MP2の導通状態及び非導通状態を制御するように、第4の電源電位を振幅とする制御信号CONT1をPMOSトランジスタMP1、MP2に供給すると共に、NMOSトランジスタMN1、MN2の導通状態及び非導通状態を制御するように、第3の電源電位を振幅とする制御信号CONT2をNMOSトランジスタMN1、MN2に供給する電源制御回路12と、を備える。

(もっと読む)

半導体装置及びそのスイッチトランジスタの制御方法

【課題】従来の半導体装置では、電源スイッチ回路の回路規模が大きくなる問題があった。

【解決手段】本発明にかかる半導体装置は、グローバル電源配線とローカル電源配線との導通状態を制御信号に応じて制御するスイッチトランジスタと、制御信号を遅延させて後段に接続されるスイッチトランジスタに伝達する遅延回路と、を備える複数のスイッチセルを有する半導体装置であって、外部から制御信号を受け、直列に接続された遅延回路により制御信号を伝達し、スイッチトランジスタを順次導通させるチェーン部と、チェーン部の最終段に配置されるスイッチセルを介して制御信号が与えられ、並列に接続された遅延回路により制御信号を複数の系列に分配し、分配された制御信号によりスイッチトランジスタを並列して導通させるツリー部と、を有する。

(もっと読む)

81 - 100 / 301

[ Back to top ]