Fターム[5J056CC03]の内容

Fターム[5J056CC03]の下位に属するFターム

基準電位(定電位)発生回路 (414)

Fターム[5J056CC03]に分類される特許

101 - 120 / 301

半導体装置、出力回路、及び、半導体装置における入出力バッファ回路の制御方法

【課題】異なる電源電圧で使用されることが考えられる半導体装置において、好適な出力回路を有する半導体装置を提供する。

【解決手段】少なくとも出力端子の機能を有する信号端子と、電源端子と、電源端子から電源電圧が供給され内部出力信号を受けて信号端子を駆動する第一及び第二の出力バッファ回路を備えた出力回路と、電源電圧を判定し出力回路の動作を制御する電源電圧判定回路と、を備え、電源電圧判定回路が、第1の電位にあると判定したときには、第1の出力バッファ回路を活性化させると共に、第2の出力バッファ回路を非活性化させ、第2の電位にあると判定したときには、前記第1、第2の出力バッファ回路を共に活性化させる。

(もっと読む)

接触式集積回路カード読み取り機の電源インターフェース回路

本発明は、接触式ICカードに電源を供給する電源インターフェース回路を具現するにあたって、さらに簡単な構成で且つ安定して電源を供給することができる技術に関する。本発明による電源インターフェース回路は、外部から供給される電源制御信号を反転及び増幅して出力する電源制御部と、前記電源制御部の出力信号によって相補型トランジスタ部の接地端子側トランジスタのオン/オフ動作を制御するスイッチングダイオード部と、前記電源制御部から直接入力される制御信号と前記スイッチングダイオード部を介して入力される制御信号によって相補型トランジスタが互いに相反する動作を行いながら電源端子電圧を電源出力部側に伝達するか、または当該電源出力部のカード電源端子を接地電圧のレベルにミューティングさせる相補型トランジスタ部と、前記相補型トランジスタ部の動作によって、当該相補型トランジスタ部を介して入力される電圧をICカードのカード電源端子に出力するか、またはカード電源端子を接地電圧のレベルに維持する電源出力部と、を備えて構成されることを特徴とする。 (もっと読む)

半導体集積回路装置

【課題】低消費電力化構造における回路レイアウト面積を大幅に増加させることなく、きめ細かな低電圧制御を行う。

【解決手段】領域21 を低速モードに移行させたい場合、システムコントローラ14は、電源スイッチコントローラ6、および低電力駆動回路9に、リクエスト信号REQ、イネーブル信号EN1をそれぞれ出力し、電源スイッチ部をOFFとし、かつ仮想基準電位VSSM1の電圧レベルが約0.2V〜約0.3V程度となるように制御を行う。これにより、領域21 は、電源電圧VDDと仮想基準電位VSSM1との間の電圧で動作が行われることになるので、低速モードとして制御される。

(もっと読む)

回路に対する内部電荷の移動

【課題】デジタル回路などの回路に対し、スリープ・モードと通常モードとの間での高速な移行を可能にする。

【解決手段】本発明は、チップ内部の電荷の移動操作を利用して回路を高速でスリープに入らせる。本発明は、外部電力の必要性を低減し、回路内の電荷の移動を制御することによってスリープ・モードへの移行を迅速化する。高速スリープおよび高速再起動は、システムのより効率的な電力管理を可能にする。また、この機能は、電力あたりのパフォーマンスを最大化し、よりエネルギ効率のよいコンピューティング・アーキテクチャを提供する。

(もっと読む)

電子回路および電圧検出回路

【課題】回路の動作電圧より低い電圧を用いた場合であっても出力が不定になるのを防止でき、チップ面積を小さくできコスト低減ができる電子回路を提供。

【解決手段】インバータ22の入力がゲートに接続されたデプレッション型Pchトランジスタ32と、インバータ22の出力がゲートに接続されたデプレッション型Nchトランジスタ31を設け、デプレッション型Nchトランジスタ31のソースをデプレッション型Pchトランジスタ32のソースに接続し、デプレッション型Pchトランジスタ32のドレインを第二の端子2に接続し、デプレッション型Nchトランジスタ31のドレインを第三の端子(出力端子)102が接続する。電源4の電圧が低下してインバータ22を構成するエンハンスメント型Pchトランジスタ51とエンハンスメント型Nchトランジスタ52が動作できなくなっても回路の出力102をLレベルとすることができる。

(もっと読む)

半導体集積回路と電源制御方法

【課題】電源回路の立ち上がり時間を予め規定しなくても、必要な回路モジュールに電源を供給して消費電力を低下させることのできる半導体集積回路と電源制御方法を提供すること。

【解決手段】本発明にかかる半導体集積回路は、半導体集積回路の主電源から電源分離された回路モジュールに対して電源供給を行う電源と、回路モジュールからの出力信号の出力を制御する出力制御回路と、電源による電源供給及び出力制御回路を制御するシーケンス制御回路を備え、電源から回路モジュールに対して電源供給を開始する場合に、シーケンス制御回路から出力された電源制御信号に応じて、電源から回路モジュールに対する電源供給を開始するとともに、この電源供給開始時以降にシーケンス制御回路に対して第1のフィードバック信号を出力し、シーケンス制御回路は、第1のフィードバック信号に応じて制御信号を出力制御回路に対して出力するものである。

(もっと読む)

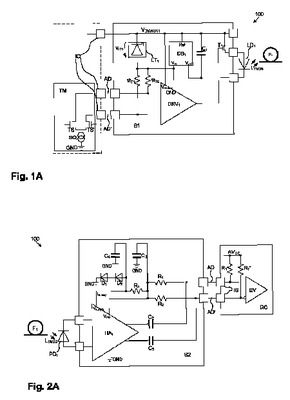

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

内蔵型低電圧差動信号インターフェース付の高速ディジタル・ガルヴァニック・アイソレータ

【課題】 様々な種類の高速ディジタル・ガルヴァニック・アイソレータ及びそれに対応する集積化低電圧差動信号(「LVDS」)インターフェースを提供する。

【解決手段】 幾つかの実施形態によれば、ファントム電力が、ガルヴァニック・アイソレータの一方の側にアイソレータの他方の側から、2つの側を相互接続するシールドが付いたツイストペア・ケーブルを介して与えられるため、電力を別の電源を通して、又はアイソレータの両側に向けられて 接続された別個の物理的な配線によって、ガルヴァニック・アイソレータの両側に与える必要性が取り除かれる。そのようなファントム電源の構成により、コストが削減され、電力消費が低下され、またノイズ・レベルが低い高速シリアルデータ通信が必要な装置の中で利用できる工学設計の選択肢の数が増加される。

(もっと読む)

半導体装置

【課題】基板バイアス印加のためのコスト負担を軽減する。

【解決手段】電源電圧Vddまたは基準電圧Vssの電圧供給線14,17にソースが接続される機能回路11内のトランジスタと、このトランジスタのチャネルが形成されるボディ領域と電圧供給線14または17との間に接続される基板バイアス可変抵抗素子(16p,16n)と、ボディ領域の電位がソース電位に対してもつ大小関係を、基板バイアス可変抵抗素子(16p,16n)の可変抵抗値により決定しているモニタ回路18と、を有する。

(もっと読む)

半導体装置

【課題】トランジスタのしきい電圧が高めに仕上がった場合に、リーク電流低減回路の制御に用いられるスイッチ回路を常にオン状態としても、当該スイッチ回路のゲート幅を大きくすることなく電源インピーダンスを低減することを可能とする半導体装置を提供する。

【解決手段】半導体装置1において、スイッチ回路SP、SNは、論理回路50に供給する電圧を、動作状態がアクティブ状態にてオン状態となり動作状態がアイドル状態でオフ状態となることで切り替える。スイッチ回路DB、DNは、スイッチ回路SP、SNと並列に接続され、スイッチ回路SP、SNの端子間のインピーダンスを低減させる。フューズ回路30は、フューズを有し、当該フューズを切断することによりスイッチ回路SP、SNを常にオン状態とし、スイッチ回路DB、DNをオフ状態からオン状態に切り替える。

(もっと読む)

半導体集積回路

【課題】CPUの動作に支障を来すこと無く、消費電力を削減することが可能な半導体集積回路を提供する。

【解決手段】CPU10と別に設けられた電源制御回路40は、半導体チップ1上に設けられたCPU10からの信号(例えばアイドル信号Si)を検出する。電源制御回路40は、この信号に応じて、CPU10に対してスイッチ素子30_1を制御して電源電圧Vpの供給を制御する。この制御により、CPU10の動作に支障をきたすことなく、効率よく電源制御が行える。

(もっと読む)

電源遮断制御回路および電源遮断制御方法

【課題】リーク電流の大きさに基づいた集積回路の電源遮断の制御をする電源遮断制御回路および電源遮断制御方法を提供する。

【解決手段】集積回路の基本回路をモデル化したモデル回路を含むモデル回路部と、前記モデル回路で生じたリーク電流によって充電される出力電圧と予め設定された基準電圧とを比較する電圧比較回路部と、前記比較結果から前記出力電圧が前記基準電圧に達するまでの到達時間を計測し、該計測結果から前記リーク電流の大きさを判定する判定回路部と、前記判定されたリーク電流の大きさに基づいて、前記集積回路の電源遮断を制御する電源遮断制御回路部と、を備える、電源遮断制御回路。

(もっと読む)

半導体集積回路及びその制御方法

【課題】 スタンバイモード中に、入力信号に応じた出力信号を生成することができる半導体集積回路を提供することを目的とする。

【解決手段】 フルタイムコア121への電源供給中にパートタイムコア122への電源供給を一時的に遮断することができる半導体集積回路であって、パートタイムコア122は、多数のレジスタ163を含む同期回路161を有し、フルタイムコア121は、外部入力されるコアゲート信号Gcに基づいて、パートタイムコア122に対する入出力信号をローレベルに固定するコアゲート回路151と、コアゲート回路151を介して同期回路161からの出力信号が入力され、外部入力されるラッチ信号Lに基づいて、入力信号の通過及び保持を選択的に行うラッチ回路152と、外部入力信号及びラッチ回路152の出力信号に基づいて、外部出力信号を生成する非同期回路162とを有する。

(もっと読む)

半導体集積回路

【課題】回路ブロックの電源供給/切断を制御する構成において安全且つ高速に回路ブロックの電源復帰が可能な半導体集積回路を提供することを目的とする。

【解決手段】半導体集積回路は、内部回路と、前記内部回路へ電源を供給する経路に設けられ、制御端子に印加される制御信号の電圧に応じた導通状態となることにより、前記内部回路への電源供給状態を制御する電源スイッチと、前記制御信号を所定の電圧にクランプするクランプ回路と、前記クランプ回路のクランプ動作の有効及び無効を切り替える切り替え回路とを含み、前記内部回路への電源供給状態を前記電源スイッチにより切断状態から供給状態に変化させるときに前記クランプ回路のクランプ動作を有効な状態に設定することを特徴とする。

(もっと読む)

半導体装置

【課題】論理回路部におけるリーク電流の低減を可能とする半導体装置を提供する。

【解決手段】半導体装置は、 第1の高電位(Vper1)を供給する第1の電源線(31)と、第2の高電位(Vper2)を供給する第2の電源線(32)と、第1の低電位(Vss1)を供給する第1の接地線(41)と、第2の低電位(Vss2)を供給する第2の接地線(42)と、第1の高電位を生成し、第1の電源線に供給する第1の内部電源発生回路(VDC1)と、第2の高電位を生成し、第2の電源線(32)に供給する第2の内部電源発生回路(VDC2)と、第1の電源線及び第1の接地線に接続された第1の論理回路(11)と、第2の電源線及び第2の接地線に接続された第2の論理回路(13)とを備える。所定数の第1の論理回路と第2の論理回路が交互に直列に接続される。

(もっと読む)

駆動回路および光スイッチ

【課題】立ち下がり時のリンギングおよび立ち上がり時のリンギングを抑制し、光スイッチの高速化を図ること。

【解決手段】駆動回路100は、抵抗R108〜110と、オペアンプOP105とを有する負電圧回路を、トランジスタFET102のソースに接続し、制御信号によってトランジスタFET101がオフ、トランジスタFET102がオンに設定された場合(SOAモジュール200をオフにする場合)に、負電圧回路の負の電流(負の電位)をSOAモジュール200に出力する。

(もっと読む)

単一電圧源CMOSのための自動検出入力回路

【課題】入力パッドに印加される比較的高電圧を維持し、回路内の供給電圧範囲の対応する信号レベルを生成する。

【解決手段】入力回路は、フローティングウェルと、対応するバイアスセレクタと、入力バイアストランジスタとを有し、予め定められた値より大きい電圧を維持する外部電圧にゲート酸化膜がさらされないようにする。バイアスセレクタは、利用可能な最高電圧を選択してフローティングウェルに対応するバイアスを逆にし、トランジスタに過度な電気的ストレスがかからないようにする。入力に関連する端子が関連する電圧を切り換えられると、バイアスセレクタは、別の端子を選択し、引き続き利用可能な最高電圧を選択して正しい逆バイアス条件を提供する。抵抗器およびクランプは、回路内の供給電圧範囲に制限された、変換された出力電圧レベルを生成する。ラッチ出力により、プルダウントランジスタは、正確なロウレベル出力信号を提供できる。

(もっと読む)

半導体装置

【課題】動作に支障が生じるような電源スイッチ制御経路の故障を検出する。

【解決手段】回路ブロック2内の回路部と、回路部の電源供給を制御する複数の電源スイッチ10と、共通の制御線11を介して複数の電源スイッチ10をオンまたはオフする制御部12と、制御部12に近い側で制御線11の途中に設けられ、その接続と遮断を制御するテストスイッチ部13と、制御部12に遠い側で制御線11に接続され、テストスイッチ部13の動作に伴う制御線電位の変化を受け、テスト応答を出力するフリップフロップ回路FFrと、を有する。

(もっと読む)

増幅回路

【課題】増幅器の消費電力を抑制する。

【解決手段】インバータにより構成された差動増幅器110は、NMOSトランジスタ142を介して電源電圧VCCと接続され、PMOSトランジスタ144を介して接地電圧GNDと接続されている。NMOSトランジスタ142は制御信号端子PSと接続され、PMOSトランジスタ144は、インバータ150を介して制御信号端子PSと接続される。NMOSトランジスタ142とPMOSトランジスタ144は、制御信号端子PSからの制御信号により同時に切断可能に制御される。

(もっと読む)

半導体素子の内部電圧生成回路及び内部電圧生成方法

【課題】外部クロックの周波数の変動にかかわらず、常に安定した電圧レベルを維持できるようにする半導体素子の内部電圧生成回路を提供すること。

【解決手段】本発明は、内部電圧端の電圧レベルが所定の目標レベルより低くなる期間において、前記内部電圧端をプルアップ駆動する第1電圧駆動手段20と、外部クロックの周波数に対応する周期の1周期毎に、所定時間の間、前記内部電圧端をプルアップ駆動する第2電圧駆動手段22とを備える半導体素子の内部電圧生成回路を提供する。

(もっと読む)

101 - 120 / 301

[ Back to top ]