Fターム[5J056CC03]の内容

Fターム[5J056CC03]の下位に属するFターム

基準電位(定電位)発生回路 (414)

Fターム[5J056CC03]に分類される特許

121 - 140 / 301

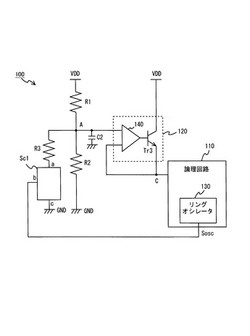

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

出力バッファ回路

【課題】電源立ち上げ時における誤作動信号の発生を抑制することのできる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第2レベルコンバータ10bから出力される第2信号Dの電源立ち上げ時における立ち下がりタイミングを遅相させ、出力回路30に出力する第4信号Gを生成するタイミング調整回路TAを備える。タイミング調整回路TAは、第1レベルコンバータ10aの第1信号Bよりも遅く立ち下がる第3信号Eを生成する第3レベルコンバータ10cと、第3信号Eと第2信号Dとの論理和演算の結果を持つ第4信号Gを出力回路30に出力するOR回路42と、を備える。

(もっと読む)

電子回路、詳細にはデジタル回路に電力を供給するための装置およびそれに関連する方法

電子回路(10)に電力を供給するための、少なくとも第1の電圧(Vhigh)、または第1の電圧と異なる第2の電圧(Vlow)を電子回路に印加することができる装置に関する方法。この装置は、具体的には、制約条件(C)を定義する情報の項目を受け取ることができ、かつ第1の期間については第1の電圧(Vhigh)に関連する第1の周波数(Fhigh)での、および第2の期間については第2の電圧(Vlow)に関連する第2の周波数(Flow)での回路の動作が、制約条件(C)を満たすようになる第1の期間および第2の期間を決定することができる性能モニタ(22)を含む。装置は、第1の期間については第1の電圧(Vhigh)および第1の周波数(Fhigh)を、ならびに第2の期間については第2の電圧(Vlow)および第2の周波数(Flow)を回路(10)に印加する(24、20、14)。  (もっと読む)

(もっと読む)

入出力回路

【課題】消費電力を低減し、かつ動作周波数の高周波数化を図り得るトレラント入出力回路を提供する。

【解決手段】入力モード時に、プルアップ側出力トランジスタP24をオフさせるゲート信号を生成するゲート信号生成部は、イネーブル信号Enと入力モード時に入出力端子Tioに入力される入力信号Diとに基づいてプルアップ側出力トランジスタP24をオフさせるゲート信号を生成する。

(もっと読む)

半導体装置

【課題】信頼性を高め、かつ消費電力の増加を低減することのできる半導体装置を提供する。

【解決手段】通信装置と無線信号の送受信を行うためのアンテナと、アンテナに電気的に接続された複数の機能回路と、を有し、複数の機能回路のうち、いずれか一の機能回路は、いずれか他の機能回路の電源回路より出力される電源電圧を制御するための電源制御回路を有し、いずれか他の機能回路における電源制御回路は、第1端子が電源回路の出力端子に電気的に接続され、第2端子がグラウンド線に電気的に接続されたトランジスタを有し、トランジスタのゲート端子がいずれか一の機能回路が有する電源制御回路に電気的に接続されている。

(もっと読む)

不揮発性記憶ゲートおよびその動作方法、および不揮発性記憶ゲート組込み型論理回路およびその動作方法

【課題】電源遮断後もデータを保持可能な不揮発性記憶ゲートを組み込み、待機状態に入ると同時に電源を遮断できる不揮発性記憶ゲートを組込み型論理回路を提供する。

【解決手段】論理ゲート16を有する論理演算部14と、不揮発性記憶部18,不揮発性記憶部に隣接して配置され,不揮発性記憶部へのデータ書込みおよび不揮発性記憶部からのデータ読出しのための制御信号を受信するデータインタフェース制御部22,データインタフェース制御部に隣接して配置され,データ入力信号Dおよびクロック信号CLKを受信し,データ出力信号Qを出力する揮発性記憶部24を有する不揮発性記憶ゲート12とを備える。

(もっと読む)

電子回路装置

【課題】半導体集積回路の容量素子と並列に接続された内部回路を高速に起動する。

【解決手段】前記の課題を解決するため、電子回路装置は、第一電圧が印加される第一電圧供給部に接続された第一容量素子と、該第一電圧供給部と該第一容量素子との間に配置された第一スイッチと、第二電圧が印加される第二電圧供給部に接続された第一負荷回路と、該第二電圧供給部と該第一負荷回路との間に配置された第二スイッチと、該第一容量素子と該第一負荷回路とを並列接続するように配置された第三スイッチと、該第一スイッチをオフ状態にするとともに該第三スイッチをオン状態にし、さらに該第二スイッチをオン状態にするスイッチ制御回路とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置において、ユーザボードの違いや製造ばらつきがあっても、電源共振ノイズによる問題を回避することができる技術を提供する。

【解決手段】半導体装置内の電源ノイズを観測する電源ノイズ観測回路1と、電源ノイズ観測回路1の出力に基づいて、生成クロック301の周波数が変化するクロック生成回路2と、生成クロック301が入力される演算回路ブロック3と、を備える。そして、前記電源ノイズ観測回路1によって観測される電源ノイズが低減するように、生成クロック301の周波数が調整される。

(もっと読む)

半導体集積回路装置

【課題】ソフトウェアによる処理負荷を大幅に低減しながら、半導体集積回路装置の低電力化処理を実現する。

【解決手段】論理回路ブロック2は、論理回路ブロック4を制御し、論理回路ブロック3は、論理回路ブロック2を制御する関係において、論理回路ブロック2のセルフパワーコントロールユニット6は、アクノリッジ信号Ack_o、選択信号sel、ならびにイネーブル信号enableが非アクティブの状態の場合に低電力要求信号となる制御信号Pw_cntlを低電力制御回路7に出力し、低電力制御を実行させる。また、セルフパワーコントロールユニット6は、イネーブル信号enable、アクノリッジ信号Ack_o、および選択信号selを監視し、これら信号のいずれか1つでもアクティブとなると、制御信号Pw_cntlを非アクティブとして、低電力制御から復帰させる。

(もっと読む)

単一電圧源CMOSのためのオープンドレイン出力バッファ

【課題】オープンドレイン出力バッファは、出力パッドに印加される比較的高電圧を受ける。

【解決手段】オープンドレインバッファは、多数のフローティングウェルと、出力スイッチングデバイスと、対応するウェル・バイアスセレクタとを有し、ゲート酸化膜が予め定められた値より大きい電圧を受けないようにする。PMOSおよびNMOSウェル・バイアスセレクタは、それぞれ、有効な最高または最低電圧を選択して印加し、対応するウェル領域をバイアスし、デバイススイッチング端子に過剰な電気的ストレスがかからないようにする。端子関連出力にスイッチング関連電圧が印加されると、ウェル・バイアスセレクタは、代わりの端子を選択して最高または最低電圧の選択を連続して行い、適正なウェルバイアス状態を提供する。分圧器は、ウェルバイアス電圧を適正に選択させる基準電圧をフローティングウェルに対して生成する。

(もっと読む)

半導体設計方法、装置、およびプログラム

【課題】電源遮断からの復帰時間が短く、かつ回路規模が抑制されたパワードメインを設計する。

【解決手段】回路挿入位置抽出部13は、パワードメインの出力側境界からN段目のFFと(N−1)段目のFFとの間の信号経路において、出力の分岐点をノードとして定義し、この定義に基づくノードモデルにおいて、N段目の各FFから(N−1)段目の各FFまでのすべての信号経路上のノードの数が同じになるようにノードを追加して、ノードモデルを更新する。そして、更新したノードモデルにおいて、N段目または(N−1)段目の各FFから見て同じノード段数となる位置に配置されたノードをカウントし、ノードの数が最も少ないノード段数に対応するノードの出力側を、電源遮断時にその直前の入力信号値を保持する機能を備えたデータラッチ回路を挿入する位置として抽出する。

(もっと読む)

出力バッファ回路、差動出力バッファ回路、調整回路及び調整機能付き出力バッファ回路並びに伝送方法

【課題】消費電力、回路面積を増やすことなく、プリエンファシス量の分解能を向上することが可能な出力バッファ回路、差動出力バッファ回路、調整回路及び調整機能付き出力バッファ回路、並びに伝送方法を提供する。

【解決手段】遅延回路23と、反転回路22と、出力バッファ3〜7とを備え、伝送線路2に論理信号を送信し、伝送線路2の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路10であって、出力バッファ3はオン抵抗に可変抵抗部分12を有し、可変抵抗値の変更によりプリエンファシス量が変更される。出力バッファ3は、前段にセクレタ20を有し、オン抵抗に可変抵抗部分12を有しており、反転回路22は、セレクタ論理により出力バッファ6に入力する信号を選択可能で、データ信号を反転し、そして、セレクタ論理のセレクト信号により、タップのプリエンファシス量を調整する。

(もっと読む)

プリント回路基板およびパッケージ基板積層の制御による半導体装置のジッタの低減

FPGA(105)内の臨界コア電圧のためにFPGA(105)とPCB電圧面(1−24)との間のインダクタンスを最小限にするようにPCB面(1−24)の積層を制御することによりデバイスジッタを低減するためのモデルおよび方法が提供される。更に、ダイ内の臨界コア電圧のためにダイと基板電圧面との間のインダクタンスを最小限にするようにパッケージ基板面の積層を制御することによりジッタを低減するためのモデルおよび方法が提供される。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】多数の機能ブロックが搭載されたSoCにおいてベクタ入力によるリーク電流削減手法に最適化されたスキャンチェイン構成及び、その制御方法を提供することである。

【解決手段】この半導体集積回路装置は、複数の機能ブロックを有する複数の電源ブロック(Area1〜AreaN)と、電源ブロックに対して動作用電源を供給可能な電源スイッチ(PSW1〜PSWN)と、電源ブロック毎に張られたスキャンチェインと、スキャンチェインに低リーク状態に遷移可能なベクタを供給するメモリ部(VEC)を具備し、スキャンチェインを非動作の機能ブロックだけに接続し直すことで、短時間に低リーク状態に遷移可能になる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置のクロック制御方法

【課題】消費電力削減の効果を発揮すること。

【解決手段】パイプライン接続された複数の演算装置4と、データ通知信号が入力されると処理制御信号を生成し出力する処理制御装置2と、処理制御信号が入力されるとクロック制御信号を生成し出力するクロック制御信号生成装置3と、を備え、演算装置4は、クロック制御信号が入力されると、クロック制御信号に基づいて、演算装置を動作させるゲーテッドクロック信号を生成し出力するクロックゲーティング回路5と、ゲーテッドクロック信号に同期して動作し、データおよび処理制御信号が入力されると、データに対して処理制御信号が指示する処理を行い、処理後のデータおよび処理制御信号を後段に接続された演算装置4へ出力する演算ブロック6と、クロック制御信号が入力されると、クロック制御信号を処理後のデータおよび処理制御信号と同期するように、演算ブロック6での処理時間分遅延して、後段に接続された演算装置4へ出力する遅延回路7と、を備える。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の試験方法

【課題】配線領域の増大を抑制しつつも、電源遮断回路が正常に機能しているかを試験することのできる半導体集積回路装置を提供する。

【解決手段】内部回路10と電源遮断回路20との間のノードAの仮想電源電圧VD1を比較電圧Vnに変換する電圧シフト回路40と、電源遮断回路20の電源通電動作時に高電位基準電圧を生成し、電源遮断動作時に低電位基準電圧を生成する基準電圧生成回路50が備えられる。また、電圧シフト回路40からの比較電圧Vnと、基準電圧生成回路50からの基準電圧VRとを比較して判定信号JSを生成し、その判定信号JSを出力パッド75に出力する電圧比較回路60が備えられる。

(もっと読む)

半導体集積回路装置

【課題】低消費電流かつ高速動作が可能な半導体集積回路装置を提供する。

【解決手段】本発明の半導体集積回路装置は、論理回路に対して、階層電源システムを備える。インバータX1、…は、高電位側のメイン電源線L1およびサブ電源線L2、低電位側のメイン接地線L3およびサブ接地線L4から電源の供給を受ける。内部電源電圧降圧回路VDC1aを配置し、メイン電源線L1の電圧を通常の高電位側の動作電源電圧より高く設定する。内部電源電圧昇圧回路VUC1aを配置し、メイン接地線L3の電圧を通常の低電位側の動作電源電圧より低く設定する。スイッチトランジスタにより、各々の電源線をショートさせた場合、各電源線の電圧を動作電源電圧に維持することが可能となる。

(もっと読む)

非同期システムにおけるリーク制御のシステム及び方法

非同期パイプラインにおけるリーク制御のシステム及び方法が開示される。実施形態において、非同期回路デバイスの動作ステージで、信号が先行ステージから受け取られ、この動作ステージに関連付けられたスイッチが、動作ステージに対する電力を使用可能にするために、動作ステージへ送られた制御信号に応じてアクティベートされる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】

本発明の目的は、連動して動作する、パワーゲーティング回路により制御されている、2以上の回路ブロックについて、一方の回路ブロックの電源ドメインが電源と接続されている状態において、他方の回路ブロックの電源ドメインが電源と接続されない状態とならないような回路を有する半導体集積回路を提供することにある。

【解決手段】

複数の回路ブロックと、回路ブロック毎に、第1制御信号の論理に応じて電源の供給、切断を行う電源スイッチと、第2制御信号を受け、複数の前記電源スイッチの内、どの電源スイッチを制御するかを選択し、選択された各電源スイッチに対応して、電源の供給又は切断を行うように指示する第3制御信号を出力する電源スイッチ制御部と、電源スイッチと電源スイッチ制御部との間に設けられ、第3制御信号の論理を変換して得られた第1制御信号を選択された各電源スイッチに出力する第1保護回路と、を備える半導体集積回路。

(もっと読む)

複数の電力領域を有する集積回路内の出力I/O信号の維持

【課題】選択的にパワーアップまたはパワーダウンさせることができる電力領域PD0,PD1,PD2,PD3を集積回路に設ける。

【解決手段】電力領域内のコア回路10によって生成された信号12をバッファする働きをする出力回路8は、それぞれ出力電力供給電圧IOVddを有している。適応型電圧感知回路24は、コア回路10へのコア電力供給電圧が閾値レベルを下回ったことを感知するとともに、低電圧信号を生成する。出力信号保持が事前に選択され、関係する出力信号に対してアクティブにされた場合に、出力回路8は、出力状態(低電圧で駆動される出力信号、高電圧で駆動される出力信号、またはハイインピーダンス駆動状態における出力信号)を維持することによって、低電圧信号に応答する。保持モードは、保持が要求されているか否かを示すモードラッチ24内に格納された値とともにオンショットパルスによって事前に選択される。

(もっと読む)

121 - 140 / 301

[ Back to top ]