Fターム[5J056CC03]の内容

Fターム[5J056CC03]の下位に属するFターム

基準電位(定電位)発生回路 (414)

Fターム[5J056CC03]に分類される特許

61 - 80 / 301

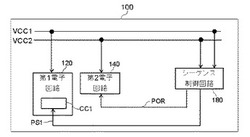

半導体集積回路装置

【課題】

複数の電源を有する半導体集積回路装置において、複数の電源が半導体集積回路装置の外部、内部であるに関わらず、それら電源の立ち上げ順序に依存せずに各回路のオン状態を一意に制御するためのシーケンス制御信号を生成することができる半導体集積回路装置を提供する。

【解決手段】

半導体集積回路装置100は、第1電源VCC1で動作する第1電子回路120と、第2電源VCC2で動作する第2電子回路140と、第1電源VCC1および第2電源VCC2の電圧の大きさを所定の検知レベルで検出し、第1電子回路120のオン動作を制御するためのシーケンス制御信号PS1、および第2電子回路140の所期化を行うためのパワーオンリセット信号PORを生成するシーケンス制御回路180を備える。

(もっと読む)

半導体集積回路及びその制御方法

【課題】従来技術の半導体集積回路では、電源遮断領域において発生する電圧降下等を抑制することができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、高電位側電源ライン14及び低電位側電源ライン15と、部分電源ライン13a,13bと、高電位側電源ライン14と部分電源ライン13aとの間に設けられた電源スイッチSWA1〜SWAmと、部分電源ライン13aと低電位側電源ライン15との間に設けられた内部回路12aと、高電位側電源ライン14と部分電源ライン13bとの間に設けられた電源スイッチSWB1〜SWBnと、部分電源ライン13bと低電位側電源ライン15との間に設けられた内部回路12bと、部分電源ライン13a,13b間に設けられ、電源スイッチSWA1〜SWAm,SWB1〜SWBnがオンの場合にオンに制御される電源スイッチSWX1〜SWXpと、を備える。

(もっと読む)

半導体装置

【課題】回路シミュレーションをすることなくスリープ状態からアクティブ状態への遷移時における、ラッシュカレントの発生を抑える半導体装置を提供する。

【解決手段】半導体装置は、複数のブロックに分割された内部回路と、各々の内部回路と電源線またはグランド線との間にそれぞれ接続されたスイッチ回路と、各々の内部回路と対応する各々のスイッチ回路との接続点に接続された制御信号生成回路とを備える。初段のスイッチ回路は、外部から入力されるスリープ信号によりオン/オフが制御され、2段目以降のスイッチ回路は、それぞれ、前段の制御信号生成回路が前段のスイッチ回路のオン/オフにより対応する接続点の電位の変化を検出して生成する制御信号により、初段のスイッチ回路と同じ状態にオン/オフが制御されることにより、上記課題を解決する。

(もっと読む)

電源回路

【課題】どの条件下でも一定のパルス幅で駆動する電源回路を提供する

【解決手段】電源回路10は、外部回路20と接続可能である。電源回路10は、一定の内部電圧を外部回路20に印加するフィードバック回路12と、パルスのパルス幅に応じた電荷を外部回路20に供給する電荷供給回路14と、外部回路20のオペレーションに対応するオペレーション状態に依存しない一定のパルスを電荷供給回路14に供給する電源制御回路16と、備える。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

半導体集積回路装置

【課題】スリープ状態の論理回路ブロックにおける寄生容量を用いることにより、電源共振雑音などの電源ノイズを大幅に低減する。

【解決手段】電源ノイズ測定回路9によって電源電圧VDDをモニタし、電源電圧VDDが任意の基準電圧以上となると、制御信号CONを出力し、スイッチコントローラ8は、仮想基準電位VSSAに蓄積された電荷を放出し、その後、任意の期間が経過すると、仮想基準電位VSSAに電荷を蓄積するようにスイッチ部6を制御することによって、基準電位VSS、および電源電圧VDDの電位を下降/上昇させ、電源電圧VDDの電源共振雑音をキャンセルする。

(もっと読む)

半導体装置

【課題】省電力化および信頼性の向上、または小面積化を実現可能な半導体装置を提供する。

【解決手段】電源遮断が行われない内部電源Vint0と電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWと、電源遮断が行われる内部電源Vint1の電圧を判定する内部電圧判定回路VINTDETを設ける。電源遮断が行われる内部電源Vint1は、外部電源Vextからレギュレータ回路VREGを用いて生成する。Vint1の電源遮断時は、SWをオフにし、VREGのオフおよびVREG出力の接地電位GNDへのショートを行い、Vint1の電源復帰時は、VREGのオンおよびショートの解除を行い、上昇したVint1の電圧をVINTDETで判定した上で回路ブロックBLK1の動作開始およびSWのオンを行う。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】スタンバイ時においてハイレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDT1L,VSSTLに接続し、スタンバイ時においてローレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDTL,VSST1Lに接続する。スタンバイ時における擬似電源線VDDTL,VDDT1L,VSSTL,VSST1Lの電位VDDT,VDDT1,VSST,VSST1は、VDDT<VDDT1<VDD、VSST>VSST1>VSSを満たす。これにより、スタンバイ状態においてオンするトランジスタのゲート電極と基板との間を流れるリーク電流や、スタンバイ状態においてオフするトランジスタのドレインと基板との間を流れるリーク電流が低減される。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】不定伝播防止回路が故障している場合に、不定伝播防止回路の故障の影響を電源遮断対象外回路に与えないようにすること。

【解決手段】半導体装置は、動作しない期間に電源供給が遮断される電源遮断対象回路M1と、電源供給が遮断されることがない電源遮断対象外回路M5と、電源遮断対象回路M1の電源供給を遮断するための信号が電源遮断対象外回路M5へ不定伝播するのを防止する不定伝播防止回路M3と、不定伝播防止回路M3から出力された信号のレベルが固定された状態であるか否かを判定し、固定された状態でない場合には、信号をあらかじめ設定した基準信号と切り替える故障検出・故障回避制御回路M4と、故障検出・故障回避制御回路M4から出力された信号に基づいて、電源遮断対象回路の電源供給状態を制御する電源制御回路M6と、を備える。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】電源線VDDTL,VSSTL間に接続された回路ブロック10Aと、電源線VDDTL,VSSL間又は電源線VDDL,VSSTL間に接続された回路ブロック10Aの出力信号を受ける論理回路10B−1と、電源線VDDL,VSSL間に接続された論理回路10B−1の出力信号を受ける回路ブロック20と、を備える。電源線VDDTL,VSSTL間には、アクティブ状態においては第1の電圧、スタンバイ状態においては第1の電圧よりも低い第2の電圧が供給され、電源線VDDL,VSSL間には、アクティブ状態及びスタンバイ状態のいずれにおいても第1の電圧が供給される。これにより、サブシュレッショルド電流低減を維持しつつ、クリティカルパスの高速化を実現することが可能となる。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の内部電圧生成回路に供給されるグランド電圧の変動による影響を抑制すること。

【解決手段】内部回路は、内部電圧生成回路によって生成される内部電圧に基づいて動作する。また、内部電圧生成回路及び内部回路は、グランド配線を介してグランドに接続される。内部電圧生成回路は、内部電圧が出力される出力端子と、グランド配線に接続されるグランド端子と、電圧が基準電圧に応じた値に制御される中間ノードと、出力端子と中間ノードとの間に接続された第1抵抗部と、中間ノードとグランド端子との間に接続された第2抵抗部と、第1抵抗部の抵抗値R1と第2抵抗部の抵抗値R2の比率R1/R2を切り換えるスイッチ部と、を備える。スイッチ部は、内部回路が動作する時の比率を、内部回路が動作を停止している時の比率よりも大きくする。

(もっと読む)

半導体装置

【課題】チップの製造プロセスの微細化にともなって各種リーク電流(サブスレッショルドリーク電流、ゲートトンネルリーク電流、GIDL(Gate-Induced Drain Leakage)電流などの接合リーク電流)が増大している。それらのリーク電流はチップの消費電流を増加する。

【解決手段】第1回路ブロックと、前記第1回路ブロックに接続される第1電源線及び第2電源線と、前記第1電源線と第1電位を供給する第1電位点とを接続するための第1トランジスタと、前記第1トランジスタのゲートに接続される第1駆動回路と、前記第1駆動回路より駆動力の大きい第2駆動回路とを有し、第1の状態から前記第1の状態よりも前記第1電源線と前記第2電源線の間の電位差が大きい第2の状態へ遷移する場合に、第1の期間において前記第1トランジスタを前記第1駆動回路によって駆動し、その後第2の期間において前記第1トランジスタを前記第2駆動回路によって駆動する。

(もっと読む)

半導体装置

【課題】内部電源電圧の急激な変化に追従し、安定した内部電源電圧を供給することができる電源部を備えた半導体装置を提供する。

【解決手段】半導体装置は、集積回路からなるコア回路と、内部電源からの電圧および外部電源からの電圧を受け、コア回路から転送されるデジタルデータを出力するドライバと、コア回路からのデータを一時的に保持し、前記ドライバに該デジタルデータを転送するフェッチ部とを含む周辺回路と、ドライバに電源線を介して内部電圧を供給する第1の電源部と、外部電源と電源線との間に直列に接続された電流駆動素子およびスイッチング素子をそれぞれ含む複数の電流駆動列を備え、複数の電流駆動列を駆動することによって第1の電源部とは別に電源線に電流を供給する第2の電源部と、デジタルデータの連続するビット間で論理が遷移するときに複数の電流駆動列の少なくとも1つを駆動させるように第2の電源部を制御する電源制御部とを備える。

(もっと読む)

集積回路装置、電子機器及び調整電圧の制御方法

【課題】 温度条件が変化しても停止電圧との適切な電位差を保ち低消費電力を実現する集積回路装置等を提供する。

【解決手段】 集積回路装置1であって、第1の振幅と比べて、入力された発振信号400の振幅の方が大きい場合に、第1の矩形波信号408を出力する第1の矩形波信号生成部11と、前記第1の振幅よりも大きな第2の振幅と比べて、前記発振信号400の振幅の方が大きい場合に、第2の矩形波信号402を出力する第2の矩形波信号生成部12を含む。

(もっと読む)

半導体装置及び電源スイッチ回路

【課題】電源スイッチがオフからオンの状態に遷移するときの突入電流を防ぐことにより電源スイッチオンに起因する電源ノイズの発生を防止する半導体装置及び電源スイッチ回路を提供する。

【解決手段】電源スイッチ回路が、ソースが第1の電源にドレインが前記機能回路に接続された電源スイッチトランジスタと、電源スイッチトランジスタのオンオフを制御する制御信号を入力とし、電源スイッチトランジスタのドレインと、ソースと、ゲートとにそれぞれ接続され制御信号に基づいて電源スイッチトランジスタをオフからオンの状態にスイッチさせるとき、電源スイッチトランジスタのソースドレイン間電圧が小さくなるほど電源スイッチトランジスタのソースゲート間電圧が大きくなるように電源スイッチトランジスタのゲート電圧を制御する電源スイッチトランジスタ制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】外部負荷を駆動する入出力回路を有するデジタル回路と、外部回路と通信を行う通信回路を備えるアナログ回路とを混載して成る半導体集積回路において、入出力回路による内部発生ノイズを低減し、アナログの通信回路における通信エラーの発生を抑える。

【解決手段】外部負荷となるメモリ5を駆動する入出力回路3とCPU2とを有するデジタル回路と、イーサーネットによって外部回路と通信を行う通信回路41を備えるアナログ回路4とを混載して成る半導体集積回路1において、前記入出力回路3と電源VDDとの間に電圧調整回路6を介在して、入出力回路3への供給電源電圧VDD’を可変にする。そして、CPU2が前記通信回路41からエラー通知F2を受信すると、電圧制御回路6へ電圧制御信号F3を出力し、前記入出力回路3の動作を保証できる下限電圧までの範囲で、パッド31,32に加わる電圧を低下させ、ノイズF1を抑える。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】回生により消費電力を抑制する回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、第1の電源電圧VPと第2の電源電圧VMを供給する電源回路100と、第1の電源電圧VPと第2の電源電圧VMが供給されることで断熱的回路動作を行う論理回路200と、を含む。電源回路100が供給する第1の電源電圧VPは、第1の基準電圧を基準電圧として周期的に変化する。電源回路100が供給する第2の電源電圧VMは、第2の基準電圧を基準電圧として周期的に変化する。電源回路100は、第1の電源電圧VPと第2の電源電圧VMの電圧差が小さくなっていく第1の期間と大きくなっていく第2の期間を繰り返す第1の電源電圧VPと第2の電源電圧VMを共振により供給する。

(もっと読む)

集積回路の電力管理

【課題】集積回路の一部分を低電力状態にすることができるだけでなく、そのような部分がこの低電力状態から出る時に、迅速に処理動作を再開できることが望ましい。これを支援するために、論理回路の状態変数は、低電力状態の間維持される必要がある。

【解決手段】集積回路2は、実質(virtual)電力線6、8に接続される論理回路4を含む。これらの実質電力線は、電力制御トランジスタ10、16を介して、電力供給源14に接続される。電力制御装置20は、導電状態にある多数の電力制御トランジスタ10、16を決定する、制御信号を生成し、したがって、中間電圧レベルを有するように実質電力線を制御する。中間電圧レベルを選択して、論理回路を保持モードで維持してもよく、この状態は論理回路4内で維持されるが、処理動作は行われない。機能モードが再入力されると、ヘッダーおよびフッタートランジスタ10、16のすべてが導電状態に切り替えられ得る。

(もっと読む)

半導体装置及び情報処理システム

【課題】電源電圧を低下させた場合であっても、正しくデータ転送が可能な半導体装置を提供する。

【解決手段】出力ドライバ100と、出力ドライバ100の特性を切り替える特性切替回路18を備える。特性切替回路18は、電源ラインに供給される電源電圧VDDQが第1の電圧VDDQ1である場合における出力ドライバ100の出力信号の立ち上がり時間及び立ち下がり時間と、電源ラインに供給される電源電圧VDDQが第2の電圧VDDQ2である場合における出力ドライバ100の出力信号の立ち上がり時間及び立ち下がり時間を互いに一致させる。これにより、電源電圧を低下させても高調波成分やクロストークによる影響が増大することがない。また、電源電圧を低下させてもレシーバ側における受信条件が変化しないことから、電源電圧にかかわらず信号の送受信を正しく行うことが可能となる。

(もっと読む)

半導体集積回路

【課題】ゲートリークによる消費電力の増大を抑制し、電源[VDD]−[GND]間のノイズを低減すること。

【解決手段】本発明の半導体集積回路は、機能ブロックと領域部3bとを具備している。機能ブロックは、電源[VDD]−[GND]間に設けられ、常に動作する。領域部3bにおいて、周辺機能ブロック4は、信号線9と電源[GND]との間に設けられ、動作モード又は非動作モードを実行する。電源スイッチMPは、電源[VDD]と信号線9との間に設けられ、動作モードにおいて電圧VDDを信号線9に供給し、非動作モードにおいて信号線9への電圧VDDの供給を遮断する。MOSトランジスタは、周辺機能ブロック4に設けられ、そのバックゲートに電源[VDD]と電源[GND]との一方の電源が接続されていて、非動作モードにおいて、そのゲートに他方の電源が接続され、そのゲートとバックゲート間に寄生容量を発生する。

(もっと読む)

61 - 80 / 301

[ Back to top ]