Fターム[5J056DD02]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | バイポーラトランジスタ (120)

Fターム[5J056DD02]の下位に属するFターム

マルチエミッタトランジスタ (1)

マルチコレクタトランジスタ

ラテラルトランジスタ (1)

バーティカルトランジスタ

逆方向動作トランジスタ

寄生トランジスタ (4)

Fターム[5J056DD02]に分類される特許

1 - 20 / 114

複数の集積回路にインタフェース信号を供給する方法および回路

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】トランシーバ回路30等の通信回路に接続される通信線10を構成するHライン通信線10H,Lライン通信線10L間にリンギング抑制回路1が設けられる。リンギング抑制回路1において、バイポーラトランジスタT1のエミッタはHライン通信線10Hに接続され、コレクタはLライン通信線10Lに接続され、ベースはコンデンサC1の一方電極及び抵抗R1の一端に接続され、コンデンサC1の他方電極はLライン通信線10Lに接続され、抵抗R1の他端はHライン通信線10Hに接続される。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

信号出力回路

【課題】トランジスタ製造工程をnpn型の製造工程のみとして、使用可能な化合物半導体の自由度を高め、単相のデジタル信号により外部から出力透過/遮断を切替制御する。

【解決手段】トランジスタとしてnpn型を用いて構成し、入力バッファ11で、外部入力された単相切替指示信号10Sを、互いの位相が反転している差動切替指示信号11Sに変換し、発生制御回路13で、差動切替指示信号11Sに基づいて、制御電圧発生回路14における制御電圧VCSの発生を制御するための発生制御信号13Sを出力し、制御電圧発生回路14で、発生制御信号13Sに基づいて、単相切替指示信号10Sの論理に応じて電圧値が変化する制御電圧VCSを発生させて出力し、出力回路15で、入力された差動入力信号INをインピーダンス変換し差動出力信号OUTとして出力し、制御電圧VCSに基づいて当該差動入力信号INの出力透過/遮断を切り替える。

(もっと読む)

電源回路

【課題】本発明は、電源回路を提供することを目的とする。

【解決手段】本発明の電源回路は、複数のロードに電力を供給するために用いられ、複数の制御端を有する制御回路、第一電力供給回路、第二電力供給回路及び第三電力供給回路を備え、各々の電力供給回路は、それぞれ制御回路の1つの制御端に接続され、各々の電力供給回路は、全てスイッチングユニットを備え、スイッチングユニットは、第一端、第二端、第一端と第二端との間の接続及び切断を制御するスイッチング端を備え、第一端は、電源に接続され、第二端は、1つのロードに接続され、スイッチング端は、制御端に接続され、第二電力供給回路及び第三電力供給回路は、全て遅延回路をさらに備え、遅延回路は、制御回路の制御端とスイッチングユニットのスイッチング端との間に接続され、第三電力供給回路の遅延回路の遅延時間は、第二電力供給回路の遅延回路の遅延時間より大きい。

(もっと読む)

半導体集積回路

【課題】コンデンサの供給する電源電圧の低下により、誤動作を起こす虞がある。

【解決手段】通常動作より低い消費電力状態である低消費電力モードを有する半導体集積回路であって、前記低消費電力モード状態時に、電源電圧レベルを検出する検出手段と、前記検出した電源電圧レベルを記憶する記憶手段と、前記通常動作時よりも小さい電流を流すことで、前記電源電圧を低下させる擬似負荷手段と、前記擬似負荷手段により電流を流す前に前記記憶手段で記憶した第1の電圧レベルに応じて前記検出手段の検出レベルを第2の電圧レベルに切り換える切換え手段と、前記擬似負荷手段により電流を流すことにより低下した前記電源電圧が、前記第2の電圧レベルとなるかを判定し、前記低消費電力モードを解除するか否かの制御を行う制御手段と、を有する半導体集積回路。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時の貫通電流が、ロジック回路を構成するP型トランジスタとN型トランジスタの閾値電圧ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタを有し、内部電源電圧の値が、N型トランジスタの閾値電圧と、P型トランジスタの閾値電圧の絶対値の和に基づいて与えられ、前記N型トランジスタは、前記ロジック回路内部のN型トランジスタと同一の製造プロセスで形成され、前記P型トランジスタは、前記ロジック回路内部のP型トランジスタと同一の製造プロセスで形成される、内部電源電圧生成回路、とした。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時、貫通電流が、製造ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタと、前記ゲートに与えられる電圧をソースフォロワ出力するトランジスタの最大電流を制限する電流制限回路と、を備え、ロジック回路への最大電流、及び消費電流を抑えることが可能な構成とした。

(もっと読む)

クロック入力インターフェース回路

【課題】低消費電力なクロック入力インターフェース回路を提供する。

【解決手段】クロック入力インターフェース回路1は、インピーダンス整合・出力電圧調整抵抗R11,R13と、出力電圧調整抵抗R12,R14と、電流安定化抵抗R15,R16と、反射防止終端抵抗R17と、DCレベル阻止容量C1,C2と、RFバイパス容量C3,C4と、電流源トランジスタQ1,Q2とから成る。クロック入力端子CKにクロック信号を入力する伝送線路とインピーダンス整合し、かつ次段の回路の入力端子で必要とされるDCバイアス電圧を出力端子OT,OCに与えることができるように、抵抗R11〜R14,R17の値および容量C1〜C4の値が設定される。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

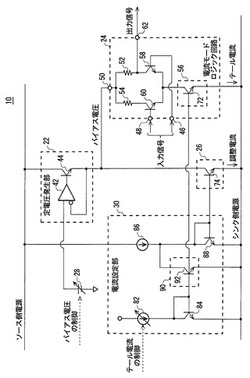

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

多値記憶手段、多値バッファ手段および双方向性スイッチング手段

【課題】C・MOS・FET等の相補型3端子スイッチング手段を用いたオン・オフ駆動手段も使用できる双方向性スイッチング手段を提供する。

【解決手段】どちらも両主電極の役割がその印加電圧の方向により互いに入れ換わることができ、どちらも互いに相補関係に有る2つのオン・オフ制御スイッチング手段が有って、その両オン・オフ制御スイッチング手段のうち一方の主電極と他方の主電極を接続し、一方の開放された主電極と一方の制御電極の間に一方のオン・オフ駆動手段を設け、一方の開放された主電極と他方の制御電極の間に他方のオン・オフ駆動手段を設け、その両オン・オフ制御スイッチング手段の直列回路を双方向性のスイッチとして使用する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

信号出力回路

【課題】より簡単な構成で、正弦波と同様に緩やかに変化する波形でスイッチング素子を制御できる信号出力回路を提供する。

【解決手段】NチャネルMOSFET8Tは、ゲートに与えられるPWM信号のレベル変化に応じてカレントミラー回路7の動作を制御し、カレントミラー回路7が動作すると電流源6が発生した電流がミラー電流として流れ、NチャネルMOSFET1のゲートを介してゲート−ソース間の容量成分に充電されている電荷を放電させる電流が流れる。カレントミラー回路7の動作が停止すると、カレントミラー回路5より電流源6を介して流れる電流が、NチャネルMOSFET1のゲートに充電電流として供給される。

(もっと読む)

レベルシフト回路

【課題】バッテリの電源投入時等の電源電圧の急激なオーバーシュートに対する耐性を向上させるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、バッテリからの高電圧レベルの入力信号VINを入力するレベルシフト部10と、レベルシフト部10の中間信号Vmを一定以下に制限するクランプ部20と、中間信号をより低電圧のCMOSレベルで出力する出力バッファ部30とを備える。出力バッファ部30の初段においてpMOSトランジスタ31の負荷を抵抗32とすることにより、電源電圧のオーバーシュートに対する耐性を向上させる。

(もっと読む)

半導体装置

【課題】省電力化および信頼性の向上、または小面積化を実現可能な半導体装置を提供する。

【解決手段】電源遮断が行われない内部電源Vint0と電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWと、電源遮断が行われる内部電源Vint1の電圧を判定する内部電圧判定回路VINTDETを設ける。電源遮断が行われる内部電源Vint1は、外部電源Vextからレギュレータ回路VREGを用いて生成する。Vint1の電源遮断時は、SWをオフにし、VREGのオフおよびVREG出力の接地電位GNDへのショートを行い、Vint1の電源復帰時は、VREGのオンおよびショートの解除を行い、上昇したVint1の電圧をVINTDETで判定した上で回路ブロックBLK1の動作開始およびSWのオンを行う。

(もっと読む)

リンギング抑制回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できるリンギング抑制回路を提供する。

【解決手段】電源と信号線12Pとの間に接続されるNチャネルMOSFET19と、信号線12Mとグランドとの間に接続されるPチャネルMOSFET20とを備え、リンギング抑制回路18は、信号線12P,12Mの電位と、それぞれに対応するNチャネルMOSFET19,PチャネルMOSFET20のゲートに付与される電位との差に応じてNチャネルMOSFET19及びPチャネルMOSFET20をオンさせて、信号線12P,12Mに発生しようとするリンギングの抑制を図る。

(もっと読む)

1 - 20 / 114

[ Back to top ]