Fターム[5J056EE08]の内容

Fターム[5J056EE08]に分類される特許

201 - 220 / 232

入力保護回路

【課題】 外部入力端子に回路の動作電源電圧を超える電圧が印加される場合でも、電源電圧以下にクランプすることができる入力保護回路を提供する。

【解決手段】 FET7は、外部入力端子3に印加される電圧を電流ΔI1に変換し、FET6は、その変換された電流に対して所定のミラー比を有する電流ΔI2を発生させる。そして、電流ΔI2が抵抗素子10に流れることで、ECU1の動作電源電圧VDDより抵抗素子10の端子電圧分だけ降下した電圧を,インバータゲート11の入力端子に印加する。

(もっと読む)

出力バッファ回路

【課題】高スルーレートでスルーレート変動の少ない出力バッファ回路を実現する。

【解決手段】NMOSトランジスタM3をONすることで容量C1と容量C2との容量比で出力トランジスタであるPMOSトランジスタM1のゲート電圧をしきい値電圧以下に低下させ、PMOSトランジスタM1をONさせ、同時に、電流源I1により最終的にPMOSトランジスタM1のゲート電圧を0Vにし、さらに、PMOSトランジスタM4をONすることで容量C3と容量C4の容量比で出力トランジスタであるNMOSトランジスタM2のゲート電圧をしきい値電圧以下に低下させ、NMOSトランジスタM2をONさせ、同時に電流源I2により最終的にNMOSトランジスタM2のゲート電圧を電源電圧レベルにする構成とし、出力トランジスタのゲート電圧を容量分圧制御で行う。

(もっと読む)

半導体装置

【課題】異なる電圧ドメインに属する回路間において、高速に信号を伝播することが困難であった。

【解決手段】第1のインバータ回路INV1は、電流通路の一端が接地された第1導電型の第1のトランジスタN1の電流通路の他端に第2の導電型の第2のトランジスタP1の電流通路の一端が接続され、各ゲートに接地電位より高い第1の電圧V1の一方からなる第1の信号CKIが供給される。第2導電型の第3のトランジスタP2は、第2のトランジスタP1の電流通路の他端と第1の電圧より高い第2の電圧V2が供給されるノードとの間に接続され、ゲートに第1の信号の変化から遅れて接地電位と、第2の電圧の一方からなる制御信号LSOが供給され、第1のインバータ回路INV1の出力端から接地電位と前記第2の電圧の一方からなる第2に信号CKOを出力する。

(もっと読む)

半導体切替回路およびその評価装置

【課題】 ウェーハ状態で容易に高周波評価試験を行うことが可能な半導体切替回路およびその評価装置を提供する。

【解決手段】 共通端子RF_COM、第1、第2の独立端子RF_1、RF_2、第1、第2の制御端子Vcont1、Vcont2、第1の独立端子と共通端子との間に、ソース、ドレインが直列に結合された第1のFET T1、第2の独立端子と共通端子との間に、ソース、ドレインが直列に結合された第2のFET T2、第1、第2のFETのゲートと、第1、第2の制御端子との間にそれぞれ接続された、第1、第2の抵抗素子Rgg1、Rgg2とを備え、第1、第2の制御端子と第1、第2の独立端子のうち、少なくともいずれか1組が隣接するように配置されており、第1、第2の制御端子は容量素子Cxを介して接続されている。

(もっと読む)

電源電圧検出回路

【課題】電源電圧が低下して所定の電圧よりも低い電圧となった場合であっても、電源電圧の検出信号が安定しており、システムの誤動作を防止することができる電源電圧検出回路を提供する。

【解決手段】電源電圧検出回路は、電源電圧が低下して第1の電圧となった時に、その出力信号が反転し、さらに電源電圧が低下して第1の電圧よりも低い第2の電圧よりも低い電圧の領域で、その出力信号が少なくとも1回以上反転する第1の電源電圧検出回路と、電源電圧が低下して第1の電圧よりも低く、かつ第2の電圧よりも高い電圧の領域で、その出力信号が1回だけ反転する第2の電源電圧検出回路と、第1の電源電圧検出回路の出力信号と第2の電源電圧検出回路の出力信号との論理をとり、電源電圧が第1の電圧よりも低い電圧かどうかを表す検出信号を出力する論理回路とを備える。

(もっと読む)

半導体集積回路

【課題】 リセット動作を自動的に実行可能な半導体集積回路を提供する。

【解決手段】 高位ロジック電源VDD及び高位電源VGGにゲート及びソースがそれぞれ接続された第1MISトランジスタTr1と、第1MISトランジスタTr1のドレイン、出力ノードn1、及び低位電源VEEにドレイン、ゲート、及びソースがそれぞれ接続された第2MISトランジスタTr2と、高位ロジック電源VDD、接続ノードn2、及び出力ノードn1にソース、ゲート、及びドレインがそれぞれ接続された第3MISトランジスタTr3と、出力ノードn1、第3MISトランジスタTr3のゲート、及び低位電源VEEにドレイン、ゲート、及びソースがそれぞれ接続された第4MISトランジスタTr4と、高位ロジック電源VDD、高位電源VGG、及び出力ノードn1にソース、ゲート、及びドレインがそれぞれ接続された第5MISトランジスタTr5とを備える。

(もっと読む)

内部電圧供給回路

【課題】ウェハー製造工程条件による半導体装置の電流駆動能力差を反映して入出力センスアンプなどのソース電圧に使用される内部電圧を調節することで、半導体装置の電気的特性を向上し、不要な電流消耗を減少してエネルギー効率を増加できる内部電圧供給回路を提供する。

【解決手段】第1イネーブル信号SAP1に応答して第1電圧Vppを供給する第1電圧駆動部N100と;第2イネーブル信号SAP2に応答して第2電圧Vcoreを供給する第2電圧駆動部N200と;半導体装置の電流駆動能力によって所定時間のイネーブル区間を有する前記第1イネーブル信号SAP1を供給する第1イネーブル信号発生部200と、を含んで構成されており、半導体装置の前記電流駆動能力が所定の基準駆動能力よりも大きい場合は、前記イネーブル区間の幅を所定基準幅よりも相対的に小さく設定し、前記電流駆動能力が前記基準駆動能力よりも小さい場合は、前記イネーブル区間の幅を前記所定基準幅よりも相対的に大きく設定して内部電圧供給回路を構成する。

(もっと読む)

レベルシフト回路

【課題】 耐圧の低い素子を使用でき、素子定数のばらつきの影響を受けにくいレベルシフト回路を提供する。

【解決手段】 駆動制御信号SHがLからHになると、レベルシフト回路18のトランジスタQ11、Q12がオフし、Q13、Q14、Q15がオンする。これによりノードNc、Neの電位が上昇し、駆動回路15のトランジスタQ17がオン、Q18がオフする。このとき、ノードNdの電圧V(Nd)はVDD−Vf(D14)−Vz(D12)までしか低下しないため、トランジスタQ5のゲート・ソース間を高電圧から保護することができる。また、トランジスタQ12のゲートにVHS−Vf(D14)なる中間的な電圧が与えられているため、トランジスタQ12とQ11は電圧VBSを分担する。このため、トランジスタQ11、Q12を高電圧から保護することができる。

(もっと読む)

エッジパルス生成回路

【課題】 入力信号が劣化していても正常動作を行い、エッジパルス幅の変動が小さく、実装基板の面積やレイアウトに影響を与えないエッジパルス生成回路を提供する。

【解決手段】 入力端子と、出力端子と、入力信号の1ビット以下の遅延値をもつ遅延素子1aと、差動増幅器3とを備え、入力端子を遅延素子1aの入力側と差動増幅器3の正側入力に接続し、遅延素子1aの出力側を差動増幅器3の負側入力に接続する。前記遅延素子1aはインダクタ素子Lと容量素子CのL型回路のn段直列接続により構成し、かつ該遅延素子1aは差動増幅器3と同じ集積回路上に形成する。

(もっと読む)

2相クロック駆動チャージポンプ回路、4相クロック駆動チャージポンプ回路、および昇圧回路

【課題】 高電圧がかかることによって起こる素子の破壊を回避する。

【解決手段】 チャージポンプ回路には、直列接続されたNchトランジスタT1〜T(n+1)と、キャパシタC1〜C(n−1),Cpがある。最終段以外のキャパシタC1〜C(n−1)の他端には、クロック信号の振幅Vccを2倍昇圧回路A1〜A(n−1)で2倍にして得られる振幅が2×Vccレベルの電圧を供給する。最終段のキャパシタCpの他端には、振幅がVccレベルのクロック信号CLKを供給する。

(もっと読む)

論理回路

【課題】 電界効果型トランジスタで構成した複数の電流モード論理回路を多段接続した論理回路において、トランスコンダクタンスgmやトランジスタの遮断周波数fTを改善し、かつ高速・広帯域化する。

【解決手段】 複数の電流モード論理回路を多段接続した論理回路であって、各電流モード論理回路は、一端が高電位側電源に接続された2つの抵抗と、ドレインがそれぞれ2つの抵抗の他端に接続され、かつ、それぞれ2つの出力端子に接続され、ゲートがそれぞれ2つの入力端子に接続され、エソースが共通接続された2つの電界効果型トランジスタと、一端が2つの電界効果型トランジスタのエソースに接続され、他端が低電位側電源に接続された定電流源とを有し、後段の電流モード論理回路ほど、2つの抵抗の一端に印加される電位が高い。

(もっと読む)

半導体集積回路装置

【課題】 高電圧から低電圧へのレベルシフト回路を小さな回路面積で構成した半導体集積回路装置を提供する。

【解決手段】 高電圧動作回路部から低電圧動作回路部へ信号を伝達するレベルシフト回路を、ゲート電極が低電圧動作回路の電源電圧電位に固定されたデプレッション型NMOSトランジスタで構成した。

(もっと読む)

チャージポンプ回路

【課題】電荷転送用MOSトランジスタの寄生ダイオードのリークパスを遮断し、消費電力の増加を防止すると共に、回路が制御不能に陥るのを防止する。

【解決手段】第1の電荷転送用MOSトランジスタM1及び第2の電荷転送MOSトランジスタM2はNチャネル型であり、互いに直列に接続されている。第1の電荷転送用MOSトランジスタM1のソースには接地電位VSSが供給され、第2の電荷転送MOSトランジスタM2のドレインである出力端子Poutから出力電位が得られる。第1の電荷転送用MOSトランジスタM1のバックゲートG1は、第1のスイッチング回路SW1によって、第1及び第2の電荷転送用MOSトランジスタM1,M2の接続点の電位Xと入力電位である接地電位VSSとのいずれか一方の電位に設定されるように構成されている。

(もっと読む)

インターフェース回路

【課題】 LVDSインターフェース回路及びCMOSインターフェース回路を併用する。

【解決手段】 LVDS信号と、第1のCMOS信号のいずれか一方を選択する第1の選択回路21と、LVDS信号及びこの第2のCMOSのいずれか一方を選択する第2の選択回路22と、この第1の選択回路21の出力信号を夫々のゲートに供給する第1のPチャンネルMOSトランジスタ25P及び第1のNチャンネルMOSトランジスタ25Nと、この第2の選択回路22の出力信号を短絡スイッチ26a付きインバータ回路26を介して夫々、共通の定電流源28、30を有する25Pと25NからなるCMOSのゲート、及び27P27NからなるCMOSの2つCMOSのゲートを介して出力する。

(もっと読む)

ロー漏洩電流を持つレベルシフタ

【課題】 待機モードとアクティブモードの両方でロー漏洩電流を流すレベルシフタを提供する。

【解決手段】 電圧レベルシフト回路は、Vcc>Vssの電圧レベルVcc、Vssを持つ入力信号を受信し、VIhigh>VIlowの電圧レベルVIhigh、VIlowを持つ相補的な第1、第2中間信号を出力する第1ステージと、前記第1、第2中間信号を受信し、VOhigh>VOlowの電圧レベルVOhigh、VOlowを持つ相補的第1、第2出力信号を出力する第2ステージと、を備え、VIhigh>VOhighまたはVIlow<VOlowであり、VOhigh>VccかつVOlow<Vssであることを特徴とする。

(もっと読む)

半導体集積回路装置及びそれを用いた半導体システム

【課題】簡単な構成によりNBTI対策機能を備え、高信頼性を実現した半導体集積回路装置と半導体システムを提供する。

【解決手段】MOSFET回路を構成するPチャネルMOSFETのうち、NBTIによって回路動作マージンが劣化すると予測されるMOSFETをターゲットとして、そのゲートに信号供給を行う伝達経路に第1スイッチを設け、所定の動作モードのときに上記第1スイッチをオフ状態にし、かつ、上記MOSFETのゲートにチャネル電圧よりも絶対値的に高い電圧を供給する回復電圧印加回路を設ける。

(もっと読む)

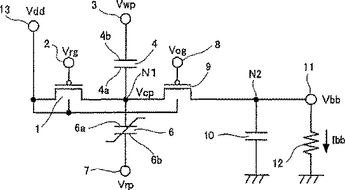

電圧発生回路、電圧発生装置及びこれを用いた半導体装置、並びにその駆動方法

キャパシタ(4)、キャパシタ(4)に直列接続された強誘電体キャパシタ(6)、出力端子(11)、出力端子(11)を接地するキャパシタ(10)、電源電圧供給端子(13)、電源電圧供給端子(13)と2つのキャパシタ(4,6)の接続ノード(N1)とを接続するスイッチ(1)、及び接続ノード(N1)と出力端子(11)とを接続するスイッチ(9)を備え、第1の期間において、スイッチ(1)及び(9)がオフ状態にされた状態で、端子(3)が接地されると共に端子(7)に電源電圧が供給され、第2の期間において、端子(3)に電源電圧が供給され、且つスイッチ(9)がオン状態にされ、第3の期間において、スイッチ(9)がオフ状態にされ、スイッチ(1)がオン状態にされ、且つ端子(7)が接地され、第4の期間において、端子(7)に電源線圧が供給され、前記第1の期間から前記第4の期間までが順に繰り返される、電圧発生回路。  (もっと読む)

(もっと読む)

出力ドライブ回路及び出力ドライブ回路の制御方法

【課題】 本発明は、LVDSドライブ回路において、電源電圧より低耐圧のトランジスタをスイッチングトランジスタに用いることにより、LVDSドライブ回路の最大動作周波数改善し、その低耐圧トランジスタに耐圧以上の電圧がかからない様にする。

【解決手段】 本発明の出力ドライブ回路はスイッチング回路14のPMOSトランジスタ4、6とPMOSトランジスタ5,7の電源電圧(例えば2.5V)に比べて(例えば、1.8V)の電圧で低耐圧化し、上記スイッチング回路14のPMOS及びNMOSトランジスタ4、6と5,7のゲートGに供給する論理L及び論理Hレベルを出力するPMOS用及びNMOS用レベルシフタ回路18と19並びに出力パスを遮断或いは接続する出力スイッチング回路20を追加しコモンモード回路15により電流制御回路8を制御させたものである

(もっと読む)

半導体集積回路、駆動回路及びプラズマディスプレイ装置

【課題】 温度変化に対して消費電力の増加や駆動マージンの低下が少ないプラズマディスプレイ装置の実現。

【解決手段】 入力信号IN1を遅延させ、その遅延量を変化させる遅延時間調整回路61と、遅延時間調整回路の出力信号を所定の電圧と比較する比較回路62と、比較回路の出力信号を出力基準電圧を基準とした信号へシフトするハイレベルシフト回路63と、ハイレベルシフト回路の出力信号を増幅して半導体素子を駆動する信号を出力する出力増幅回路64とが1チップ上に形成されたIC60でPDP装置のサステイン回路を構成する。

(もっと読む)

電源瞬断対応論理回路

【課題】 供給される電源の一時的な低下もしくは停止に対してデータを保持し続けることができる電源瞬断対応論理回路を提供する。

【解決手段】 第1スイッチSW1を介して外部回路からデータ信号が入力されると共に、データ信号をラッチする第1ラッチ回路L1と、第2スイッチSW2を介して第1ラッチ回路L1にてラッチされているデータ信号を入力し、そのデータ信号をラッチすると共に外部回路に出力する第2ラッチ回路L2と、を備える。また、第1、第2ラッチ回路L1、L2は、データ信号に対応した電圧を保持する第1、第2コンデンサCP1、CP2と、第1、第2コンデンサCP1、CP2にて保持される電圧の変動を抑制する第1、第2抵抗RS1、RS2と、をそれぞれ有する。さらに、第1、第2コンデンサCP1、CP2は、その電極の一方が第1、第2抵抗RS1、RS2の電流出力側に接続されている。

(もっと読む)

201 - 220 / 232

[ Back to top ]