Fターム[5J056EE08]の内容

Fターム[5J056EE08]に分類される特許

81 - 100 / 232

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

出力バッファ回路および固体撮像素子

【課題】消費電力を低減させることができるようにする。

【解決手段】出力バッファ回路31において、PチャネルMOSトランジスタM4のソースは、プッシュプル回路15のNチャネルMOSトランジスタM6のゲートと接続され、PチャネルMOSトランジスタM4のソース出力によって、NチャネルMOSトランジスタM6が駆動される。また、NチャネルMOSトランジスタM5のソースは、プッシュプル回路15のPチャネルMOSトランジスタM7のゲートと接続され、NチャネルMOSトランジスタM5のソース出力によって、PチャネルMOSトランジスタM7が駆動される。PチャネルMOSトランジスタM4とNチャネルMOSトランジスタM5は、電流源Q11を介して直列に接続されている。本発明は、例えば、固体撮像素子に用いられる出力バッファ回路に適用できる。

(もっと読む)

出力回路、及びそれを用いた車載用通信システム

【課題】回路面積が小さく、製造バラツキによる出力特性の劣化を修正できる出力回路を提供することにある。

【解決手段】本発明による出力回路は、差動入力信号DIに応じた差動出力信号BP、BNを出力端子対31、32から出力するメインバッファ回路1と、制御信号CSに応じて出力端子対31、32のインピーダンスを調整するトリミング回路2とを具備する。トリミング回路2は、第1電源VDDと出力端子対31、32との間に、メインバッファ回路1内の第1トランジスタ対MP1、MP2及び第1抵抗対R1、R2に対して並列に接続された少なくとも1つの第2トランジスタ対MP11、MP21を備える。

(もっと読む)

多値論理ドライバ

【課題】SLVSを多値化して、多値のCML及び2値のSLVSと比べ1ビット当りの消費電力を削減し、SLVSの多値化に際して生じる論理値の違いによる電源電流の変動を補償した多値論理ドライバを提供する。

【解決手段】第1、2の差動プッシュプル回路(DPP)は各々対応する第1、2の差動入力を受け、各々第1〜4のトランジスタ(Tr)を含み、第1、3のTrのドレーン(D)は電源に接続され、第2、4のTrのソース(S)は接地され、第1、3のTrのゲート(G)は正入力に接続され、第2、4のTrのGは補入力に接続され、第1のTrのSと第2のTrのD及び第3のTrのSと第4のTrのDは第1、2のDPPに亘り正・補各々コモン接続されて単一の差動出力を形成し、第1、2のDPPを構成する各4個のTrのオン時の抵抗値は差動出力に接続される伝送路の特性抵抗値Zoを単位として各々3/2、3に設定されている。

(もっと読む)

出力バッファ回路

【課題】駆動能力が切替可能であると共に、ESD耐性が高い出力バッファ回路。

【解決手段】出力バッファ回路100において、第1の電源電圧と、第1の電源電圧より低い第2の電源電圧との間に直列に接続された第1導電型トランジスタTRA1と第2導電型トランジスタTRB1は、出力トランジスタを構成する。制御回路110は、トランジスタTRA1とトランジスタTRB1を相補的にオン/オフさせ、かつトランジスタTRA1とトランジスタTRB1をオンさせるときに与えるゲート電圧を複数の値間で切替可能である。

(もっと読む)

半導体装置及びシステム

【課題】複数の入力回路の切り替え時において入力信号の内部への供給が遮断されないような半導体装置を提供する。

【解決手段】半導体装置は、第1電源電圧が供給される第1入力回路と、前記第1電源電圧よりも低い第2電源電圧が供給される第2入力回路と、第1のモードで前記第1入力回路を活性化させ、第2のモードで前記第2入力回路を活性化させる制御回路とを含み、前記制御回路は、前記第1のモードと前記第2のモードとの間の切り替え時において前記第1入力回路と前記第2入力回路とが同時に活性化する期間があるように前記第1入力回路と前記第2入力回路とを制御することを特徴とする。

(もっと読む)

出力バッファ回路、入出力バッファ回路及び半導体装置

【課題】出力レベルのスイッチング時に電源電位に発生され得るノイズを低減することのできる出力バッファ回路、入出力バッファ回路及び半導体装置を提供する。

【解決手段】駆動回路2aは、駆動能力が同一のトランジスタTP1,TN1を含む第1駆動部E1と、駆動能力が同一のトランジスタTP2,TN2を含む第2駆動部E2と、駆動能力が同一のトランジスタTP3,TN3を含む第3駆動部E3を備える。これら駆動部E1〜E3内のプルアップ側のトランジスタTP1,TP2,TP3同士の駆動能力及びプルダウン側のトランジスタTN1,TN2,TN3同士の駆動能力は互いに異なる。制御回路3aは、データ信号Aと、駆動能力制御信号B1,B2と、駆動能力選択信号DSとに応じて、駆動能力が異なるプルアップ側のトランジスタとプルダウン側のトランジスタとを相補的にオンさせる信号を生成する第1制御回路40を備える。

(もっと読む)

トレラントバッファ回路及びインターフェース

【課題】出力端子が出力回路の電源電圧より高電位である場合や、出力回路の電源電圧が0Vになっても出力端子から電源電圧へ電流の逆流入は発生しないトレラントバッファ回路及びインターフェースを提供すること。

【解決手段】トレラントバッファ回路100は、電源端子VDD1と出力端子102の間にソースを共有して直列接続されたPチャンネルMOSトランジスタQ111,Q112と、出力端子102と接地端子の間に接続されたNチャンネルMOSトランジスタQ113と、PチャンネルMOSトランジスタQ111のゲートに出力接続されたインバータ121と、PチャンネルMOSトランジスタQ112のゲートに出力接続されたインバータ122と、各MOSトランジスタQ111、Q112、Q113にそれぞれ第1、第2及び第3の制御信号を出力してこれらのMOSトランジスタのオン・オフを制御する制御回路130とを備える。

(もっと読む)

半導体集積回路装置

【課題】I/O処理性能の向上と消費電力の低減またはコストの低減が実現可能な半導体集積回路装置を提供する。

【解決手段】例えば、複数の半導体チップCHIP0〜CHIPnが積層搭載され、互いのデータ送受信端子P_DIOが貫通ビアTSVを介してバス接続された半導体集積回路装置を設け、CHIP0〜CHIPnの内部コア回路の電源電圧のうち最も低い電源電圧を用いてこのバスを介したデータ送受信を行わせる。これに伴い、この最も低い電源電圧となるCHIPnの電源電圧端子P_VDDnを、貫通ビアTSVを介して他の半導体チップCHIP0,CHIP1のデータ送受信回路用の電源電圧端子P_VDDL0,P_VDDL1に接続する。

(もっと読む)

送信回路

【課題】出力回路のトランジスタのばらつきに関わらず、出力信号のクロス電圧を安定化させ得るUSB送信回路を簡単な回路で提供する。

【解決手段】データDP,DMの入力に基づいてメインバッファ回路から出力信号FSDP,FSDMを出力する第一及び第二の出力回路11a,11bと、第一及び第二の出力回路から出力信号FSDP,FSDMを相補信号として出力することと、メインバッファ回路を構成する出力トランジスタの駆動電流のばらつきを補正する補正信号を生成する補正回路12a,12bと、メインバッファ回路に並列に接続され、補正信号に基づいてメインバッファ回路の出力トランジスタの電流駆動能力のばらつきを相殺するサブバッファ回路とを備えた。

(もっと読む)

伝送回路、CMOS半導体デバイス、及び設計方法

【課題】クロック信号の遅延量を低減する。

【解決手段】予め定められた最小パルス時間以上のパルス時間を有する差動信号を伝送する伝送回路であって、2本の伝送線の電位差として、差動信号を送出する駆動部102aと、2本の伝送線の電位差により差動信号を受け取ることにより、差動信号に基づいて動作する被駆動部102bと、2本の伝送線を電気的に接続する接続抵抗104とを備える。また、接続MOSトランジスタは、被駆動部の受信端の近傍に設けられてよい。

(もっと読む)

出力ドライバ回路

【課題】本発明の目的は、被駆動部の確実な駆動を維持しつつも、より高速に被駆動部を駆動することができる、出力信号を得ることができる、出力ドライバ回路を提供することにある。

【解決手段】本発明の一態様にかかる出力ドライバ回路は、入力信号が加えられる入力端子と、前記入力信号を受けてバッファ信号を出力する、第1電源から給電されて動作する、入力バッファと、前記バッファ信号を受けて出力信号を出力端子から出力する、第2電源から給電されて動作する、出力バッファと、前記出力バッファに、前記第2電源の電位が前記第1電源の電位と同等である第1状態時に、前記バッファ信号をそのまま前記出力バッファに加えさせる第1の動作と、前記第2電源の電位が前記第1電源の電位に比して高くなった第2状態時に、前記バッファ信号を前記第2電源の電位に対応するレベルまでレベルシフトしてレベルシフト済信号として前記出力バッファに加えさせる第2の動作とを、切り替えて行わせる、制御部と、を備える。

(もっと読む)

信号調節受信器回路網

【課題】通信経路から受信されるデジタル信号を調節するための技術を提供すること。

【解決手段】通信経路から受信される信号を調節するためのシステムおよび方法が開示される。受信器は、信号の周波数成分の少なくとも一部を減衰する通信経路から信号を受信できる。受信器は、受信される信号の周波数コンテンツの少なくとも一部を調節する等化ブロック、正規化された信号振幅および/または正規化されたエッジスロープを提供する信号正規化ブロック、および制御ブロックを含み得る。一実施形態においては、制御ブロックは、高周波数に対する等化ブロックにおける周波数調節を制御するが、低周波数に対しては制御しない。低周波数調節に対して、制御ブロックは、信号正規化ブロック内の正規化された信号振幅を制御する。このようにして、低周波数コンテンツに対する制御された調節は、信号正規化ブロックにおいて実行される。

(もっと読む)

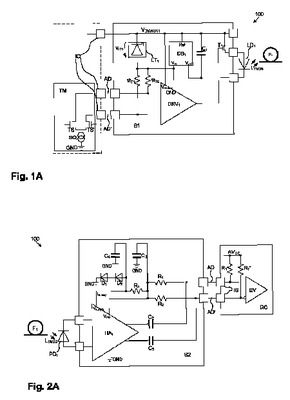

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

差動出力回路

【課題】複数の異なる差動小振幅インターフェイス規格に対応しながらも回路面積の増大を抑えた差動出力回路を提供する。

【解決手段】差動出力回路は、直列接続された第1のPMOSトランジスタと第1のNMOSトランジスタとを有する第1の出力駆動回路と、直列接続された第2のPMOSトランジスタと第2のNMOSトランジスタとを有する第2の出力駆動回路と、制御信号が第1の値の場合に第1及び第2のPMOSトランジスタの一方を選択的に導通状態とし且つ第1及び第2のNMOSトランジスタの一方を選択的に導通状態とし、制御信号が第2の値の場合に第1及び第2のPMOSトランジスタの何れにも電流を流さず且つ第1及び第2のNMOSトランジスタの一方を選択的に導通状態とすることにより、第1及び第2の出力駆動回路から一対の差動信号を出力させる制御回路とを含む。

(もっと読む)

出力バッファ回路及び出力バッファシステム

【課題】出力回路のスイッチング素子の短絡による破壊を確実に防止することが可能な出力バッファ回路及びそれを複数備えた出力バッファシステムを提供する。

【解決手段】第1の上側スイッチング素子4の他方の主端子と第1の下側スイッチング素子5の一方の主端子とを接続する部分が外部への出力部6を構成する第1の出力回路2と、出力端子が第1の出力回路2の出力部6に接続された第2の出力回路22と、第1の出力回路2の出力部6の短絡を検出する短絡検出回路24と、を備え、その起動時に、第1の出力回路2を動作させる前に第2の出力回路22を動作させて短絡検出回路24を動作させ、出力部6の短絡が検出されなかった場合に第1の出力回路2を動作させ、出力部6の短絡が検出された場合には第1の出力回路2を動作させないよう構成されている。

(もっと読む)

液晶表示装置

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

CMOSレベルシフタ回路デザイン

レベルシフティング回路(402)は、アシスト回路のペア(404、406)を含んでいる。レベルシフティング回路(402)は、入力ポイント(420)と、2つの出力ポイント(416、418)と、出力ポイント(416、418)に結合されたクロス結合ペアPMOSトランジスタ(412、414)と、入力及び出力ポイント(420)間に結合されたNMOSトランジスタのペアを含んでいる。各アシスト回路(404、406)は、PMOSトランジスタのペアを含み、一方(424、432)は入力ポイント(420)に印加された入力に応答し、他方(426、434)は一方のNMOSトランジスタ(408、410)のドレイン電圧に応答する。アシスト回路(404、406)は、入力がロウからハイに変化、或いはハイからロウに変化したとき、クロス結合ペアPMOSトランジスタ(412、414)を一時的に弱くする。  (もっと読む)

(もっと読む)

出力回路

【課題】より精度よく外部インピーダンスとの整合をとることができる半導体集積回路の出力回路を提供する。

【解決手段】出力回路は、トランジスタN00〜N7を含むトランジスタ回路が出力端子3に複数段並列に接続されてなり、各トランジスタ回路に含まれるトランジスタのゲートへの入力信号G0〜G7により出力インピーダンスの調整が可能な出力回路であって、複数段のトランジスタ回路に含まれる、少なくとも2段のトランジスタ回路のインピーダンスを互いに異ならせる。

(もっと読む)

半導体装置

【課題】レベルシフトを行う場合に、低電圧で動作するトランジスタが使用可能であり、そのトランジスタがオンオフ動作する際の出力変化速度(動作速度)の向上を半導体チップ内の少ない占有面積で容易に実現可能な半導体装置の提供。

【解決手段】レベルシフト部5は、MOSトランジスタN2と、抵抗R2と、抵抗R1とを備え、これらが直列接続されている。抵抗R1には、ツェナーダイオードZD1が並列接続されている。ツェナーダイオードZD1は、MOSトランジスタN2がオフからオンになるときに、レベルシフト部5の出力電圧LOを所定値にクランプする。MOSトランジスタN2のドレインとソースとの間には、ツェナーダイオードZD2が並列接続されている。ツェナーダイオードZD2は、MOSトランジスタN2がオフのときに、MOSトランジスタN2のドレインとソースとの間の電圧を所定値にクランプする。

(もっと読む)

81 - 100 / 232

[ Back to top ]