Fターム[5J056EE08]の内容

Fターム[5J056EE08]に分類される特許

41 - 60 / 232

レベルシフト回路

【課題】変換する電位差が大きくても、小規模な回路で、高速に、低電圧から高電圧へ信号レベルを変換することのできるレベルシフト回路を提供する。

【解決手段】低電圧電源電圧VDDLで動作する低電圧部100からは、入力信号Sinと同相の同相信号Sおよび逆相の逆相信号SNが出力され、能動バイアス制御部1は、入力された逆相信号SNの信号レベルに応じて、出力するバイアス信号VMの電位を、高電圧電源電圧VDDHに近い電位、または接地電位GNDに近い電位に、能動的に制御し、出力部2は、高電圧電源線VDDHと反転出力端VQとの間の導通が同相信号Sおよびバイアス信号VMにより制御され、接地電位電源線GNDと反転出力端VQとの間の導通が同相信号Sにより制御され、反転出力端VQの信号の極性がインバータINV1により反転される。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】断熱的回路動作と非断熱的回路動作を切り替え可能である回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、論理回路200と、電源回路100と、を含む。第1のモードでは、電源回路100は、非直流の電源電圧VPK、VMKを論理回路200に供給し、論理回路200は、その非直流の電源電圧VPK、VMKが供給されることで断熱的回路動作を行う。第2のモードでは、電源回路100は、直流の電源電圧VDD、VSSを論理回路200に供給し、論理回路200は、その直流の電源電圧VDD、VSSが供給されることで非断熱的回路動作を行う。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

データ出力回路

【課題】プリエンファシスまたはディエンファシスのためのドライバの追加がなくても、プリエンファシスまたはディエンファシス動作を行えるデータ出力回路を提供すること。

【解決手段】インピーダンスコードによって各々オン・オフされ、出力ノードにデータを出力する複数の駆動手段311、312を備え、前記インピーダンスコードが、前記駆動手段をターンオンさせる値を有する第1のグループと前記駆動手段をオフさせる値を有する第2のグループとに分けられ、プリエンファシス期間の間には、前記第2のグループによる制御を受ける駆動手段の全部または一部がターンオンされる。

(もっと読む)

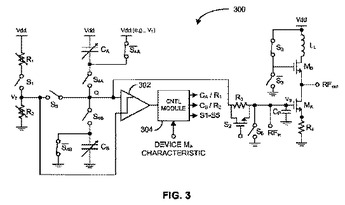

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】デジタル回路とアナログ回路とを混載して成る半導体集積回路において、前記デジタル回路によってメモリなどの外部負荷を駆動するにあたって、グランドバウンスによるアナログ回路への影響を抑えつつ、前記外部負荷がデジタル回路からの矩形波パルスを受信するにあたって、ON/OFF(「1」/「0」)判定のマージンを最大にする。

【解決手段】外部負荷3を駆動するメインドライバ回路7を、複数段のインバータINV1〜INV3を備える多段階電圧制御型のプリドライバ回路6を介して駆動するようにし、そのインバータINV1〜INV3の使用段数を切換え回路12で切換えられるようにする。そして、雑音検出回路13によって検出されるグランドバウンスのレベルが、小さいときにはインバータINV3のみを使用して前記矩形波パルスの鈍りを小さくし、大きいときにはインバータINV1〜INV3を使用して、グランドバウンスを抑える。

(もっと読む)

半導体装置

【課題】スイング領域を変換せずに、CML領域でスイングする信号の電源電圧レベルをシフトすることができる回路を提供する。

【解決手段】第1の電源電圧VDD1を電源として用い、第1のレベルを基準としてスイングするCMLクロックCML_TRANS_Pを受信して、そのスイング基準レベルを第2のレベルに切り換えて降圧CMLクロックCML_TRANS_Lとして出力するスイングレベル切換部220と、第2の電源電圧VDD2を電源として用い、スイングレベル切換部220から伝達される降圧CMLクロックCML_TRANS_LをバッファリングするCMLクロック伝達バッファリング部240と、第1の電源電圧VDD1を電源として用い、ソースクロックCML_INをバッファリングして、CMLクロックCML_TRANS_Pを生成した後、スイングレベル切換部220に提供するCMLクロック生成バッファリング部200とを備える。

(もっと読む)

検知システム並びにそれを用いた半導体装置および情報処理装置

【課題】 低電力モードを有するLSIにおいて、低電力モードで電力が低減されていない場合にも、LSIを搭載する機器が性能劣化等に至るのを防止することが可能なLSIを提供する。

【解決手段】 動作モードを指示し、そのモードの通りに動作しているかを検出する回路であって、低電力モード時の電流を擬似的に測定し、低電力モードに移行したにもかかわらず実際には電流が低減されていない場合に警告信号を発する。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】低コストで実現でき、小型化、低消費電力化及び高周波化に資するとともに、フリップフロップ回路の誤動作を防止するレベルシフト回路及びレベルシフト回路を用いたスイッチング電源装置を提供する。

【解決手段】それぞれ一端がレベルシフト電源に接続された抵抗R1、R2と、抵抗R1の他端にドレインが接続されたトランジスタMN3と、抵抗R2の他端にドレインが接続されたトランジスタMN4と、入力信号に基づいてトランジスタMN3,MN4のオン/オフを制御するパルス発生回路10と、トランジスタMN3がオンである場合にセット信号、トランジスタMN4がオンである場合にリセット信号を生成する制御部と、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12とを備える。

(もっと読む)

半導体集積回路

【課題】ゲートリークによる消費電力の増大を抑制し、電源[VDD]−[GND]間のノイズを低減すること。

【解決手段】本発明の半導体集積回路は、機能ブロックと領域部3bとを具備している。機能ブロックは、電源[VDD]−[GND]間に設けられ、常に動作する。領域部3bにおいて、周辺機能ブロック4は、信号線9と電源[GND]との間に設けられ、動作モード又は非動作モードを実行する。電源スイッチMPは、電源[VDD]と信号線9との間に設けられ、動作モードにおいて電圧VDDを信号線9に供給し、非動作モードにおいて信号線9への電圧VDDの供給を遮断する。MOSトランジスタは、周辺機能ブロック4に設けられ、そのバックゲートに電源[VDD]と電源[GND]との一方の電源が接続されていて、非動作モードにおいて、そのゲートに他方の電源が接続され、そのゲートとバックゲート間に寄生容量を発生する。

(もっと読む)

半導体集積回路および半導体集積回路のテスト方法

【課題】内部電源ノイズを正確に測定を行える半導体集積回路の提供。

【解決手段】TEST信号を出力するテスト制御回路101と、テストモード対応バッファ回路111と、通常出力バッファ回路113とを具備する。テストモード対応バッファ回路111は、TEST信号としてテストモードを示す第1TEST信号を受け取ると、第1TEST信号を受けている間、第1端子121を介して内部の電源電圧又は接地電圧に固定された第1出力信号を出力し、TEST信号として通常モードを示す第2TEST信号を受け取ると、通常動作の入力バッファとして外部信号を受け取る、又は、通常動作の出力バッファとして第2出力信号を出力する。通常出力バッファ回路113は、テストモード対応バッファ回路111がTEST信号に基づいて動作する間、第2端子123を介して通常動作の出力バッファとして第3出力信号を出力する。

(もっと読む)

信号入出力回路

【課題】従来、データ受信するとき、データを判別する為、大小判定を行うコンパレータを備えており、このコンパレータには、動作時、入力信号の変化に追従するため、定常的に電流が流れている。このコンパレータに流れる定常的な電流が、大きな電力を消費しているという問題があった。

【解決手段】本発明は、一方のレベルを検知する第1検出回路と、他方のレベルを検知する第2検出回路とを有する受信部と、前記一方のレベルを出力するか、前記他方のレベルを出力するか、信号線から電気的に切り離したハイインピーダンス状態とするか、3つのうち何れかを1つの値を出力する三値出力器と有する送信部と、前記受信部と前記送信部を制御する制御回路と、を備え、前記制御回路は、受信の状態では、前記第1検出回路及び前記第2検出回路からの検知結果に応じて、入力される信号のレベルを判断し、送信の状態では、前記三値出力器からの出力値を制御することを特徴とする

(もっと読む)

半導体装置、及びその制御方法

【課題】発振回路と信号入出力回路とを切り替えて使用可能な半導体装置、及びその制御方法を提供することである。

【解決手段】本発明にかかる半導体装置は、発振素子1が接続可能な第1及び第2の外部接続端子2、3と、反転増幅器4と、反転増幅器の出力側と入力側との間に接続されたフィードバック抵抗5と、反転増幅器4の入力側に接続されたカップリング容量11に印加されるバイアスを安定化するバイアス安定化回路6と、第1の信号入出力部7と、第2の信号入出力部8と、を備える。半導体装置を発振回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を動作状態とし、第1及び第2の信号入出力部7、8を停止状態とする。信号入出力回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を停止状態とし、第1及び第2の信号入出力部7、8を動作状態とする。

(もっと読む)

半導体装置

【課題】通常動作モードとテスト動作モードの切換に使用した兼用外部端子をテスト動作モード時のモニター端子としても使用できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、通常動作モードとテスト動作モードを切り換える切換回路と、前記通常動作モード時と前記テスト動作モード時で兼用する2つ以上の兼用外部端子とを備える半導体装置であり、前記切換回路は、前記兼用外部端子にて前記半導体装置で通常使用する入出力電圧の範囲外の電圧の印加を検出する検出回路と、全ての前記兼用外部端子に同時に前記入出力電圧の範囲外の電圧の印加が検出された場合テスト開始信号を出力する論理回路と、前記テスト開始信号をラッチする記憶回路とを含み、前記テスト動作モードに切り換わった後、前記兼用外部端子の内、1つの兼用外部端子に前記入出力電圧の範囲外の電圧が印加し続けられていることでテスト動作モードが維持される。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、データの送受信を精度良く行うことができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、双方向用信号線を介してデータの送受信が行われるSoC回路100及びSDRAM回路101を備え、SoC回路100は、電源と双方向用信号線との間に設けられた抵抗207,208と、抵抗207,208に流れる電流のオンオフを制御するスイッチ209,210と、を有するターミネーション回路204と、データ受信時にはスイッチ209,210をオンし、データ送信時にはスイッチ209,210をオフし、データ受信後にさらに別のデータを受信する場合には、先のデータ受信後から所定の期間スイッチ209,210をオンし続けるように、ターミネーション回路204に対して制御信号200を出力する制御回路205と、を備える。

(もっと読む)

半導体装置

【課題】高速の半導体装置で要求されるクロック整列トレーニング動作を提供すること。

【解決手段】システムクロック及びデータクロックを入力されるクロック入力部(200)と、データクロックの周波数を分周して所定の位相差を有する複数の多重位相データ分周クロックを生成し、分周制御信号に応答して多重位相データ分周クロックの位相の反転可否を決定するクロック分周部(220)と、多重位相データ分周クロックのうち所定の第1選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応して分周制御信号のレベルを決定する第1位相検出部(240)と、多重位相データ分周クロックのうち所定の第2選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応してトレーニング情報信号を生成する第2位相検出部(260)と、トレーニング情報信号を外部に伝送するための信号伝送部(270)とを具備する。

(もっと読む)

出力ドライバ、出力ドライバを含むメモリ、メモリコントローラ及びメモリシステム

【課題】プリアンブルに続く最初のハイレベル又はローレベルの区間の長さを、その後のクロッキング部分のハイレベル又はローレベルの区間の長さに一致させる。

【解決手段】 出力ドライバは、第1の電源と出力端子との間に接続される第1のドライバと、第2の電源と出力端子との間に接続される第2のドライバとを有する。第1のドライバ及び第2のドライバの一方は、互いに並列接続された2つの駆動部を備える。これら2つの駆動部の各々と、第1のドライバ及び第2のドライバの他方とは、それぞれ独立した入力信号に応じて動作する。

(もっと読む)

41 - 60 / 232

[ Back to top ]