Fターム[5J056EE08]の内容

Fターム[5J056EE08]に分類される特許

21 - 40 / 232

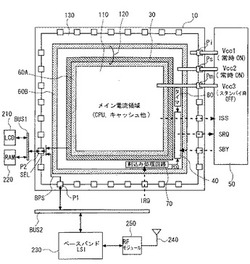

携帯電話

【課題】回路の誤動作や回路面積の増加を防止しつつ一部の回路の電源電圧を

遮断して消費電力を低減させることができる半導体集積回路を提供する。

【解決手段】チップ内部を複数の回路ブロック(11,12,13……)に分

割するとともに、いずれかの回路ブロックへの電源電圧の供給を遮断可能に構成

し、電源電圧の供給を遮断可能な回路ブロックから他の回路ブロックへ出力され

る信号の経路上であって信号が分岐される前の位置に、信号の伝達を遮断可能な

信号ゲート手段(31)と電源遮断直前の信号を記憶可能な記憶手段(32)と

を含むブロック間インタフェース回路(30)を設けるようにした。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

切替回路及び受信回路

【課題】2つのクロック信号を切り替えて出力する切替回路において、出力信号のデューティ比を、入力されるクロック信号のデューティ比に保つこと。

【解決手段】切替回路100は、制御信号CONTに応じて、入力信号IN1,IN2を切り替えて出力信号OUTとして出力する。具体的には、制御信号CONTが「Lレベル」のときには、クロックドインバーターX2が動作し、信号IN1が信号OUTとして出力され、制御信号CONTが「Hレベル」のときには、クロックドインバーターX4が動作し、信号IN2が信号OUTとして出力される。

(もっと読む)

通信信号生成装置及び通信装置

【課題】集積回路の実装面積を抑えつつ通信信号の通信波形のリンギングを抑制する。

【解決手段】トランスミッタ130において、出力バッファ制御信号生成部131は、トランジスタ132a〜132d,133a〜133dをすべてオンにして第1通信線11及び第2通信線12に電流を流すことによりドミナントを表す通信信号を生成し、トランジスタ132a〜132d,133a〜133dをすべてオフにして第1通信線11及び第2通信線12に電流を流さないことによりレセッシブを表す通信信号を生成する。そして、出力バッファ制御信号生成部131は、ドミナントを表す通信信号の1ビット時間において、トランジスタ132a〜132d,133a〜133dを順にオフにして出力バッファ(第1のトランジスタ群132及び第2のトランジスタ群133)の各インピーダンスを徐々に高くする。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

入出力回路、半導体制御システム、および入出力回路の制御方法

【課題】デジタル信号を高速で送受信するための入出力回路を、EM耐性を保ちつつ、小さな回路面積で、実現する。

【解決手段】出力バッファ21は、電源−グランド間に接続されたトランジスタTP1,TN1と、ノードn1と入出力端子23との間に接続された抵抗素子R1とを備え、出力バッファ22は、電源−グランド間に接続されたトランジスタTP2,TN2と、ノードn2と入出力端子23との間に接続された抵抗素子R2とを備えている。信号入力モードにおいて、出力バッファ21,22によって1つの終端回路を構成する。例えば、トランジスタTP1,TN2をON、トランジスタTN1,TP2をOFFにし、抵抗素子R1,R2を通る電流パスを形成する。

(もっと読む)

バッファ回路およびそれを用いた半導体装置、出力回路および電子機器

【課題】高速信号を確実に伝送可能なバッファ回路を提供する。

【解決手段】電流源312は、定電流Icを生成する。第1トランジスタM1は、その一端が電流源312と接続され、その制御端子に入力信号SINが入力される。反転回路314は、入力信号SINを反転および遅延させ、反転入力信号SIN#を生成する。第2トランジスタM2は、その一端が電流源312と接続され、その制御端子に反転入力信号SIN#が入力される。バッファ回路310は、第1トランジスタM1および第2トランジスタM2の、電流源312と共通に接続された一端に生ずる信号SOUTを出力する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、トランジスタの閾値電圧のばらつきに起因する出力電圧のばらつきを抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】6Tr3Cで構成されるインバータ回路において、入力端子IN2に、入力端子IN1に入力されるパルス信号の位相よりも進んだ位相のパルス信号が印加される。これにより、入力端子IN1の電圧がハイからローに変化する際に、トランジスタT5のゲート−ソース間電圧から、トランジスタT5の閾値電圧の影響が取り除かれるので、その後にトランジスタT5がオンしてトランジスタT5に電流が流れたときに、その電流値Idsからも、トランジスタT5の閾値電圧の影響が取り除かれる。

(もっと読む)

スイッチタイミング制御回路及び半導体装置

【課題】回路規模を大きくせずに複数のスイッチを貫通電流が流れないように確実に導通非導通のタイミングを制御するスイッチタイミング制御回路を提供する。

【解決手段】複数のデータフリップフロップが縦続接続され、縦続接続されたデータフリップフロップには共通のクロック信号が接続され、それぞれ前段のデータ出力信号が後段のデータ入力信号として接続され、初段のデータ入力信号には、最終段のデータ出力信号の論理が反転されて接続された分周回路と、複数のデータフリップフロップのうちそれぞれ複数の異なるデータフリップフロップの出力信号が入力端子に接続された複数の組み合わせ論理回路と、複数の組み合わせ論理回路の出力信号によりそれぞれ導通、非導通が制御される複数のスイッチと、を備える。

(もっと読む)

レベルシフト回路及びデータドライバ及び表示装置

【課題】低振幅のデジタル入力信号を高振幅の電圧信号に高速にレベル変換可能としレベル変換信号の安定な保持を可能とし、構成を簡易化する。

【解決手段】第1のトランジスタM1のゲートと、第2及び第3のトランジスタM2、M3の一方のトランジスタのゲートには、第1の制御信号S1が共通に入力され、第2及び第3のトランジスタM2、M3の他方のトランジスタのゲートには、第1の電源と第2の電源の電源振幅よりも低振幅の入力信号INが入力される入力端子1に接続される。第2の制御信号S2によりオン又はオフに制御されるクロックドインバータ10と、第1の出力端子3に入力が接続されたインバータ20と、第1のノード2とインバータ20の出力との間に接続され、第3の制御信号S3によりオン又はオフに制御されるスイッチSW1を備えている。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

ソースドライバ及び液晶表示装置

【課題】液晶表示パネルを駆動するソースドライバのソースアンプの振幅差偏差を向上する。

【解決手段】液晶表示パネルを駆動するソースドライバ100が、画素データDINに対応する階調電圧を出力するD/Aコンバータ23と、階調電圧に対応する駆動電圧を出力するソースアンプ25とを備えている。ソースアンプ25は、第1及び第2NMOSトランジスタMN11,MN12を含むNMOS差動対と、第1及び第2PMOSトランジスタMP11,MP12を含むPMOS差動対と、NMOS差動対とPMOS差動対に流れる電流に応じて駆動電圧を出力する出力回路部(2,3)と、第1及び第2入力レベル変換回路4、5とを備えている。第1及び第2入力レベル変換回路4、5は、ソースアンプ25に入力される階調電圧と、ソースアンプ25の入力にフィードバックされる駆動電圧とに対し、駆動電圧の極性及び/又は階調電圧に応じて入力レベル変換を行う。

(もっと読む)

半導体メモリのデータ出力回路及びその制御方法

【課題】カップリングノイズを減少させることができる半導体メモリのデータ出力回路およびその制御方法を提供すること。

【解決手段】複数のグローバルラインと、複数のデータを互いに異なるタイミングで複数のグローバルラインに出力するように構成されたセンスアンプブロックと、複数のグローバルラインを介して伝送された複数のデータを互いに異なるタイミングでラッチするように構成されたパイプラッチブロックと、アドレス信号を用いてセンスアンプブロックの出力タイミングとパイプラッチブロックのラッチタイミングとを制御するように構成された制御部とを備えることを特徴とする。

(もっと読む)

半導体集積装置、及びその調整方法、並びに終端抵抗調整回路

【課題】第1の伝送路及び第2の伝送路間のDuty比の高精度化を実現できる終端抵抗調整回路、及び半導体集積回路を提供する。

【解決手段】本発明に係る終端抵抗調整回路71は、差動入力信号の第1及び第2の伝送路21、22それぞれに挿入され、制御信号に応じて抵抗値が調整される終端抵抗郡1,2と、第1及び第2の伝送路21、22の内、少なくともいずれかの伝送路であって、終端抵抗郡1,2の後段に挿入され、終端抵抗郡1、2を介して接続する伝送路の電位の調整を行う可変抵抗郡3と、可変抵抗郡3の後段、若しくは、当該可変抵抗郡3が配設されていない場合には終端抵抗郡1,2の後段に挿入され、第1及び第2の伝送路21、22の電位差を比較する比較器4と、比較結果に基づいて可変抵抗郡3の抵抗値を制御することによって伝送路の電位を調整する伝送路電位調整部5と、を備える。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

電源変動緩和回路を有する集積回路

【課題】

内部回路の一部の回路が起動または停止したときに内部電源電圧の変動が緩和されるようにした集積回路を提供する。

【解決手段】

電源が供給される集積回路において,電源が供給され内部電源を内部に供給する電源配線と,内部電源を供給される第1及び第2の内部回路と,第2の内部回路を非動作状態から動作状態に制御するイネーブル信号を第2の内部回路に供給するイネーブル信号供給回路とを有し,イネーブル信号供給回路は,イネーブル信号が非動作状態から動作状態に変化したときに動作状態の期間を間欠的に発生する調整イネーブル信号を生成し第2の内部回路に供給する。

(もっと読む)

21 - 40 / 232

[ Back to top ]